文章目录

一、问题描述

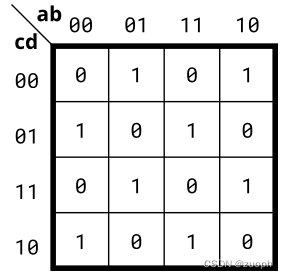

实现下面卡诺图描述的电路。

模块声明

module top_module(

input a,

input b,

input c,

input d,

output out );

endmodule

思路:

本题不能化简,直接写出格中为1的项。

a’bc’d’+ab’c’d’+a’b’c’d+abc’d+a’bcd+ab’cd+a’b’cd’+abcd’

=(a’bc’d’+ab’c’d’)+(a’b’c’d+abc’d)+(a’bcd+ab’cd)+(a’b’cd’+abcd’)= (a^b)c’d’ + (~a ^ b)c’d + (a ^ b)cd + ( ~a ^ b)cd’

= (a ^ b)(~c ^d) + ( ~a ^ b)( c ^ d)

= (a ^ b) ^ (c ^ d)

二、verilog源码

module top_module(

input a

订阅专栏 解锁全文

订阅专栏 解锁全文

111

111

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?