set_ideal_network 只是将net上的transition和delay默认设置为0,fix timing的时候是不会动到这个net的。但是我们还会设置max_fanout

它不管你是不是ideal的,只要扇出足够大他就会去优化。所以必须要给高扇出的net设置dont_touch属性。

=========================================

附上4个实践结果:

1。 只执行set_dont_touch_network , 而不执行set_ideal_network.

这种情况下,阻止不了DC往high_fanout的地方长buffer_tree.

2。 当约束文件中,没执行set_driving_cell 命令, 这种情况下: DC不会对复位脚长buffer_tree.

当约束文件中,有执行set_driving_cell命令后,这种情况下:

对于high_fanout的net, DC会不会插入buffer_tree,由这根high_fanout的net, 是否具有ideal_net属性来决定。

可以通过命令 get_attribute [get_nets XXX] ideal_net 来查看。

或者 report_ideal_network -net 来查看

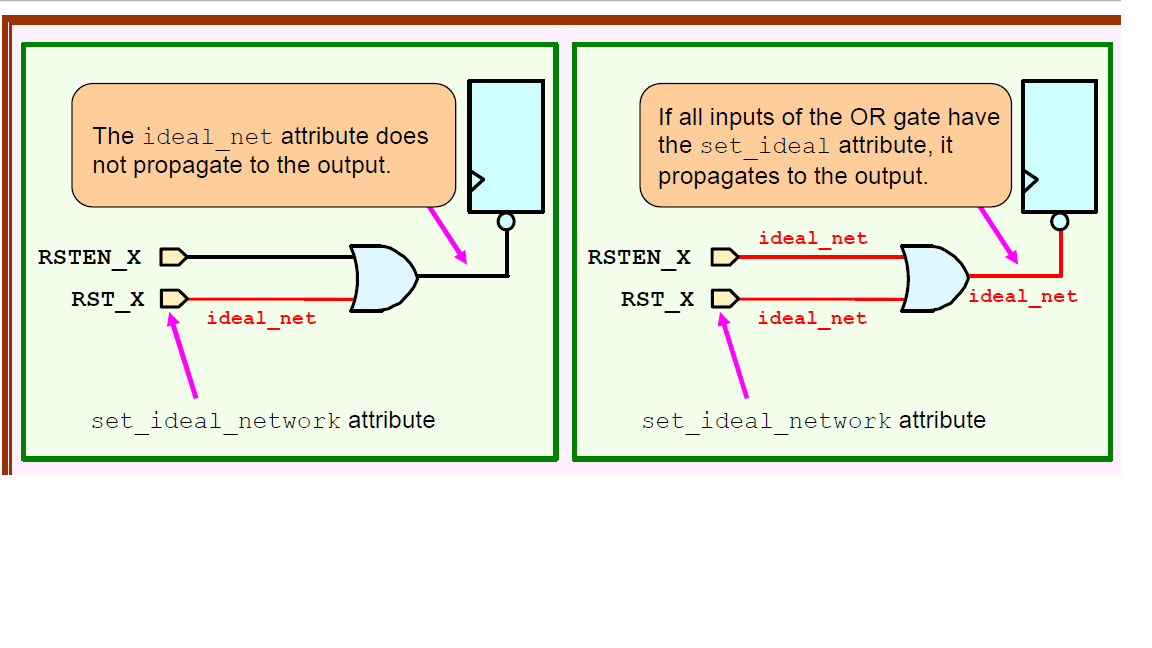

3。具有ideal_net属性的线,在经过与门,或门后,不能往下级传播(如左图所示)。 除非这个cell的所有输入都具有 ideal_net属性,才能住下级传播(如右图所示)。

4. DC会自动为create_clock命令创建的port pin ,所对应连接的net, 赋与ideal_net属性。 所以,DC默认不会为时钟树长buffer_tree.

=========================================

在综合的过程中,为了不让DC工具自动优化一些我们不希望其优化的模块(比如CLK)我们通常都会设置set_ideal_network和set_dont_touch,我理解为前者在timing_report的时候忽略延迟,后者阻止DC插入buffer。

那么dont_touch的属性,能不能穿过logic?

set_dont_touch和set_dont_touch_network有什么区别,为什么普遍认为set_dont_touch_network会造成未知问题而不推荐使用?

对于ideal_net的这个属性,是不是说直接忽略了延迟,忽略了DRC,如果将clk设定为ideal_net,是不是就不用再设定dont_touch了?

说的有点混乱,请各位大神技术支持,小弟不胜感激!!

~~~~~~~~~~~~

set_dont_touch不会穿过logic,可以用于cells, nets, references, 和 designs。你不希望DC碰的地方,都可以用它。

set_dont_touch_network可以穿过logic,可以用于clocks, pins, 或 ports,比上面的范围小。当你对设计不十分熟悉时,这个属性可能会传到你不希望的地方去。

ideal_net 顾名思义就是把这条net完全理想化--无穷大的驱动能力,没有延迟。有时会和上面的命令一起用。当你知道了它们的意思,如何使用取决于你的目的和得到的结果

~~~~~~~~~~~~

对于Ideal_net这个属性,设置的时候有个no_propagate的属性,对于net来说一定要设这个,是不是就是为了阻止其穿过逻辑?那如果我设的是pin并且不加上no_propagate能穿过逻辑吗?

在建立clock的时候,我看到它会自动的设为ideal_net,但是却还是会计算延迟,会不会因为clock path有逻辑的原因?

~~~~~~~~~~~~

| set_ideal_net = set_ideal_network -no_propagate clock net 如果被用作data,就会有delay,那是因为net上面挂的clk pin的负载,不是ideal net本身 |

~~~~~~~~~~~~

我大体上明白了,clk在创建的时候,会默认为ideal net的,但当clk接入到data path的时候,D端就会考虑我clk上的负载,但并不会影响clk的ideal net的属性。

假如我的clk需要门电路做gating,gating后的时钟也有很大的扇出,那我为了忽略掉延迟,是不是需要在gating后重新给clk定义ideal net?因为ideal net不能穿过逻辑。

~~~~~~~~~~~~

| 如果你的CG集成好的标准单元,它会自动继承ideal的属性 |

~~~~~~~~~~~~

问题1: set_ideal_network :当object是一个net的时候,必须加上-no_propagate选项,不然dc会ignore该命令,是不是说用set_ideal_network 声明ideal net时候,dc不让attribute 传递,为什么要这么要求?set_ideal_net被抛弃?

问题2:

在什么场景下需要使用set_ideal_network net_name -no_propagate 场景1.当gate logic cell中的latch的output与ideal clock做与的时候,与门的output 不会是ideal,如果需要output 为ideal,需要强制的设定latch output net为ideal。

还有其他的场景吗?

问题3:

set_ideal_network和set_dont_touch_network在什么场景下需要配合使用; 场景1:set_ideal_network,对design 内部soft reset network声明ideal network的时候,由于reset net被一个组合逻辑驱动,无法找到相关的pin,只好声明reset_net为ideal network,但是这样的话要使用set_ideal_network -nopropagate,导致ideal attribute无法spread,这时候只能使用set_dont_touch_network将reset_net声明为dont touch ,但是整个reset network没有完全声明为ideal,没有声明为reset network的部分还会做timing check&drc,甚至报violation,这种场景存在吗?该如何解决啊

=========================================

#-----clock------

create_clock -name $clock_name -period [expr $clk_period] [get_ports $clock_name]

#设置时钟

set_clock_uncertainty -setup $clk_uncertainty_setup [get_clocks $clock_name]

#设置时钟不确定性

set_clock_latency $clk_latency [get_clocks $clock_name]

#设置时钟延迟

set_dont_touch_network [get_clocks $clock_name]

#在优化过程中对时钟网络不进行改变和替换,原因:由于时钟端口的负载很大,DC 会使用 Buffer 来增加其驱动能力。但一般设计者都使用布局布线工具来完成此项工作,所以有必要指示 DC 不要对时钟网络进行修改,可以选中上图中“Don’t touch network”进行设置。

set_dont_touch_network [get_ports $reset_name]

#在优化过程中对复位信号不进行改变和替换

set_ideal_network [get_ports $reset_name]

#对reset设置成理想线网,因为reset的fanout太大,一般布图前都设置成理想线网,具体原因有待研究#

————————————————

版权声明:本文为CSDN博主「木子木杉」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_38407219/article/details/89448667

本文详细解析了在数字电路设计中理想网络(set_ideal_network)与勿触(set_dont_touch)属性的应用技巧,包括如何正确配置这些属性以避免不必要的优化,并探讨了它们在时钟信号和其他关键路径中的作用。

本文详细解析了在数字电路设计中理想网络(set_ideal_network)与勿触(set_dont_touch)属性的应用技巧,包括如何正确配置这些属性以避免不必要的优化,并探讨了它们在时钟信号和其他关键路径中的作用。

1191

1191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?