目录

一、前言

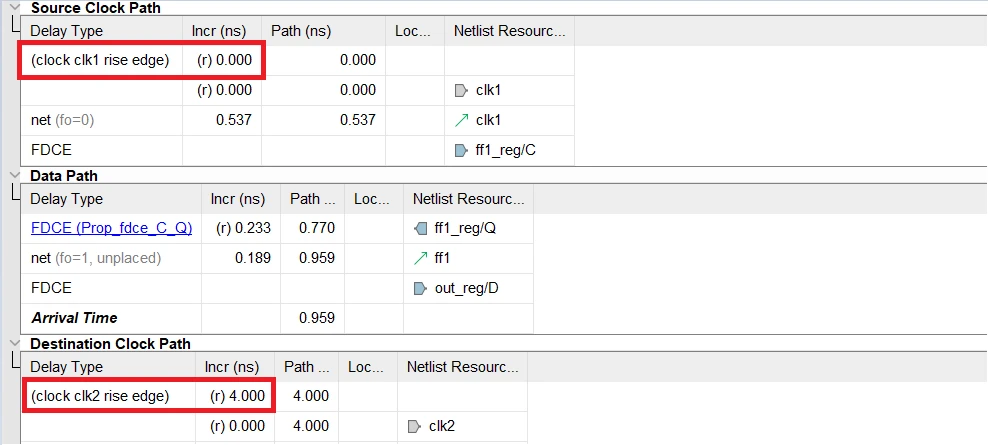

在对时序报告进行详细查看时,将看到source clock path或destination clock path的第一段延时都是时钟的edge,并且同一段路径的setup和hold也是不一样的,如下图的红色框内容为setup的示例,关于它的值在时序分析中是如何确定的呢?下面将对此进行详细的解答。

二、Clock edge的选取逻辑

首先,还是先看时序分析中setup、hold的定义。通常说setup、hold本质上是对同一个单元(时序单元,如触发器)上两个输入信号到达时间关系的检查,通常是检查数据信号/复位信号与时钟信号的到达先后关系。如果是数据信号与时钟信号,则是setup/hold分析,如果是复位信号与时钟信号,则是recovery/removal检查。

在用户手册UG906中,setup是对两个时钟延时关系进行最悲观的边沿检查,对时钟的边沿检查默认是发起时钟和捕获时钟边沿间的最小的正delta。 hold检查是确保启动边沿发送数据后,不能够被前一个setup捕获沿捕获。在实际的路径分析中,除了时钟的时延,还需考虑数据传输的时延,就是在报告中看到的完整时序路径。

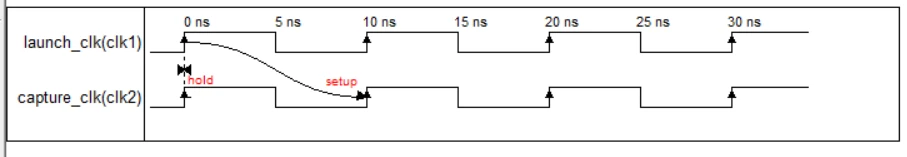

上面解释了分析时如何选取发起时钟launch clock和捕获时钟capture clock的边沿,即setup为正的边沿差值,hold尽量为负的差值,下面将结合实际例子来说明,根据发起始终与捕获时钟的频率与相位关系进行分类。

2.1 设计工程

工程很简单,就是最基础的时序路径,由两个触发器构成

module clk_edge(clk1,clk2,d,rst,out);

input clk1,clk2,d,rst;

output out;

reg ff1,out;

always@(posedge clk1,negedge rst)

if(!rst)

ff1<=0;

else begin

ff1<=d;

end

always@(posedge clk2,negedge rst)

if(!rst)

out<=0;

else begin

out<=ff1;

end

endmodule2.2 同频同相

时钟约束,clk1,clk2都是周期为10ns,占空比50%,在0-5ns为高电平

create_clock -period 10.000 -name clk1 -waveform {0.000 5.000} -add [get_ports clk1]

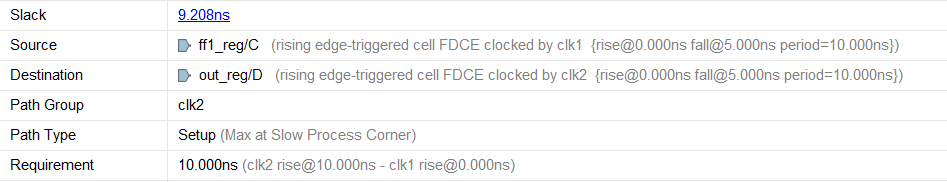

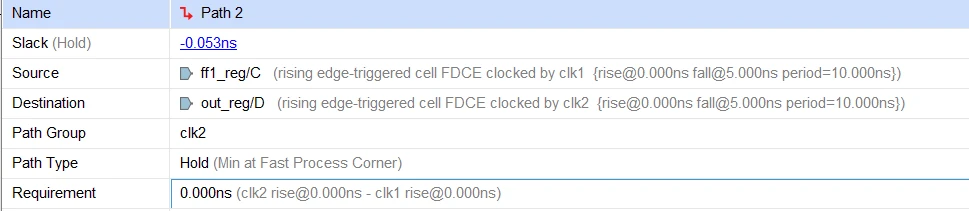

create_clock -period 10.000 -name clk2 -waveform {0.000 5.000} -add [get_ports clk2]因同频同相,每个周期内的相位关系都是确定的,在一个周期内分析即可,setup边沿的获取根据上述规则选取如下图,hold直接取0时刻的。

setup分析,requirement为10ns-0ns=10ns

hold分析,requirement为0ns-0ns=0ns

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?