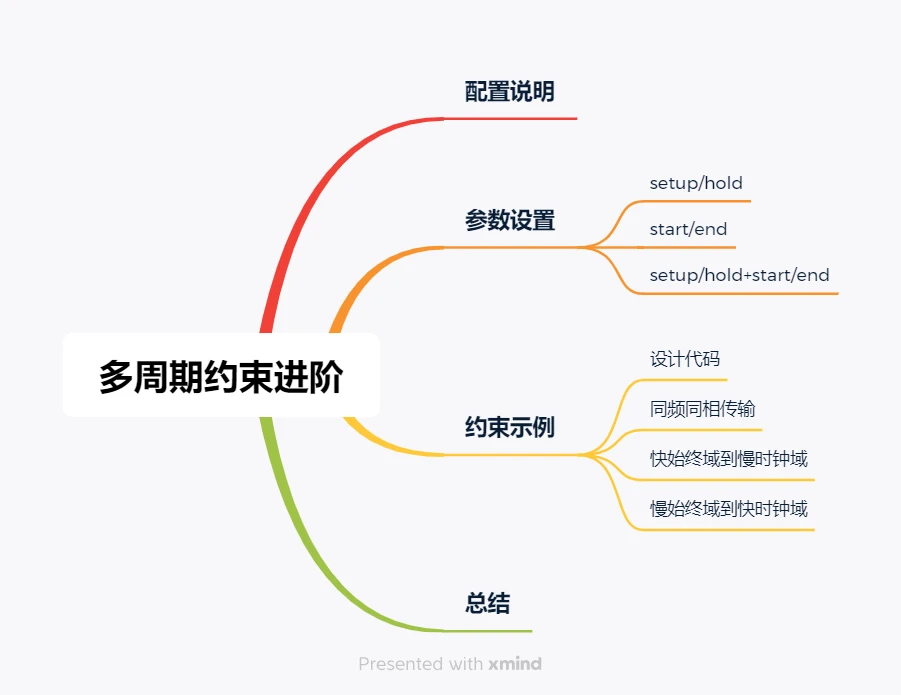

一、内容概览

二、前言

在前面的文章中,已经在https://zhuanlan.zhihu.com/p/660388515中对多周期约束set_multicycle_path进行了初步的解释说明。本文在上述的基础上从实际使用的角度进行进一步的说明

三、Set_Multicycle_Path约束

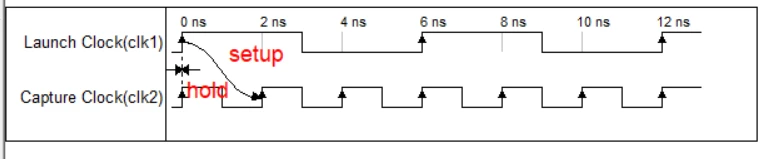

通常,对于同步时钟域内,时序分析中setup默认是在一个周期内分析,hold分析是在当前时刻进行分析,如下图,在0ns处Launch Clock传送的数据在Capture Clock的一个周期5ns后被捕获(setup),并且数据不能被Capture Clock 0ns的上升沿捕获到(hold)

在实际的设计中,往往存在跨时钟域路径,如Launch Clock和Capture Clock非同步时钟,但是有需要对其进行时序分析,此时就需要设置多周期约束,无论是快时钟域到慢时钟域还是慢时钟域到快时钟域。

多周期约束通俗的理解就是在默认分析边沿对的基础上改变发起时钟或捕获时钟的边沿进行分析,默认分析边沿对的选取规则可以看之前的文章《时序分析之setup/hold时钟path requirement解疑》,下面将针对各种场景进行示例说明。

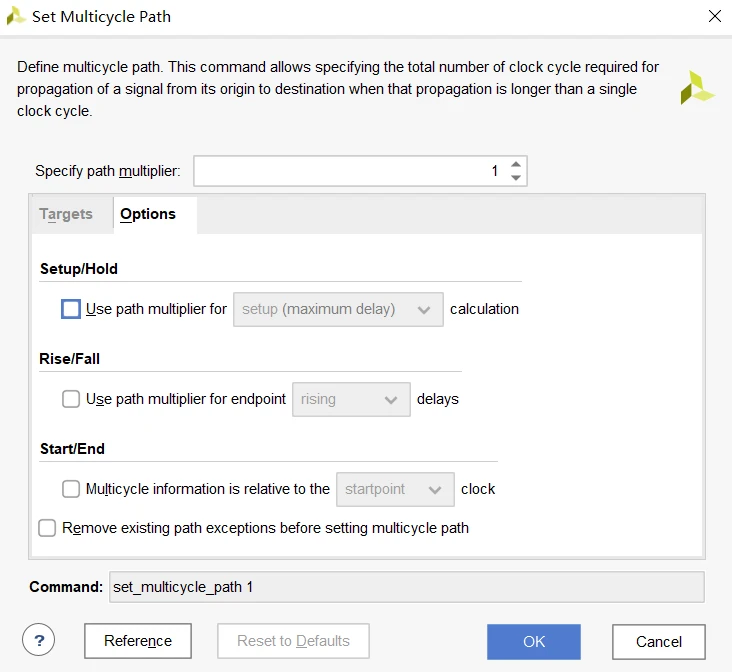

3.1 Set Multicycle Path参数

Set Multicycle Path约束的设置界面如下,Targets主要设置约束的路径,本文重点关注Options界面。

Specify path multiplier:设置约束的多周期数量,只能是正整数。

Setup/hold:用于设置约束是用于setup还是hold分析,默认为setup,但setup会影响hold

Rise/Fall:用于设置约束生效于endpoint的上升沿还是下降沿,默认rise和fall都有效。

Start/End:用于设置多周期作用于发起时钟launch clock还是捕获时钟capture clock,start对应发起时钟,end对应捕获时钟,setup默认为end,hold默认为start,对于同步时钟域,start/end是没有区别的。

Remove existing path exceptions before setting multicycle path:勾选后如果设置多周期约束的路径上有其他的exceptions约束,如set false path/set maximux delay/set minimum delay约束,其他的exceptions约束将不会生效,默认不勾选。

3.2 设计代码

示例设计为简单的两个触发器的路径代码

module multicyle(clk1,clk2,d,rst,out);

input clk1,clk2,d,rst;

output out;

reg ff1,out;

always@(posedge clk1,negedge rst)

if(!rst)

ff1<=0;

else begin

ff1<=d;

end

always@(posedge clk2,negedge rst)

if(!rst)

out<=0;

else begin

out<=ff1;

end

endmodule时钟约束如下

create_clock -period 2.000 -name clk1 -waveform {0.000 1.000} [get_ports clk1]

create_clock -period 5.000 -name clk2 -waveform {0.000 2.500} [get_ports clk2]3.3 参数示例说明

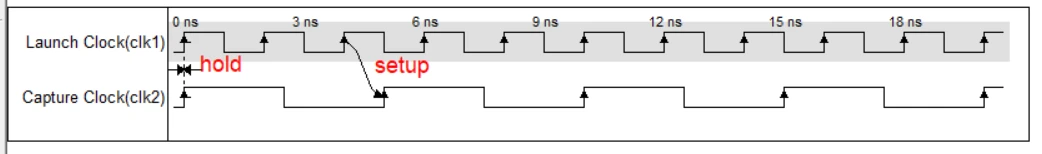

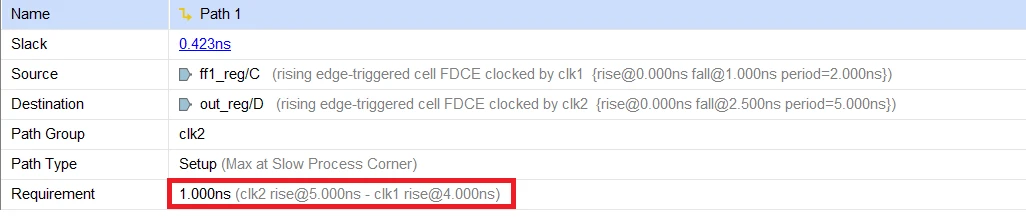

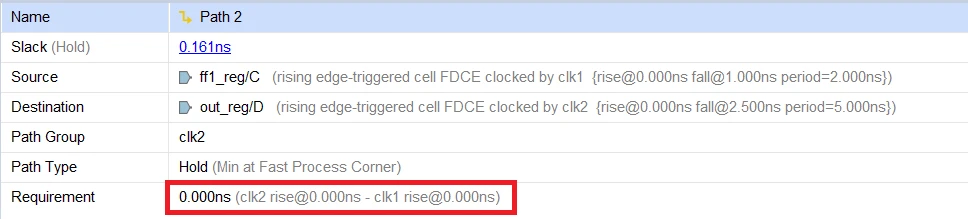

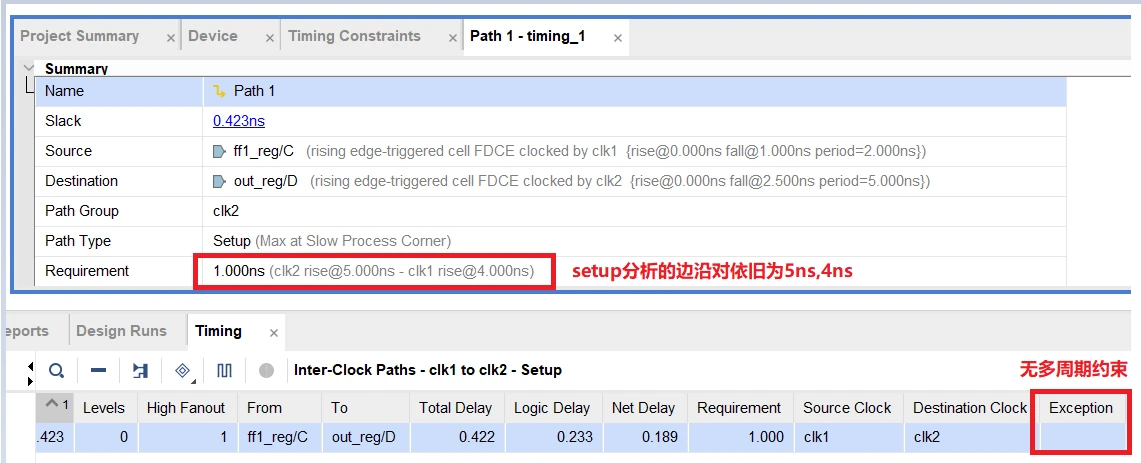

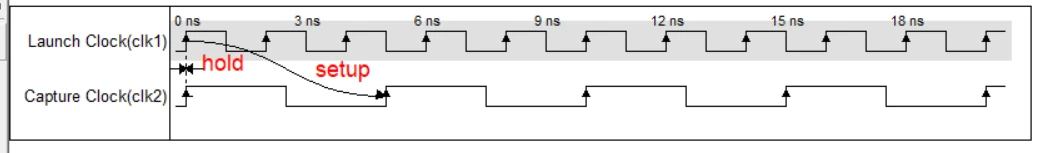

时钟clk1的周期为2ns,clk2的周期为5ns,占空比都为50%,第一个上升沿都在0ns处,在无多周期约束时默认的分析边沿对如下图

setup分析结果中requirement为5ns-4ns=1ns

hold分析结果,requirement为0ns-0ns=0ns

3.3.1 setup/hold参数

设置setup分析的多周期约束,约束命令如下

set_multicycle_path -setup -from [get_clocks clk1] 2

有一点需要注意,不设置多周期约束时,可以默认为设置了setup的周期数为set_multicycle_path -setup -end -from [get_clocks clk1] 1,即该约束设不设置都不会影响原本的分析。

a)只设置setup参数

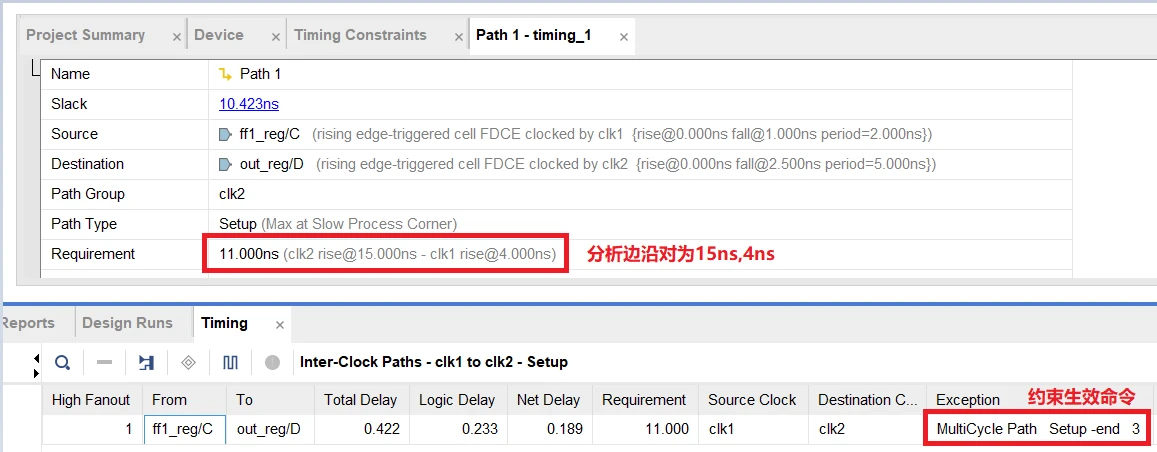

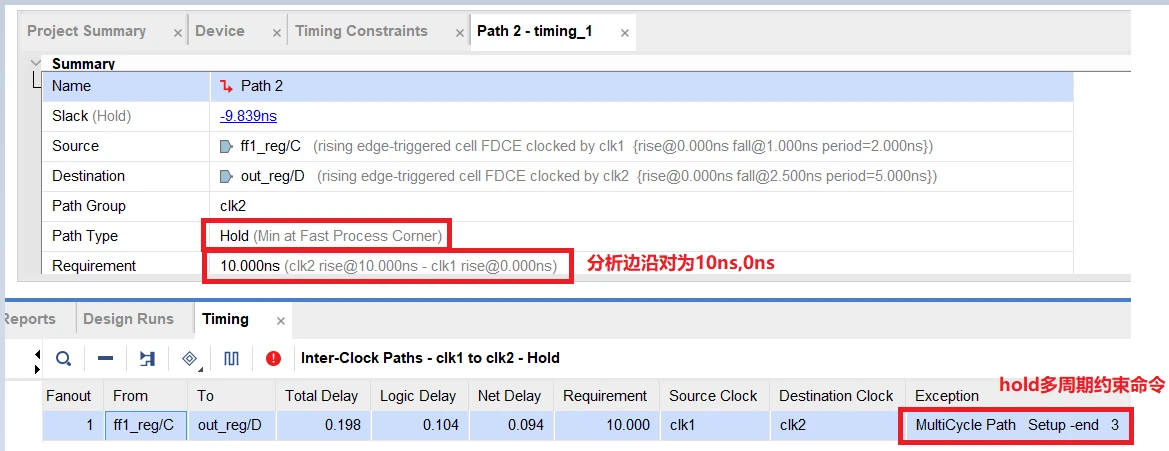

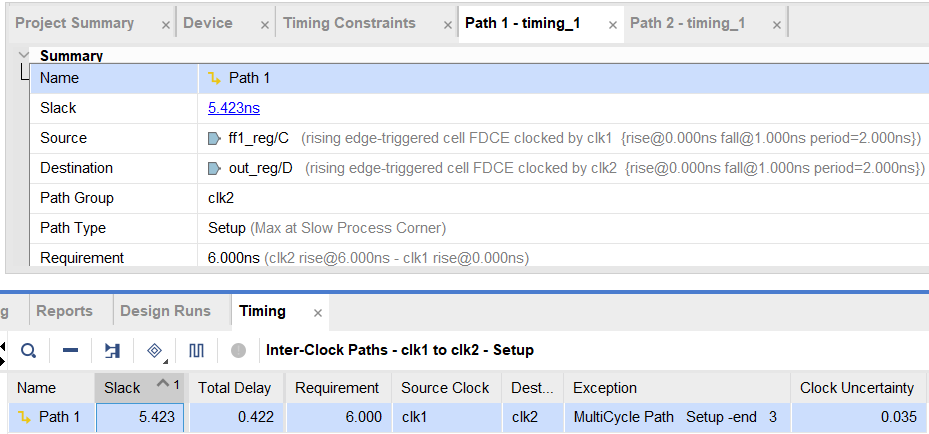

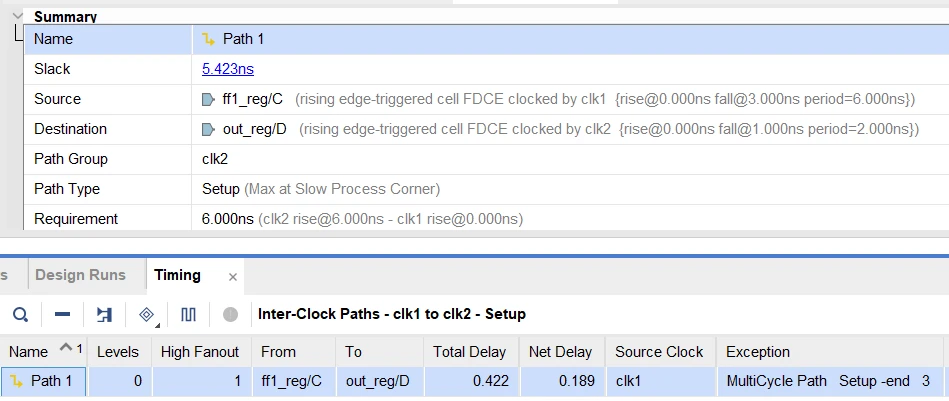

下面设置一条setup的约束如下,多周期约束值为3,约束生效的路径为以clk1为发起时钟的路径。

set_multicycle_path -setup -from [get_clocks clk1] 3

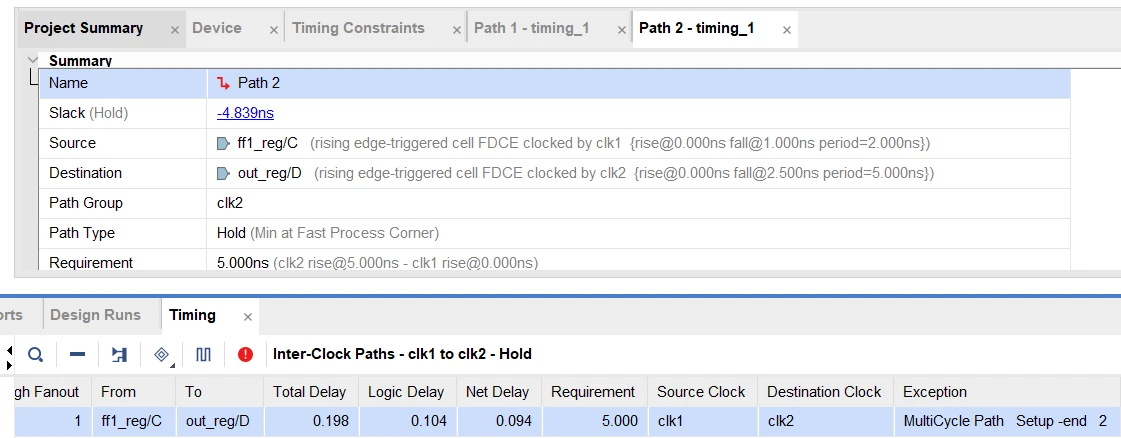

含义解析:根据约束的含义,对setup中的捕获时钟沿(未指定start/end时默认为end)移动两个周期(默认为1,设置3时表示移动了2个周期),查看分析结果

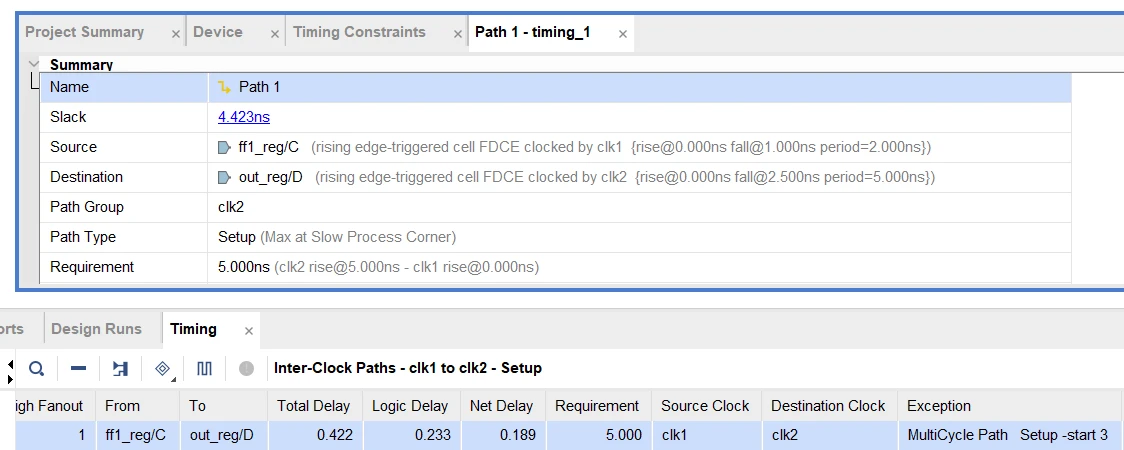

setup分析结果,分析边沿对由无多周期约束下的5ns-4ns成为多周期约束后的15ns-4ns,即将捕获时钟clk2的分析边沿往后移动了2个周期(5ns+2*5ns)为15ns,发起时钟的边沿不变

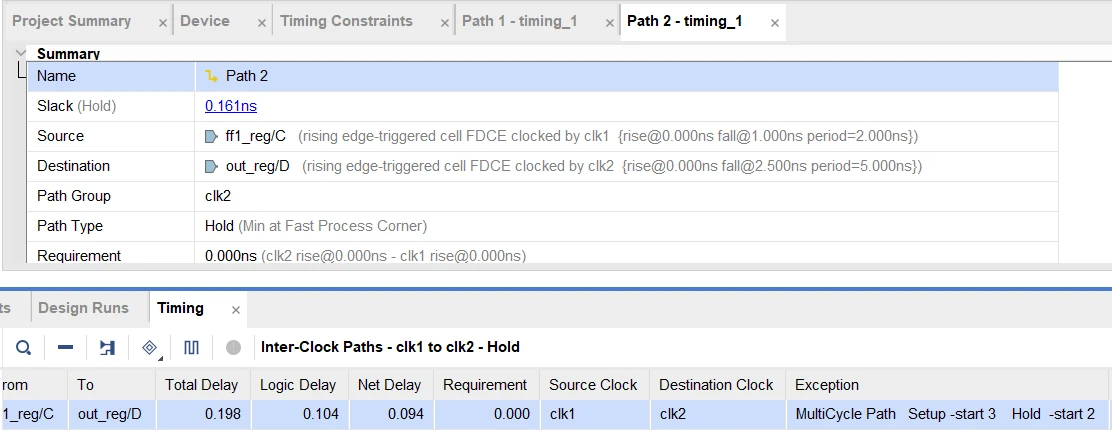

hold分析,虽然没有设置hold的多周期约束,但因setup分析的边沿已改变,hold分析的边沿也会同步变化,clk2边沿同样往后移动了2个周期为10ns

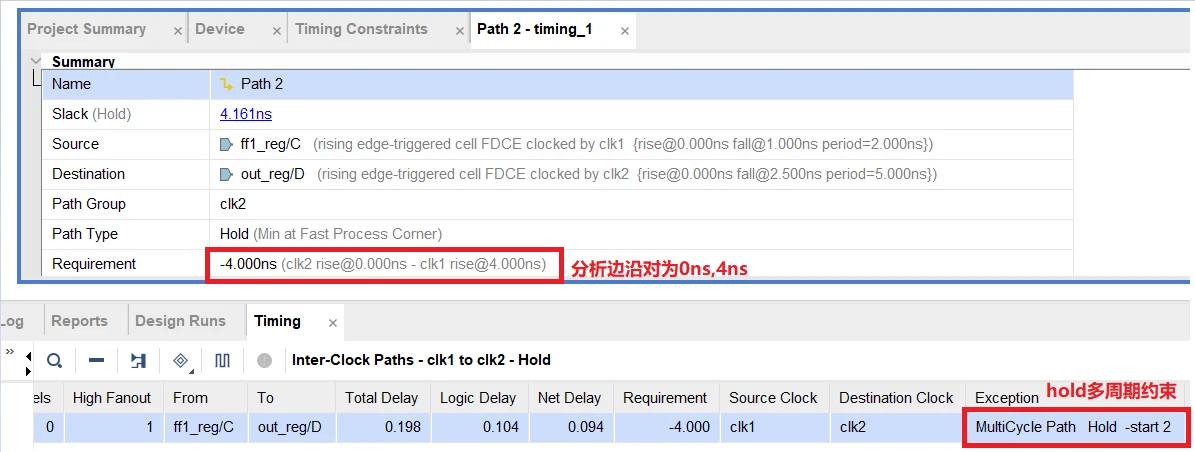

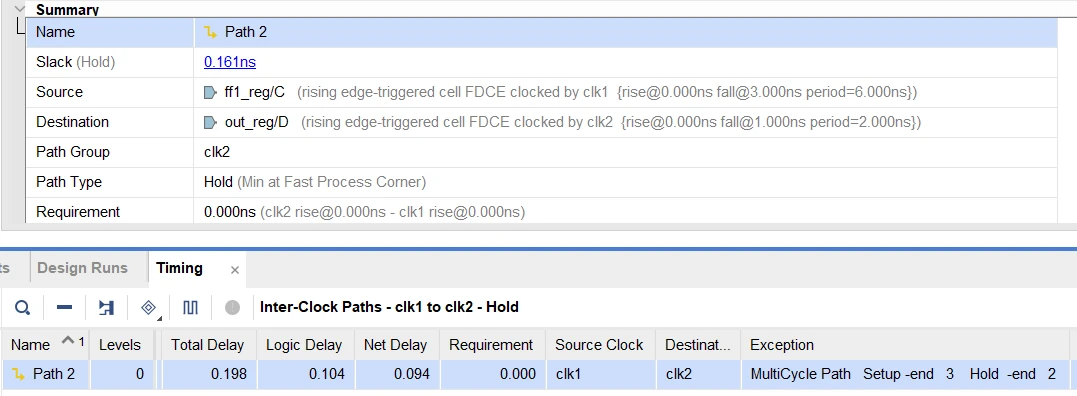

b)只设置hold参数

hold多周期约束如下,约束含义为hold分析时发起时钟边沿往后移动2个周期(hold多周期约束时钟默认为start,即发起时钟)

set_multicycle_path -hold -from [get_clocks clk1] 2

setup分析结果不受hold多周期的影响,requirement和slack不变。

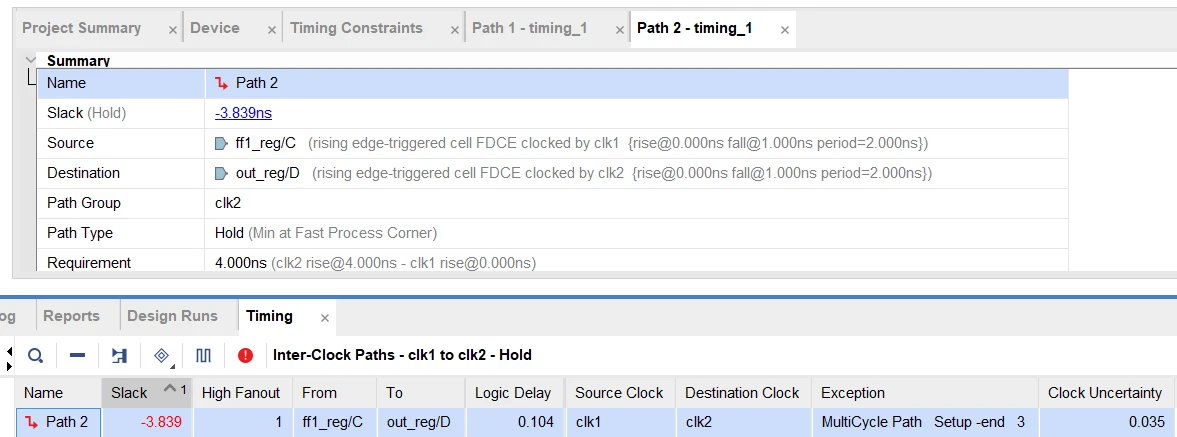

hold分析结果,分析边沿对中clk1已移动了2个周期变为4ns,clk2的边沿不变,此时requirement为0-4ns为-4ns

3.3.2 start/end参数

start/end参数用于设置边沿移动的时钟是捕获时钟还是发起时钟。

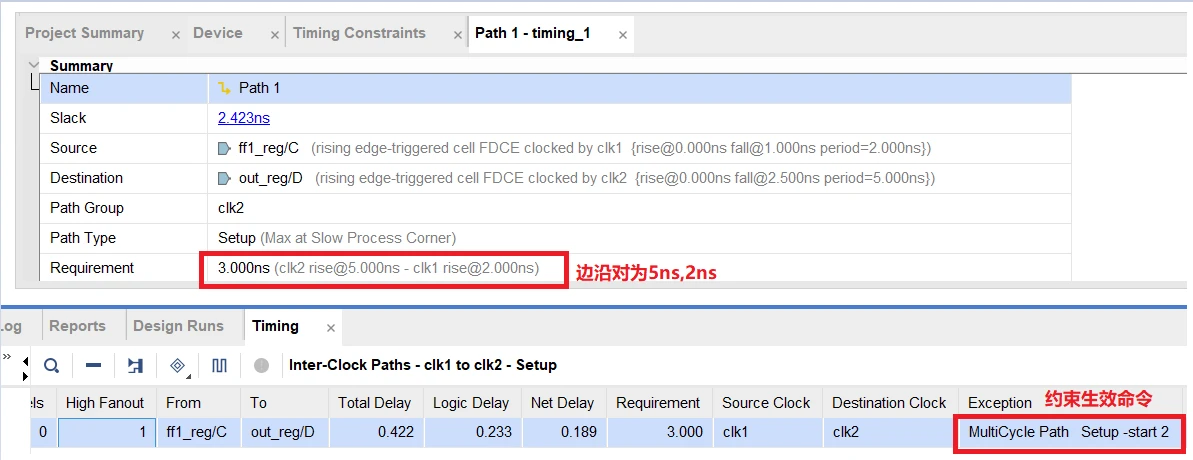

a)只设置start参数

约束只指定start参数,根据前面的参数解释,可知setup/hold未指定时,默认setup,约束如下

set_multicycle_path -start -from [get_clocks clk1] 2

该命令等效如下命令

set_multicycle_path -setup -start -from [get_clocks clk1] 2

即将setup分析的发起时钟start移动1(减去默认的1个周期)个周期,捕获边沿不变

setup分析结果,边沿对由默认的5ns,4ns变为5ns,2ns,即发起时钟向前移动了1个周期

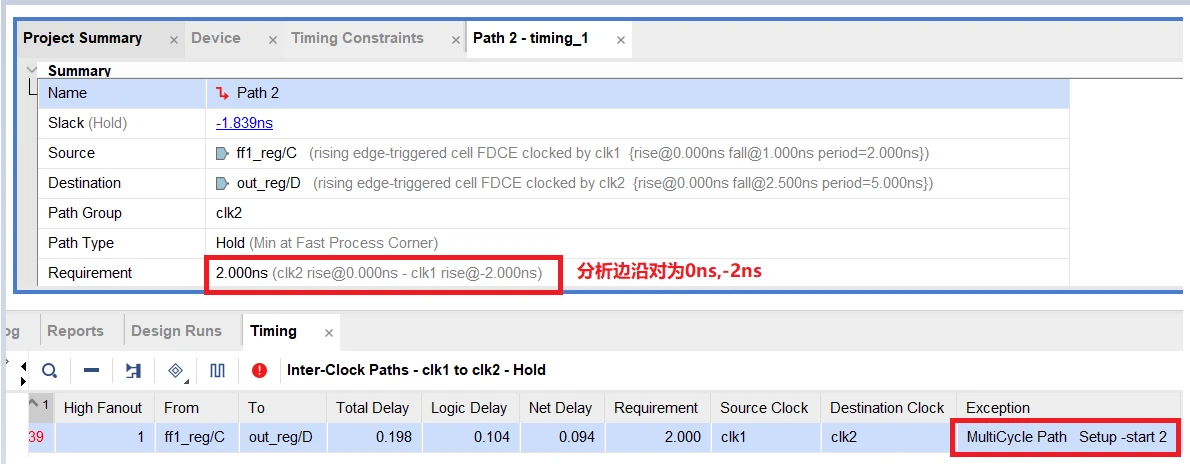

hold分析结果,因受setup分析边沿的变化,同步的调整了clk1的边沿,向前移动了一个周期,因此为-2ns

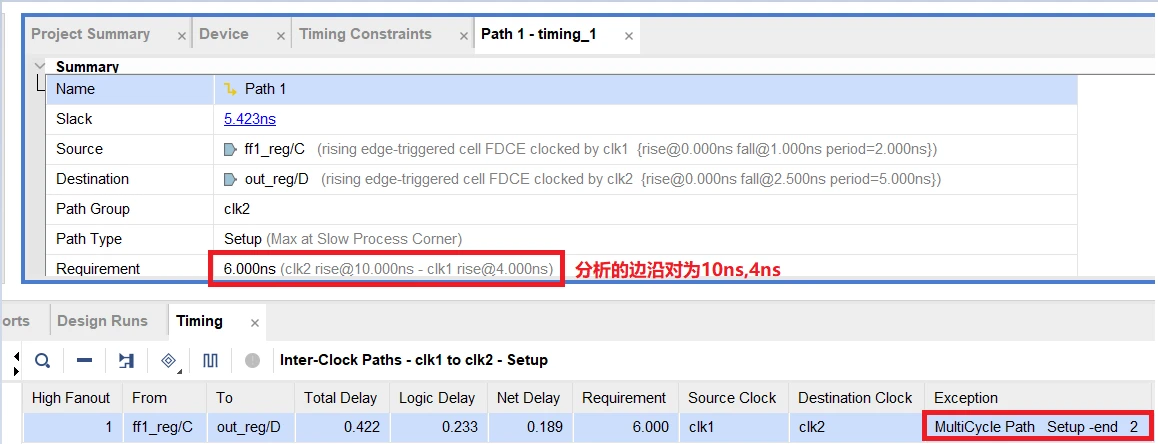

b)只设置end参数

只设置end参数的约束如下

set_multicycle_path -end -from [get_clocks clk1] 2

未设置setup/hold参数时,默认使用setup,因此上述约束等效如下

set_multicycle_path -setup -end -from [get_clocks clk1] 2

setup分析,捕获时钟clk2向后移动一个周期,clk1的边沿不变,requirement为10ns-4ns=6ns

因setup分析的边沿对变化了,hold的分析边沿对同步会变化,clk2同步移动一个周期,捕获边沿从0ns变为5ns

四 应用示例

4.1 同频同相时钟域

以clk1,clk2是同频同相的时钟,周围为2ns,占空比为50%,默认的setup/hold分析边沿如下图

如果实际需要进行分析的边沿如下图,即向前移动2个周期

根据之前的参数,只需对setup进行多周期约束如下

set_multicycle_path -setup -end -from [get_clocks clk1] 3

setup分析结果,分析的边沿对变为6ns,0ns

hold分析边沿对由原来的0ns,0ns变为4ns,0ns

4.2 快时钟域到慢时钟域

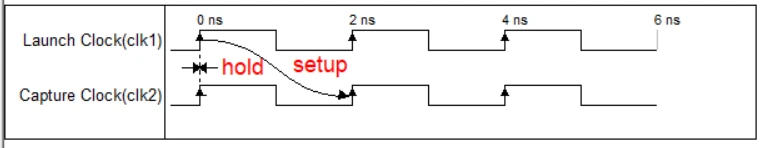

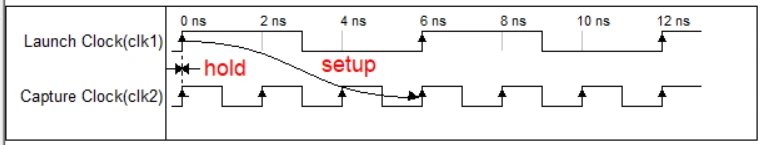

下面将对实际场景进行约束示例,以clk1,clk2周期分别为2ns,5ns,占空比50%,都在0ns为第一个上升沿。clk1到clk2准确的setup/hold分析边沿对如下图,即setup分析时发起时钟应该在0ns的位置

下面对上述快时钟到慢时钟域的信号进行正确的约束如下

set_multicycle_path -setup -start -from [get_clocks clk1] 3

set_multicycle_path -hold -start -from [get_clocks clk1] 2对setup分析的边沿对中对启动时钟向后移动2个周期

setup分析结果如下,捕获时钟clk2边沿不变为5ns,clk1的向后移动2个周期从4ns变为0ns

hold分析在setup分析边沿变化,发起时钟clk1也同步向后移动2个周期,从0ns变为-4ns,又有自身的约束start向前移动2个周期,因为分析边沿还是0ns

4.3 慢时钟域到快时钟域

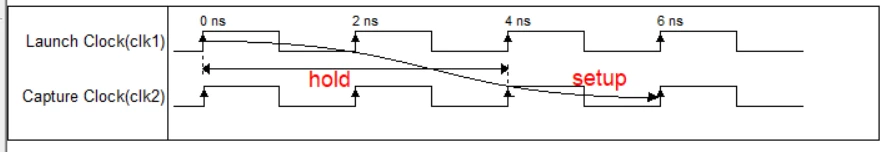

clk1和clk2的周期分别为6ns,23ns,占空比都是50%,都在0ns处有第一个上升沿,默认情况下setup/hold分析的边沿对如下,setup分析边沿对为0ns:2ns,hold分析为0ns:0ns

实际正确的分析应如下图,setup分析中start应后移一个周期

通过多周期约束如下

set_multicycle_path -setup -end -from [get_clocks clk1] 3

set_multicycle_path -hold -end -from [get_clocks clk1] 2setup分析结果,捕获时钟clk2向前移动了2个周期,边沿从2ns变为6ns

hold分析因要保持不变,在setup约束的作用下clk2向前移动了2个周期,故需要再向后移动2个周期,即通过-hold -end 2实现,最终分析边沿为0ns,0ns

五、总结

1、multicycle的multiplier值在setup中默认为1,在hold中默认为0(理论分析上,实际不可设置)

2、multicycle约束是在默认的边沿分析对基础上根据约束对发起时钟或捕获时钟边沿进行修改

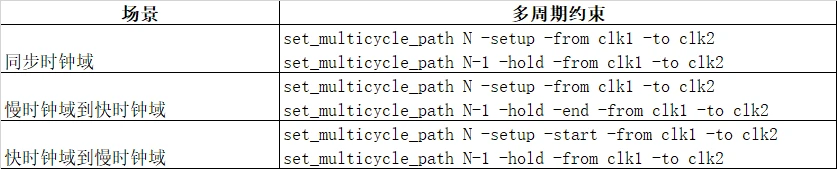

针对三种典型场景的多周期约束如下

2134

2134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?