一、用与非门构造RS锁存器(RS触发器)

RS触发器属于时序逻辑电路,其信号形成是由RS触发器将输出信号引回到输入信号,形成一个反馈。这样是的输出信号的状态不但取决于同时输入的输入信号状态,也与输出之前的状态相关。而我们平常学习的电路属于组合逻辑电路,它的输出状态值取决于同时输入的输入信号状态。

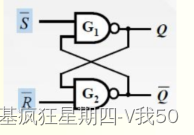

1.电路图

输入端:

S:置位端(设置端Set)

R:复位端(Reset)

没有时钟输入端

输出端:

Q:状态输出端

:反相状态输出端

2.逻辑功能图

与非门逻辑功能表

RS触发器(与非门)逻辑功能表

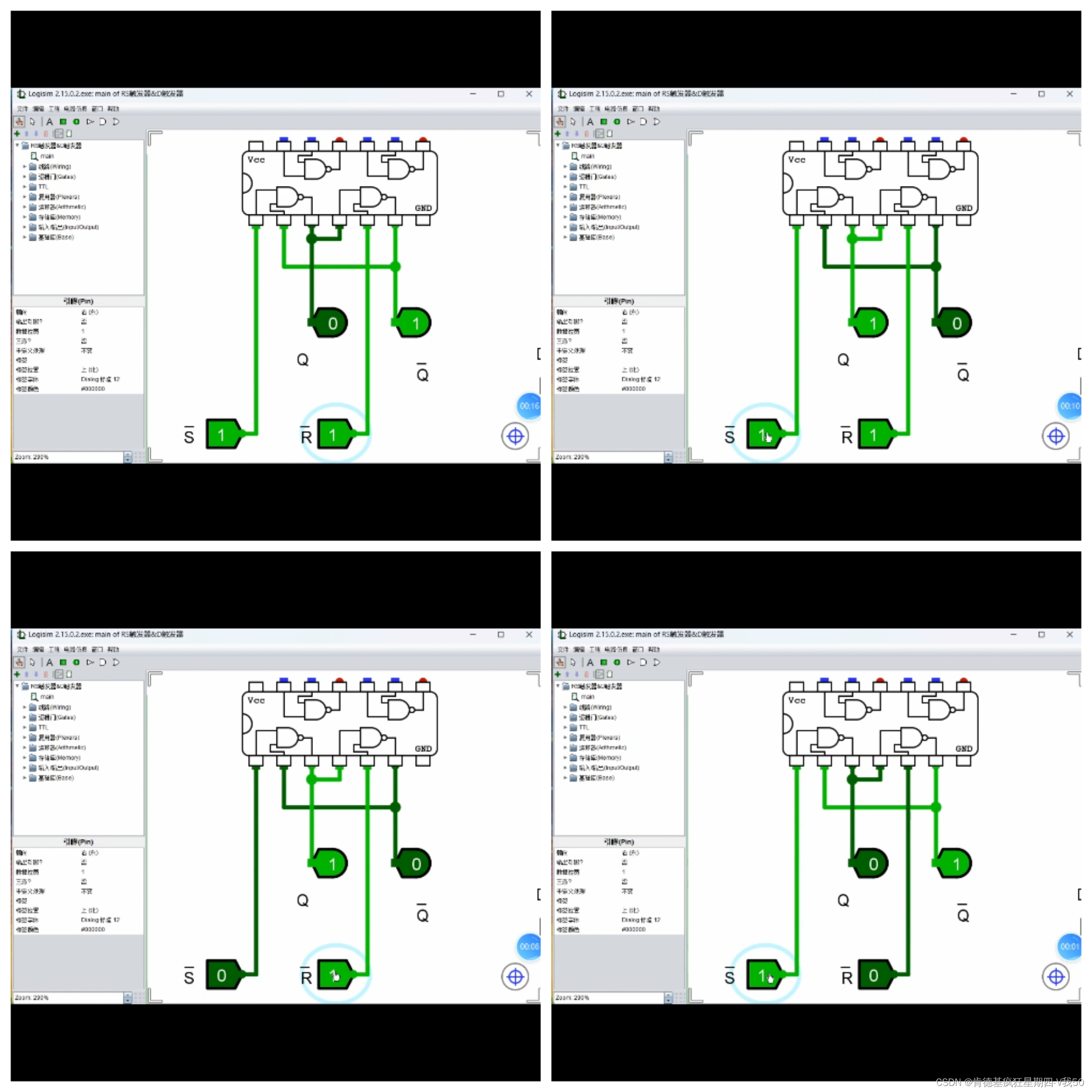

输入信号R、S的作用方法:低电平有效。

3.RS触发器结论

(1.)不论现态是什么,

在R端施加低电平能够将现态强制性地转换到“0”态;

在S端施加低电平能够将现态强制性地转换到“1”态;

R和S不能同时施加低电平。

(2.)R和S端的有效电平为低电平。

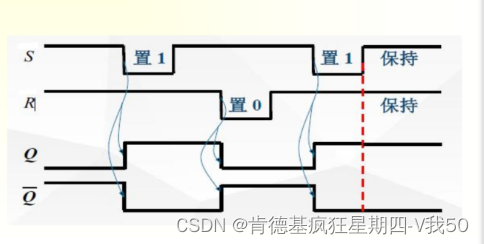

4.RS触发器(与非门)电平图

假设RS触发器的初态Q=0

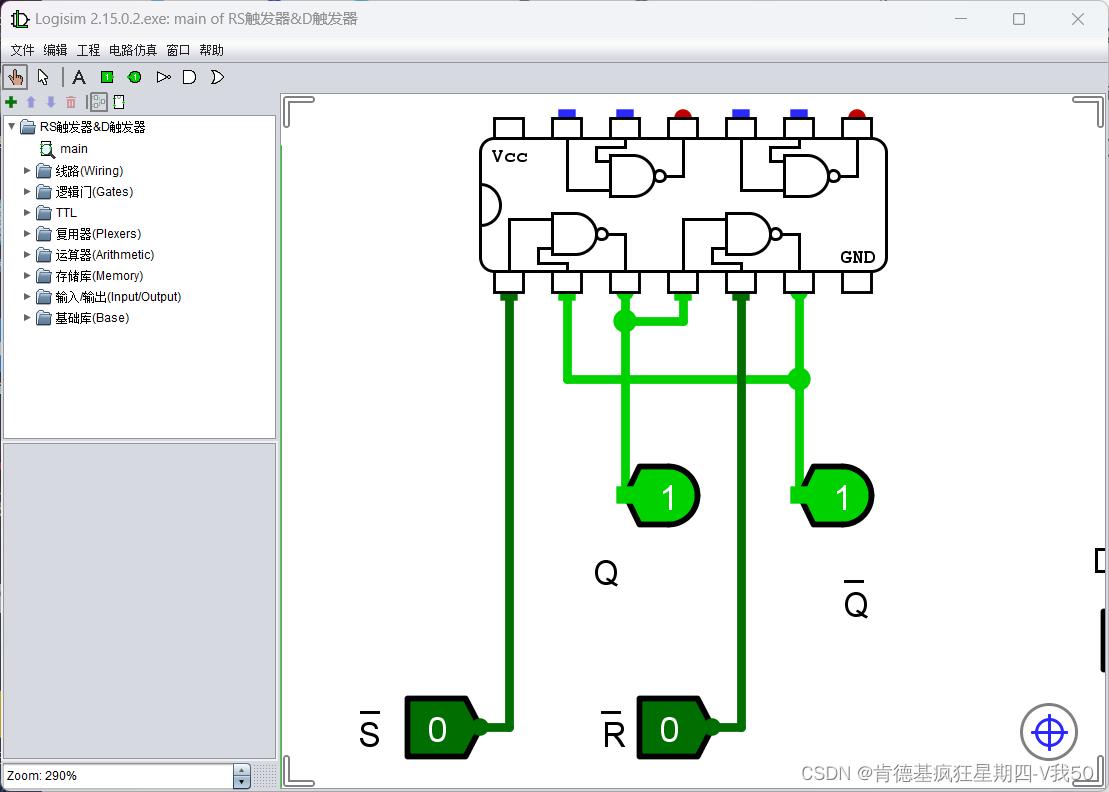

5.RS触发逻辑电路设计

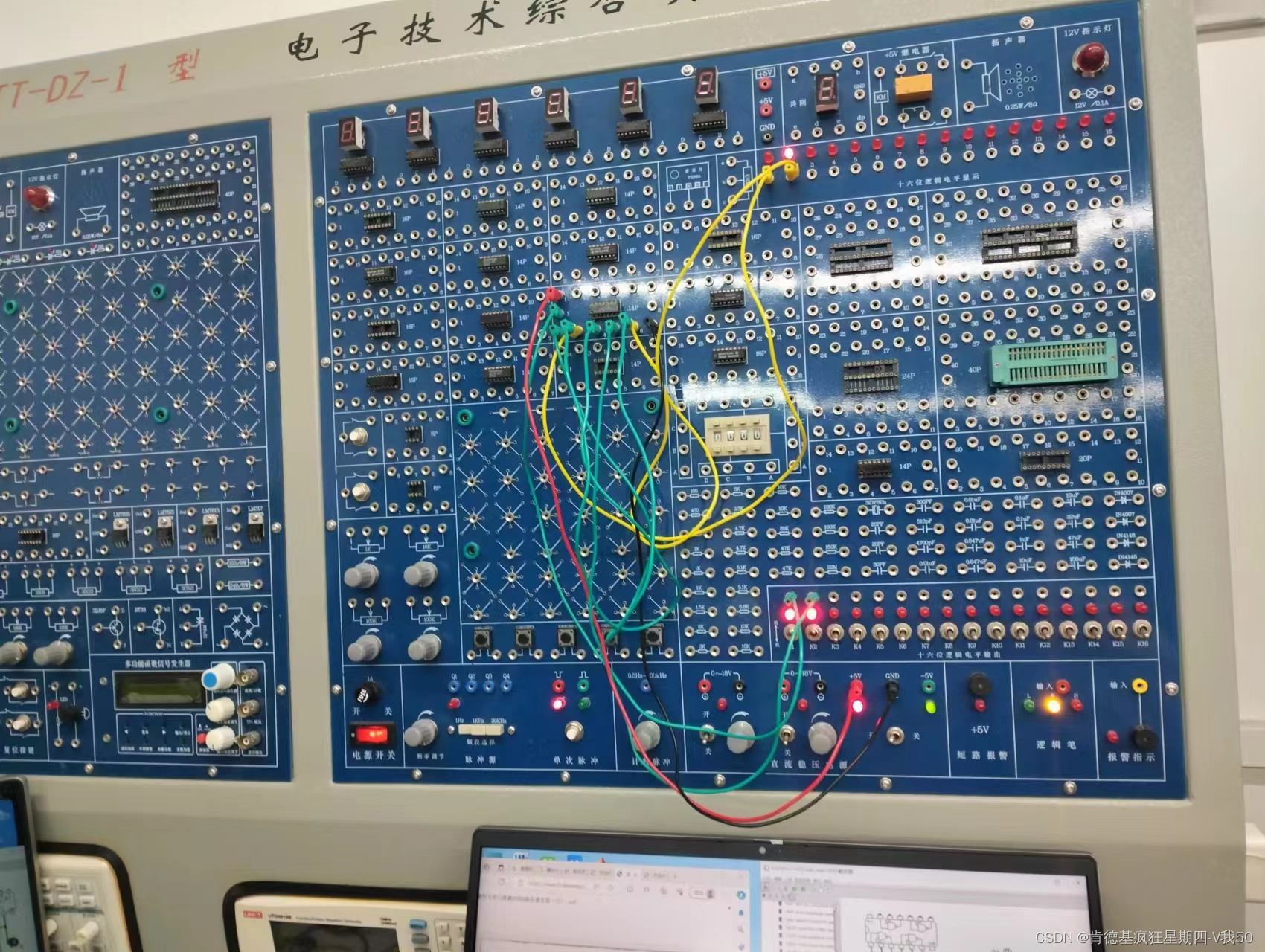

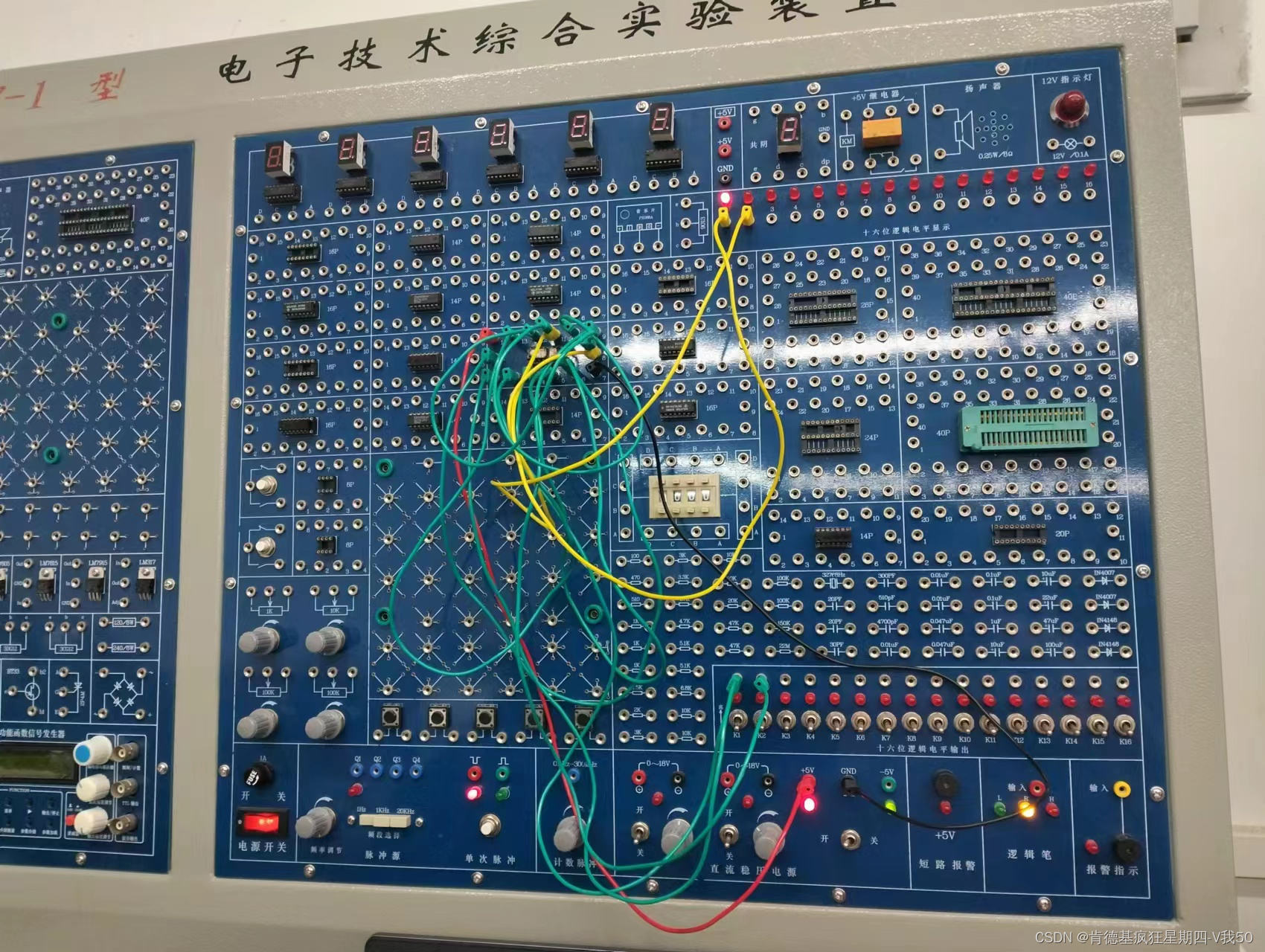

6.RS触发器电路实现

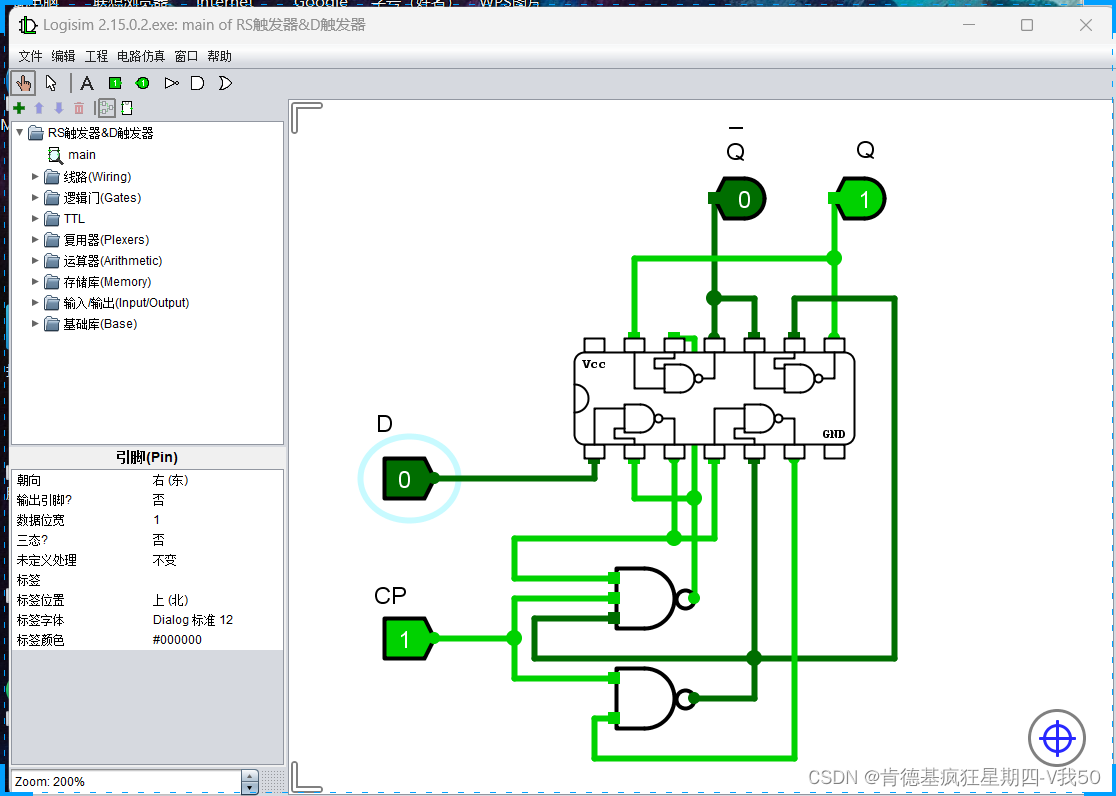

二、D型触发器

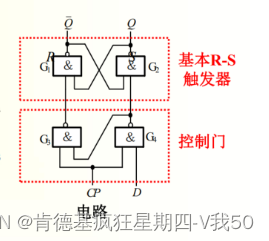

D型触发器由4个与非门组成,其中G1和G2构成基本RS触发器。G3和G4构成控制门。其可以解决输入约束问题。

1.电路图

D触发器工作原理:

CP=0:G3、G4被封锁,D的变化不能传到G1、G2,触发器保持现状态

CP=1:G3、G4门开放,D经G3、G4转换成一对互补信号送到G1、G2。

若D=0,则RS=01,Q=0;

若D=1,则RS=10,Q=1。

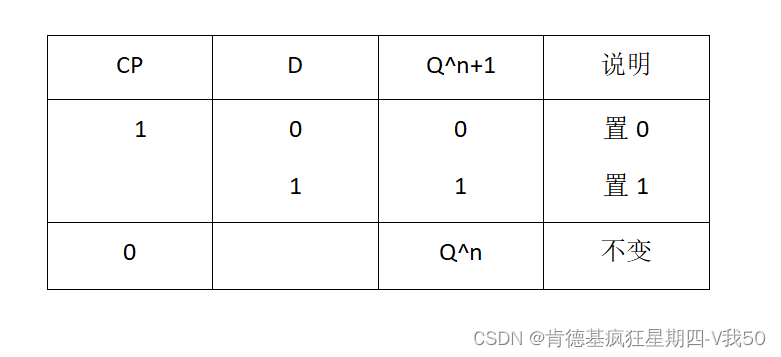

2.逻辑功能图

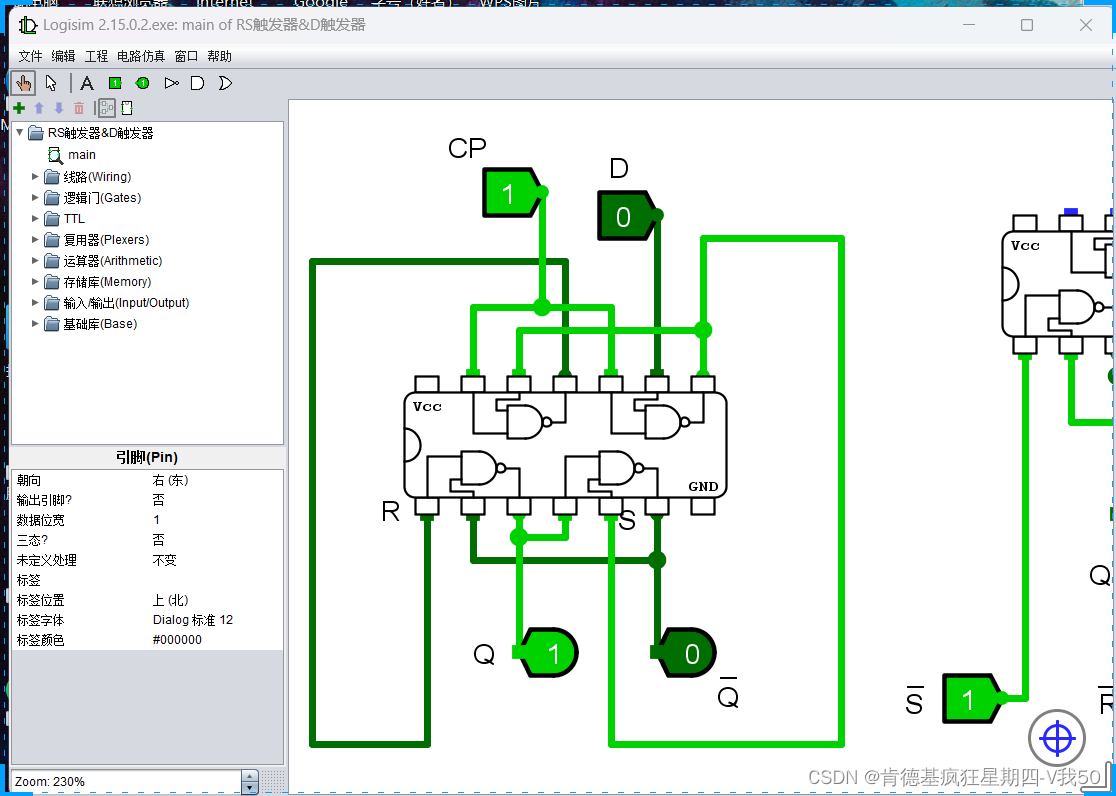

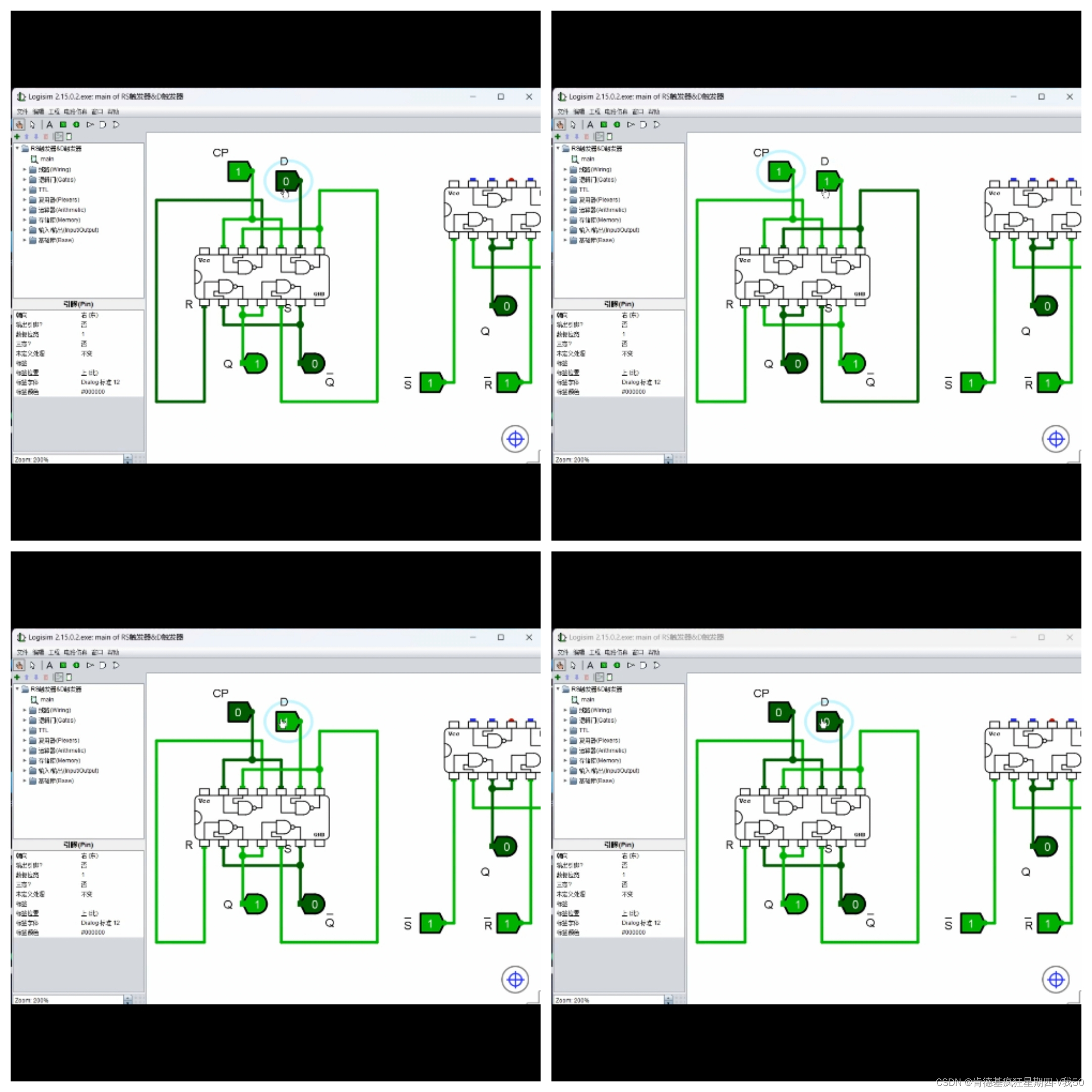

3.D型触发器逻辑电路设计

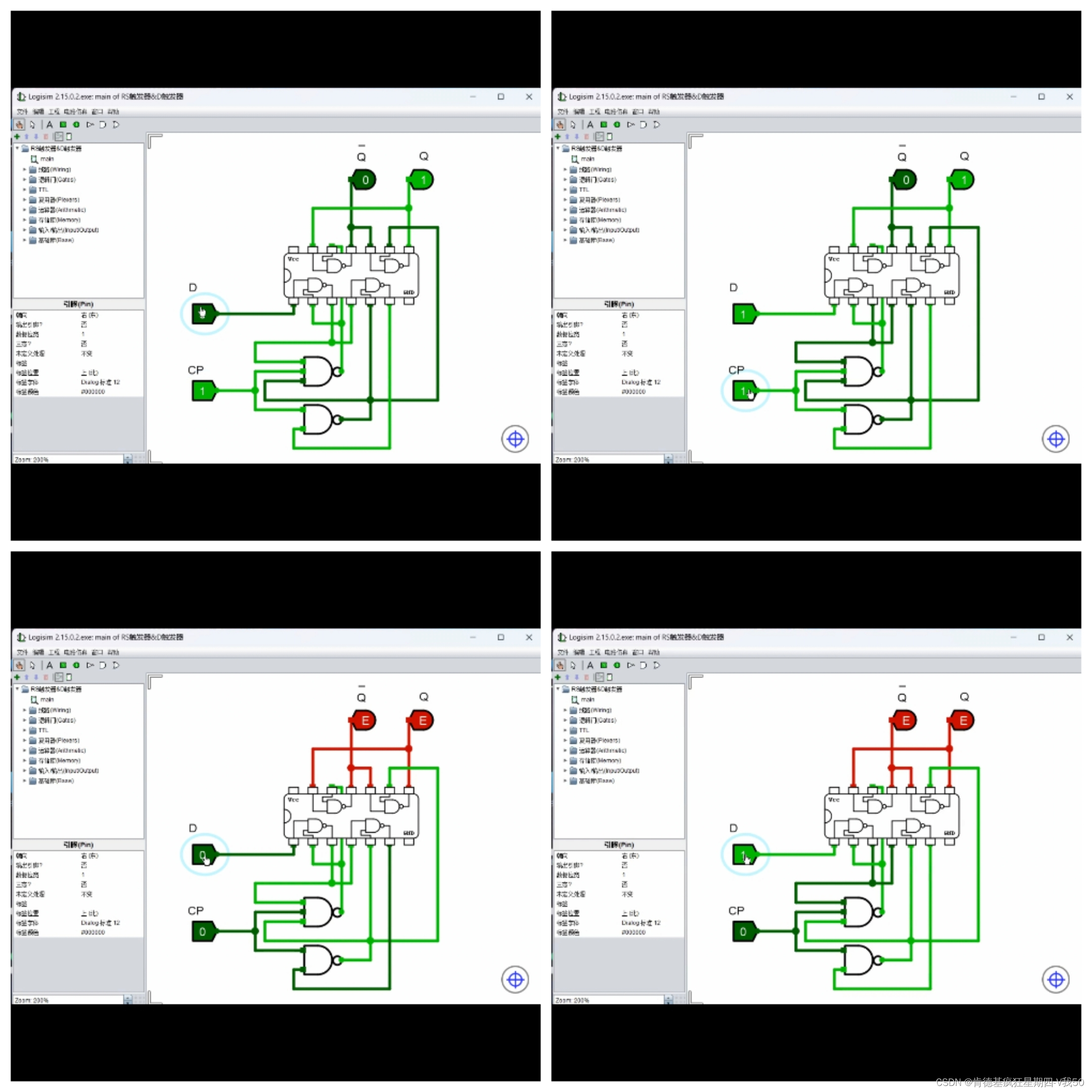

4.D型触发器电路实验

由于该RS触发器由与非门构建,所以当CP和D都为0时处于不稳定的状态,通过图片可见,当CP和D为0时,Q和处于不稳定的随机亮灯状态。

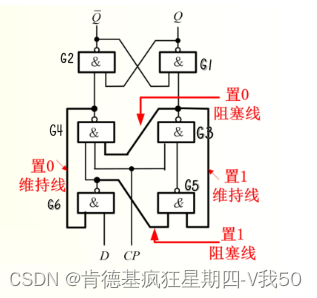

三、维持阻塞D触发器

由G1,G2构成了基本SR触发器。G3,G4,G5,G6构成了D信号的输入通道。

目的:为了解决“空翻”问题。

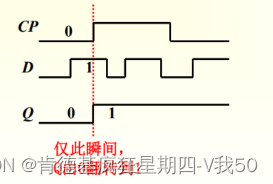

为了维持阻塞线路的作用,仅当CP的上升出现的一瞬间,D端的数据才能置入触发器。

1.电路图

当CP=0时;触发器维持原状态不变。输入信号D到达G4,G3的输入端,等待送入。

当CP由0变为1时,Q^(n+1)=D,并立即封锁输入通道。

2.维持阻塞D触发器电平图

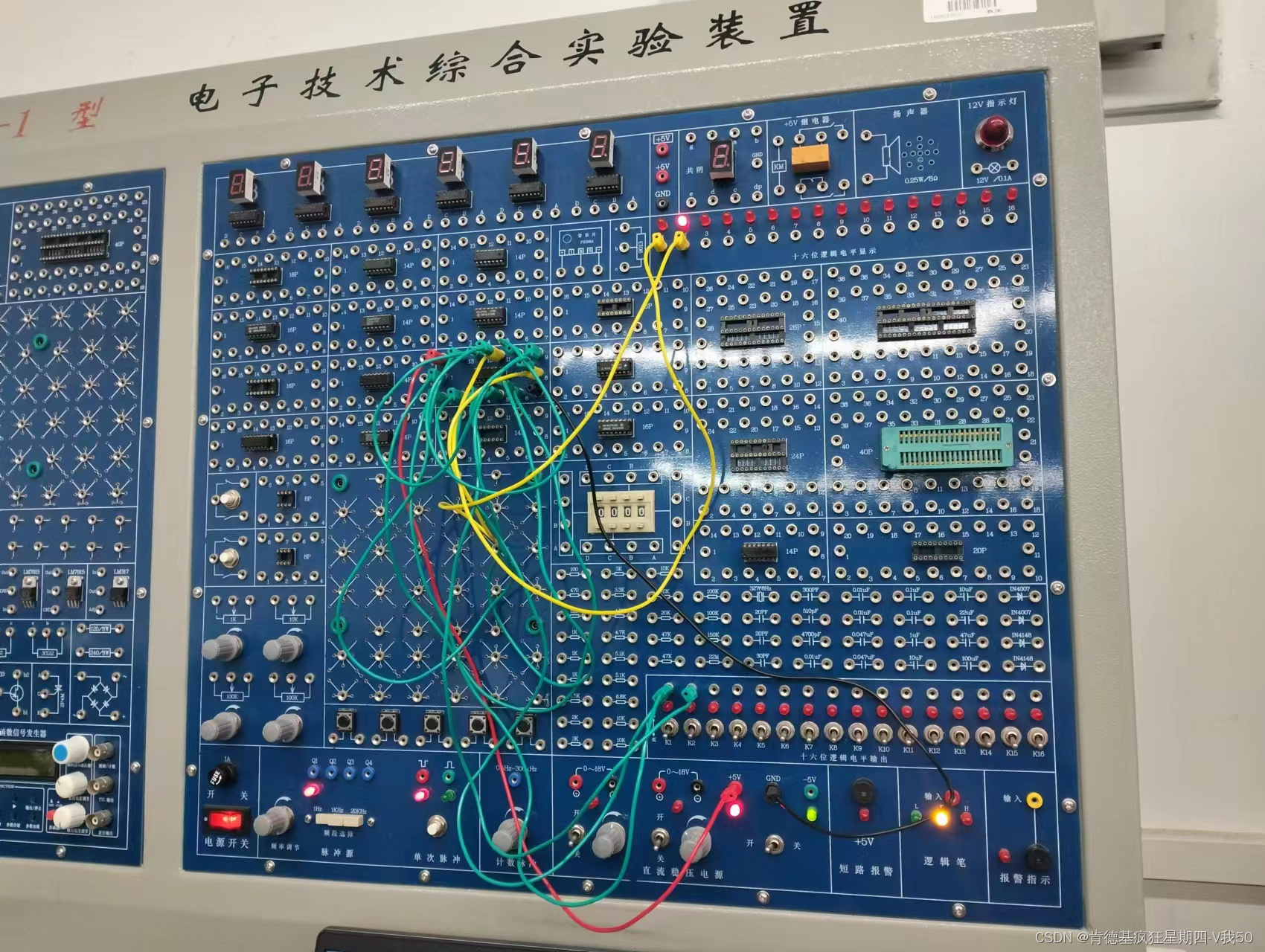

3.维持阻塞D触发器电路设计

本文介绍了RS触发器,一种利用与非门构成的时序逻辑电路,其功能取决于输入信号R和S的状态以及输出历史。随后讨论了D型触发器,由四个与非门组成,解决了输入约束问题。还提到了维持阻塞D触发器,用于防止空翻现象。

本文介绍了RS触发器,一种利用与非门构成的时序逻辑电路,其功能取决于输入信号R和S的状态以及输出历史。随后讨论了D型触发器,由四个与非门组成,解决了输入约束问题。还提到了维持阻塞D触发器,用于防止空翻现象。

742

742

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?