一,RS锁存器

(一)RS锁存器的简介

RS锁存器是一两输入、两输出的电路,其有两个互相交叉反馈相连的两个与非门构成,其两个输出为两个相反的输出(或称为互补输出)。

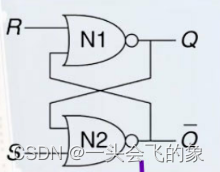

(二)RS锁存器的电路结构

基本的RS锁存器可以由或非门实现,如下图所示。

(三)RS锁存器的特性

根据RS锁存器的电路结构图可得,

①当R端可S端都为0时,它是保持上次输出不变的,这也是它的锁存特性(?)

②当R端和S端都为1时,就会让电路进入一个危险的状态,推导可知,此时输出 Q 和 Q非 均为0,但由于实际电路的延迟,S端和R端不可能同时变为0,就会出现不确定值,故R端和S端都为1时称为非法状态,设计电路时应避免这个状态

③当R端为0,S端为1,由电路图可知,Q始终为1,故称S端为置位端(置1端)

④当R端为1,S端为0,由电路图可知,Q始终为0,故称R端为复位端(置0端)

从置位端和复位端的称谓来看,也不能让两者同时有效(同时为1),这也没有实际上的意义。

与非门组成的触发器:不论是什么状态,在R端施加低电平能将现在的状态强制转换到“0”态;在S端施加低电平能将现在的状态强制转换到“1”态;R与S输入端不能同时为低电平。R和S输入端的有效电平为低电平。

或非门组成的触发器:不论是什么状态,在R端施加高电平能将现在的状态强制转化到“0”态。在S端施加高电平能将现在的状态强制转化到“1”态。R与S输入端不能同时为高电平。R和S输入端的有效电平为高电平。

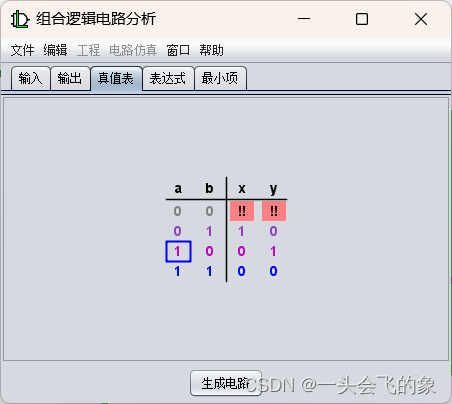

如下图,为RS锁存器的特征表

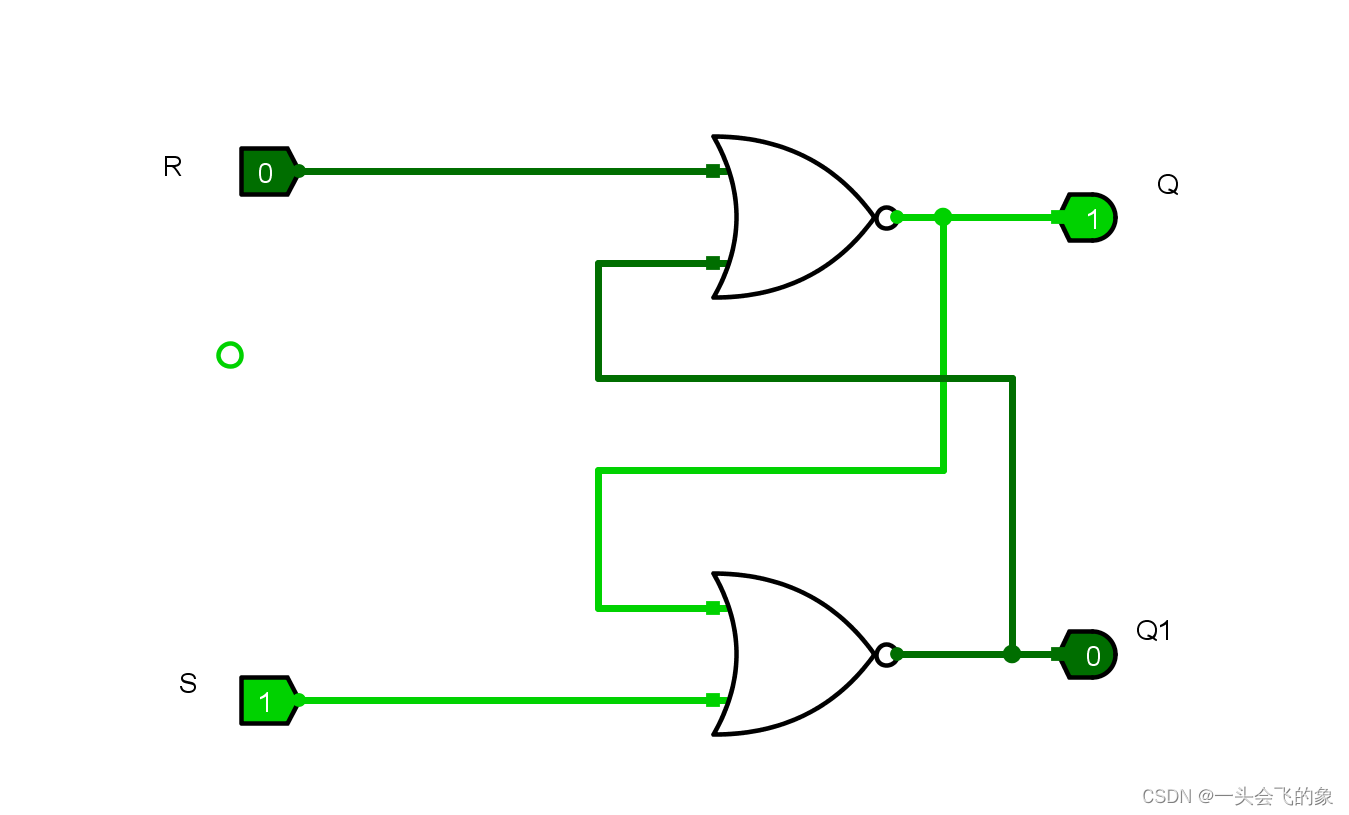

(四)RS锁存器的仿真及验证

用logsim采用门电路设计基本RS锁存器,进行仿真,如下图所示。

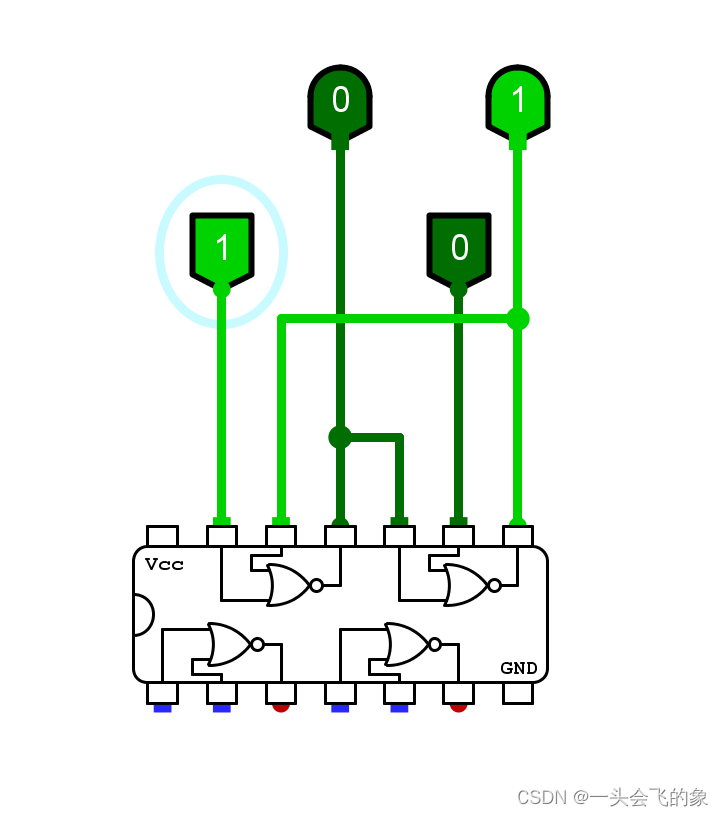

用logsim采用74LSxx系列设计基本RS锁存器,进行仿真,如下图所示。

最终在logsim软件中得到其真值表,如下图所示

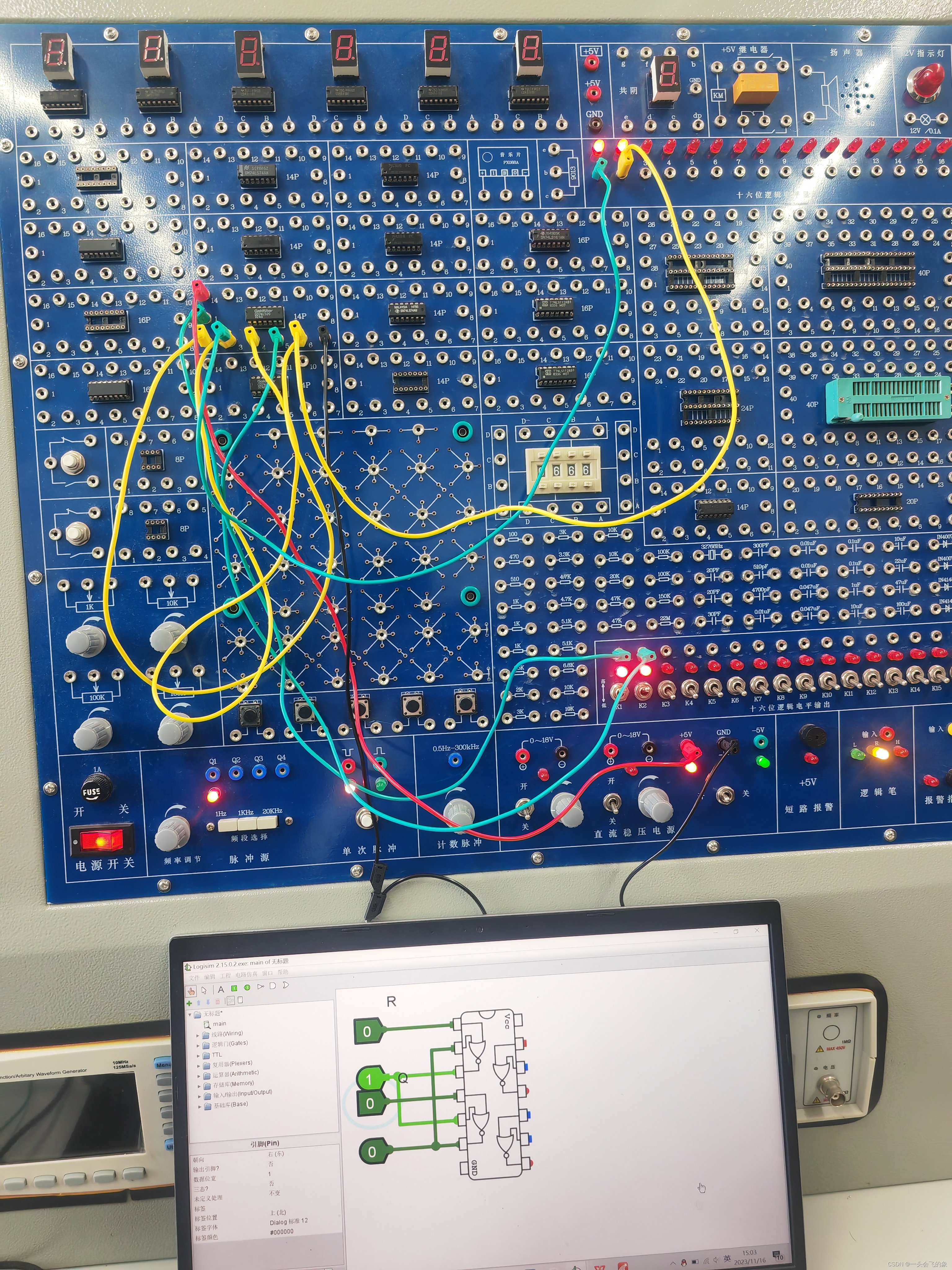

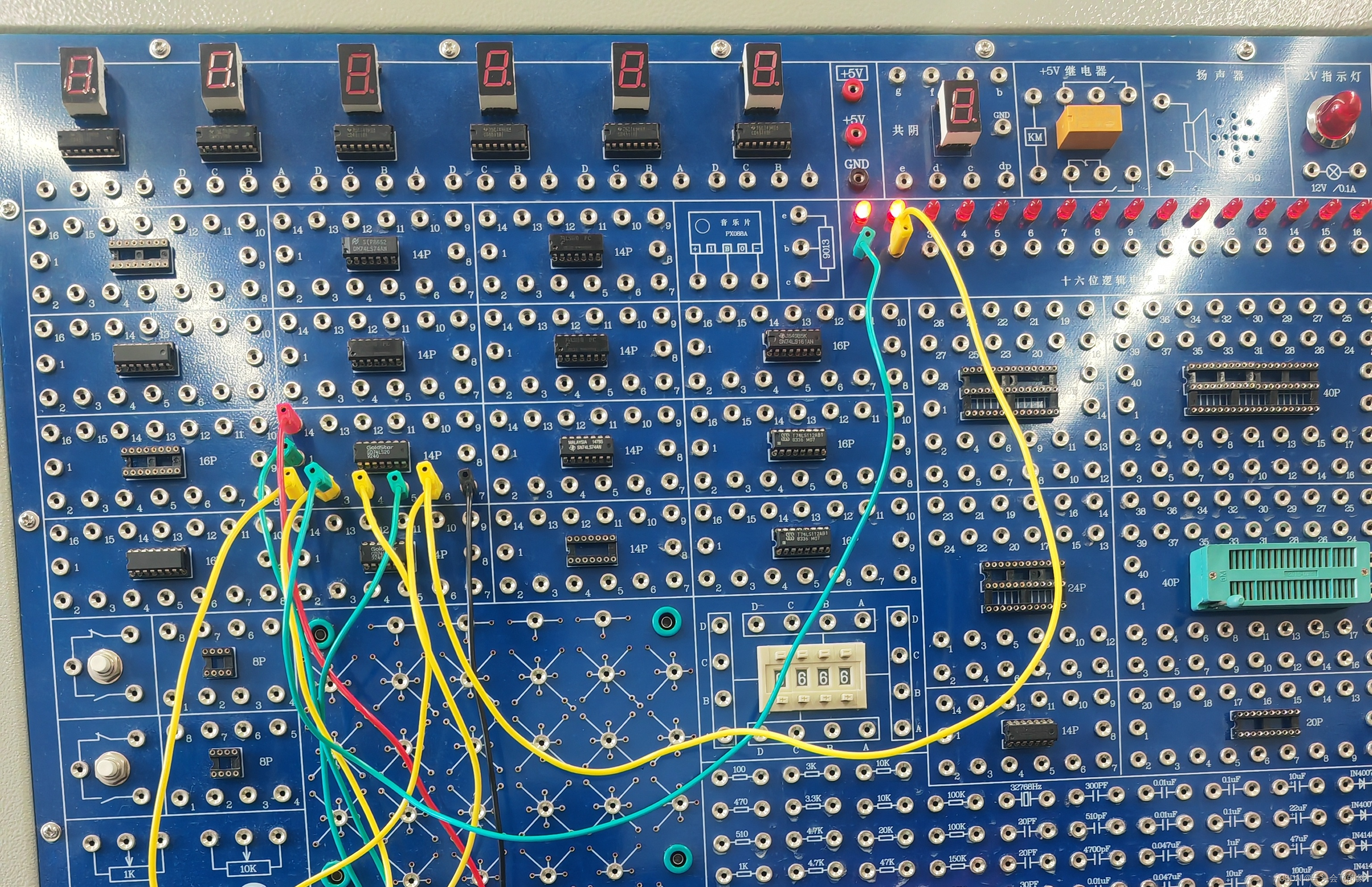

利用实验器材进行验证,如下图

最终得到实验结果符合上述说法。

二,D型触发器

(一)D型触发器的简介

D触发器是一种最简单的触发器,在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。在两个有效的脉冲边沿之间,D的跳转不会影响触发器存储的值,但是在脉冲边沿到来之前,输入端D必须有足够的建立时间,保证信号稳定。

(二)D型触发器的电路结构

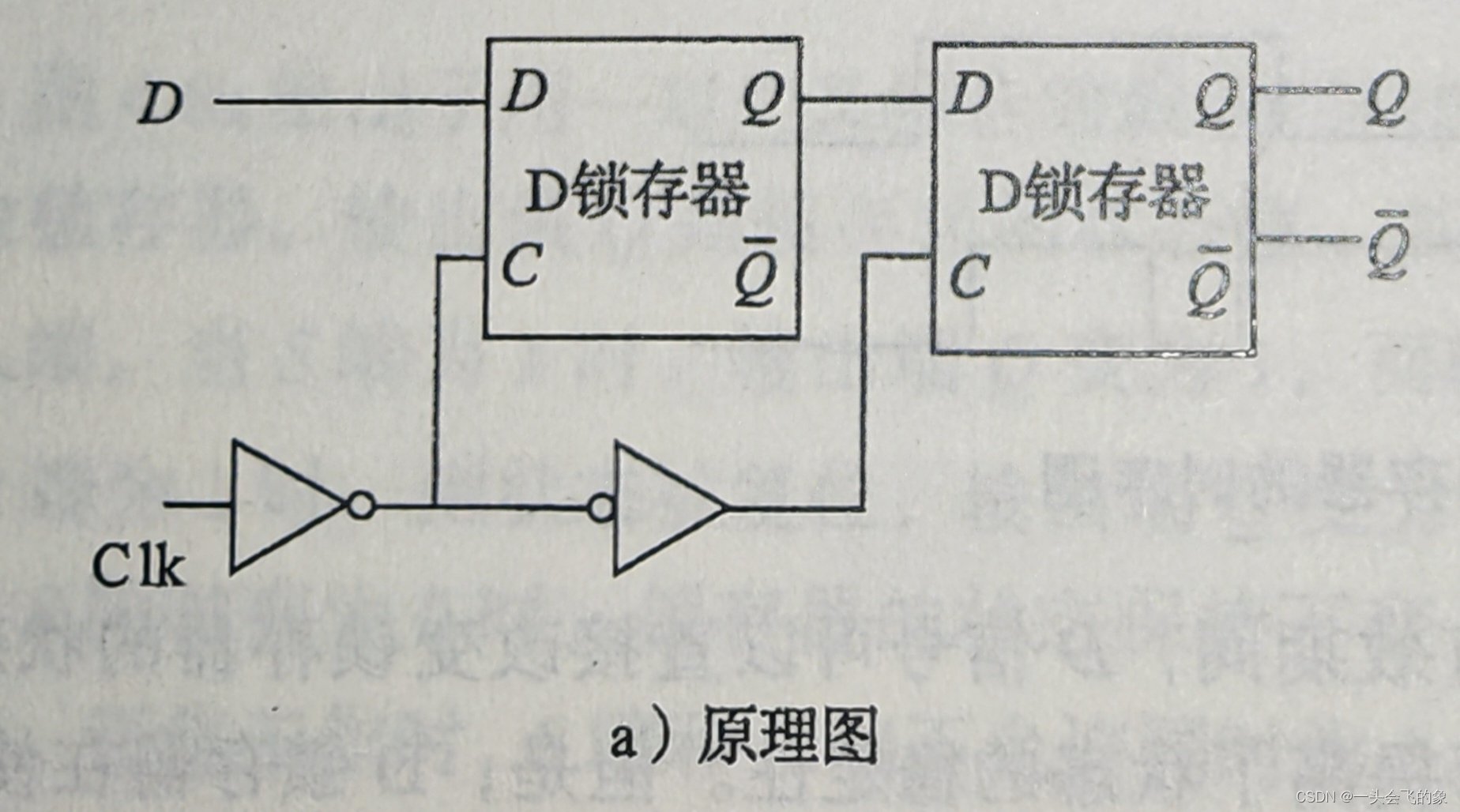

D型触发器的电路图由两个D锁存器构成,下图为D锁存器电路原理图。

D型触发器的电路原理图如下图所示,

(三)D型触发器的特性

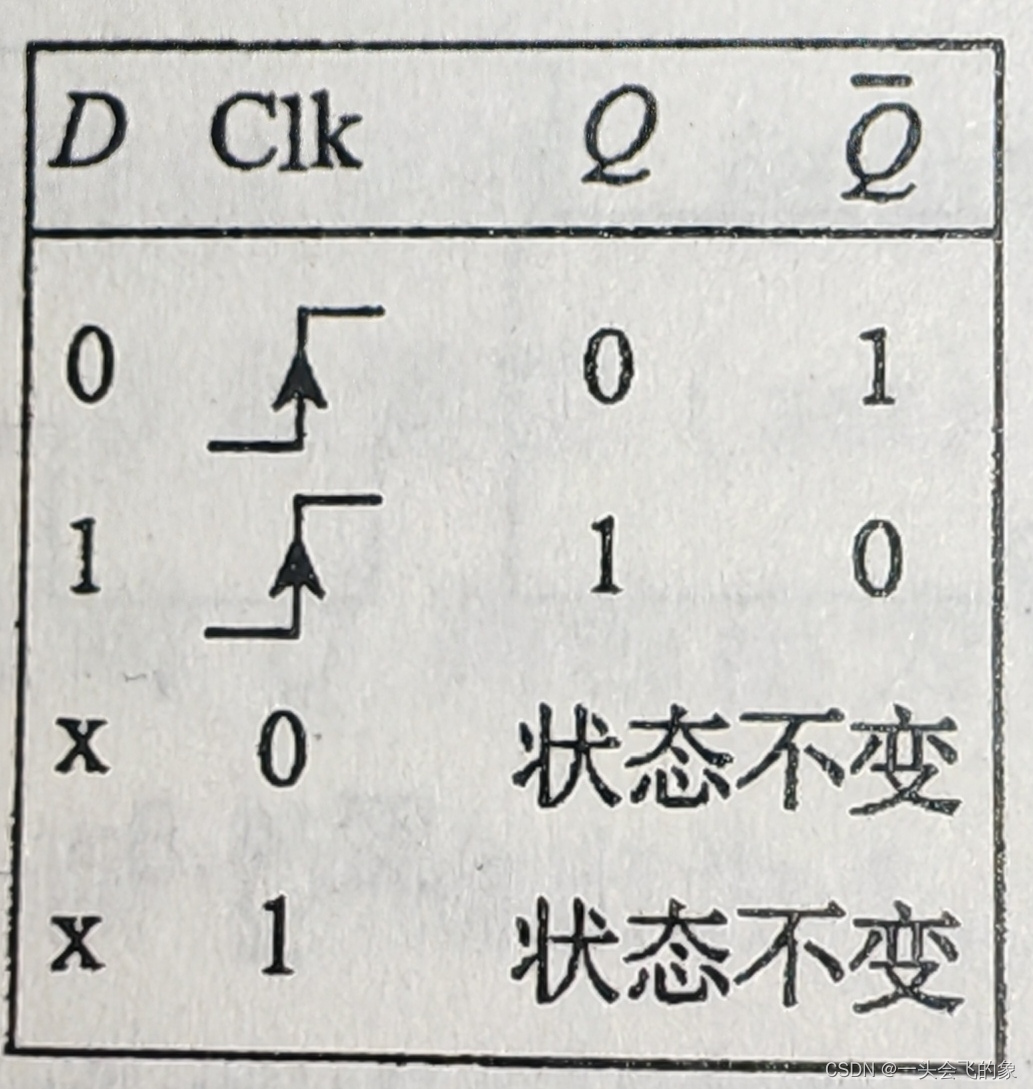

D型触发器真值表

对于D触发器,存在以下规律:

Clk=1时,主锁存器(左端的锁存器)输出端Q会与输入端D信号变化一致,而从锁存器(右边的锁存器)处于闭状态,故总输出Q保持不变。

Clk由高电平变为低电平时,主锁存器(左边的锁存器)锁存当前D的状态,传递至中间输出Q并保持不变。而从锁存器现在处于开状态,即最终输出Q与中间输出Q的状态保持一致。即最终输出Q输出的状态与输入D一致。

综上所述,D触发器最终输出Q只会在时钟Clk电平下降时,对D端进行信号的锁存,其余时间输出端信号具有保持的功能。

(四)D型触发器的仿真及验证

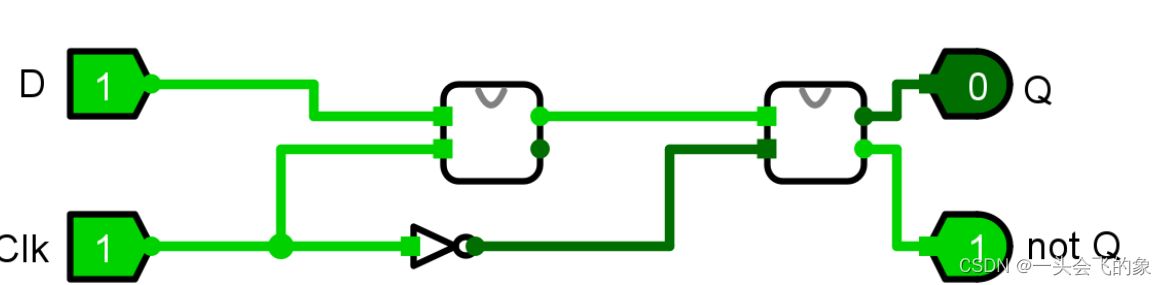

将D锁存器封装之后,最后得到D型触发器的仿真。

利用实验器材进行验证,如下图

4244

4244

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?