一种序列信号发生器设计,周期性进行输出。

目录

一、序列发生器

序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号,能产生这种信号的逻辑器件则称为序列发生器。在设计中有些时候会需用使用某些非常特殊的数字信号,一般情况下就将这种特殊的串行数字信号称作序列信号。

序列信号发生器的设计方法有多种,例如:

(1)环形计数器型序列信号发生器

(2)扭环计数器型序列发生器

(3)其他任意类型的序列发生器,例如:D触发器实现序列发生器、使用计数器和多路复用器实现序列发生器、使用移位寄存器和反馈组合电路实现序列发生器等。

从结构上,一般可以分为反馈移位型和计数型两种:

(1)移位型:移位型序列信号发生器是由移位寄存器和组合电路两部分构成。组合电路的输出作为移位寄存器的串行输入。由n位移位寄存器构成的序列信号发生器所产生的序列信号的最大长度为:P=2n。

(2)计数型:计数型序列信号发生器能产生多组序列信号,这是移位型发生器所没有的功能。一般把凡具有测频和测周两种以上功能的计数器都归类为通用计数器,而序列发生器就是产生一系列特定的信号的仪器。

二、代码实现

一般情况会选择移位型来实现,会比较简单。

上代码:

module sequence_gen(

input clk,

input rst_n,

input en,

input [7:0] din,

output reg dout_lsb,

output reg dout_msb

);

reg [7:0] tmp_lsb;

reg [7:0] tmp_msb;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

dout_lsb <= 1'b0;

tmp_lsb <= 8'b0;

end

else if(en)begin

dout_lsb <= dout_lsb;

tmp_lsb <= din;

end

else begin

dout_lsb <= tmp_lsb[0];

tmp_lsb <= tmp_lsb >> 1;

tmp_lsb[7] <= dout_lsb;

end

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

dout_msb <= 1'b0;

tmp_msb <= 8'b0;

end

else if(en)begin

dout_msb <= dout_msb;

tmp_msb <= din;

end

else begin

dout_msb <= tmp_msb[7];

tmp_msb <= tmp_msb << 1;

tmp_msb[0] <= dout_msb;

end

end

endmodule这是一位的序列发生器,分为了从最低位开始和从最高位开始两种。

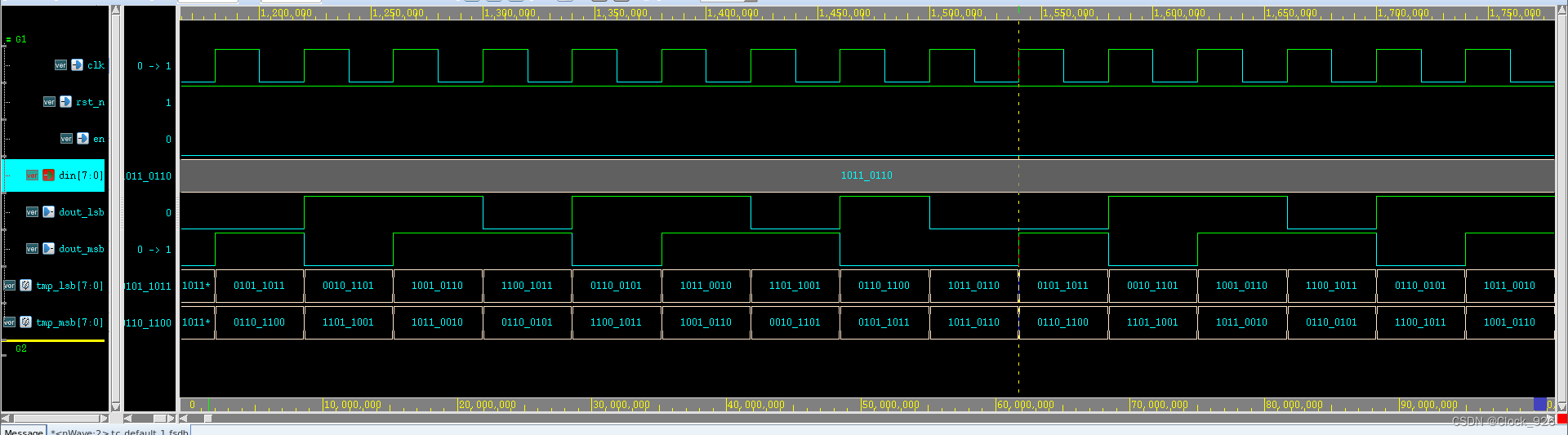

测试波形,周期性输出1011_0110:

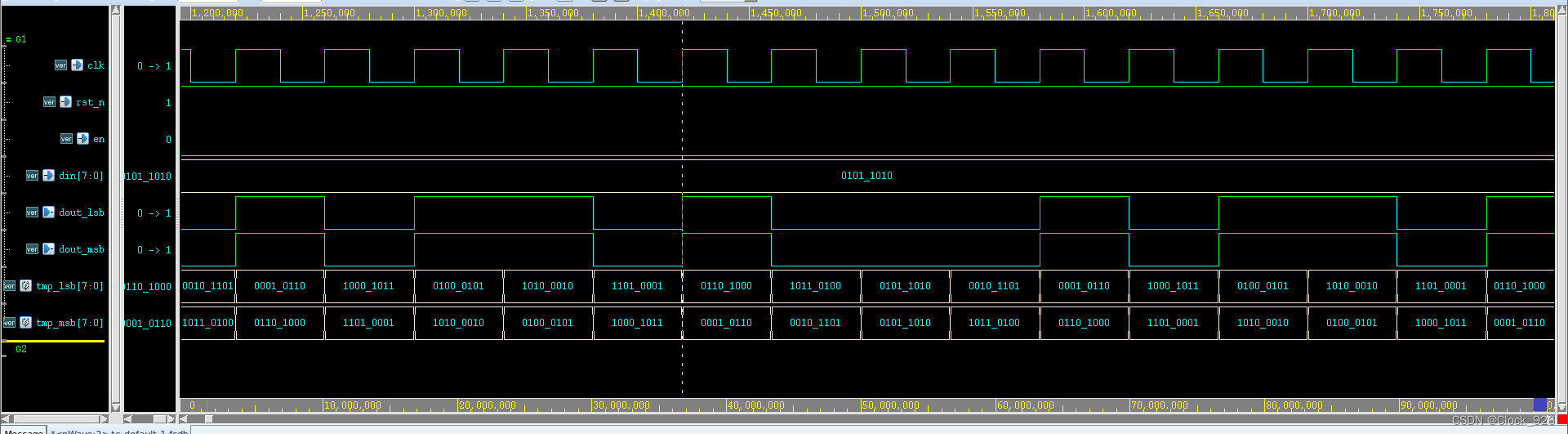

测试波形,周期性输出0101_1010:

华为曾有一道手撕代码的题:循环序列的产生,请写出产生0123456776543210的循环输出序列;思路也是类似的。

module gen(

input clk,

input rst_n,

output reg [3:0] dout

);

reg [63:0] tmp;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

dout <= 4'b0;

tmp <= 64'h0123456776543210;

end

else begin

dout <= tmp[63:60];

tmp <= tmp << 4;

tmp[3:0] <= dout;

end

end

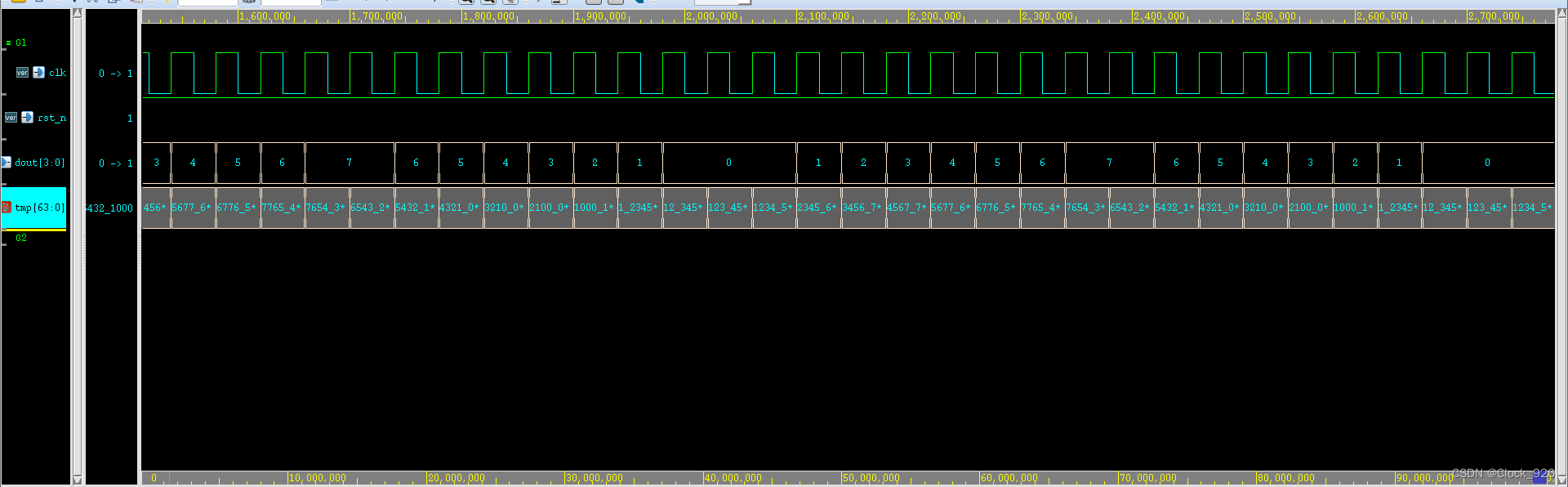

endmodule测试波形:

5342

5342

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?