一个简单的除法器设计。

目录

一、除法器概述

除法器即实现除法运算的逻辑电路。相比于乘法器和全加器,除法器的设计要稍微复杂一些。

除法运算过程如下:

(1) 取被除数的高位数据,位宽和除数相同。

(2) 将被除数高位数据与除数作比较,如果前者不小于后者,则可得到对应位的商为 1,两者做差得到第一步的余数;否则得到对应的商为 0,将前者直接作为余数。

(3) 将上一步中的余数与被除数剩余最高位 1bit 数据拼接成新的数据,然后再和除数做比较。可以得到新的商和余数。

(4) 重复过程 (3),直到被除数最低位数据也参与计算。

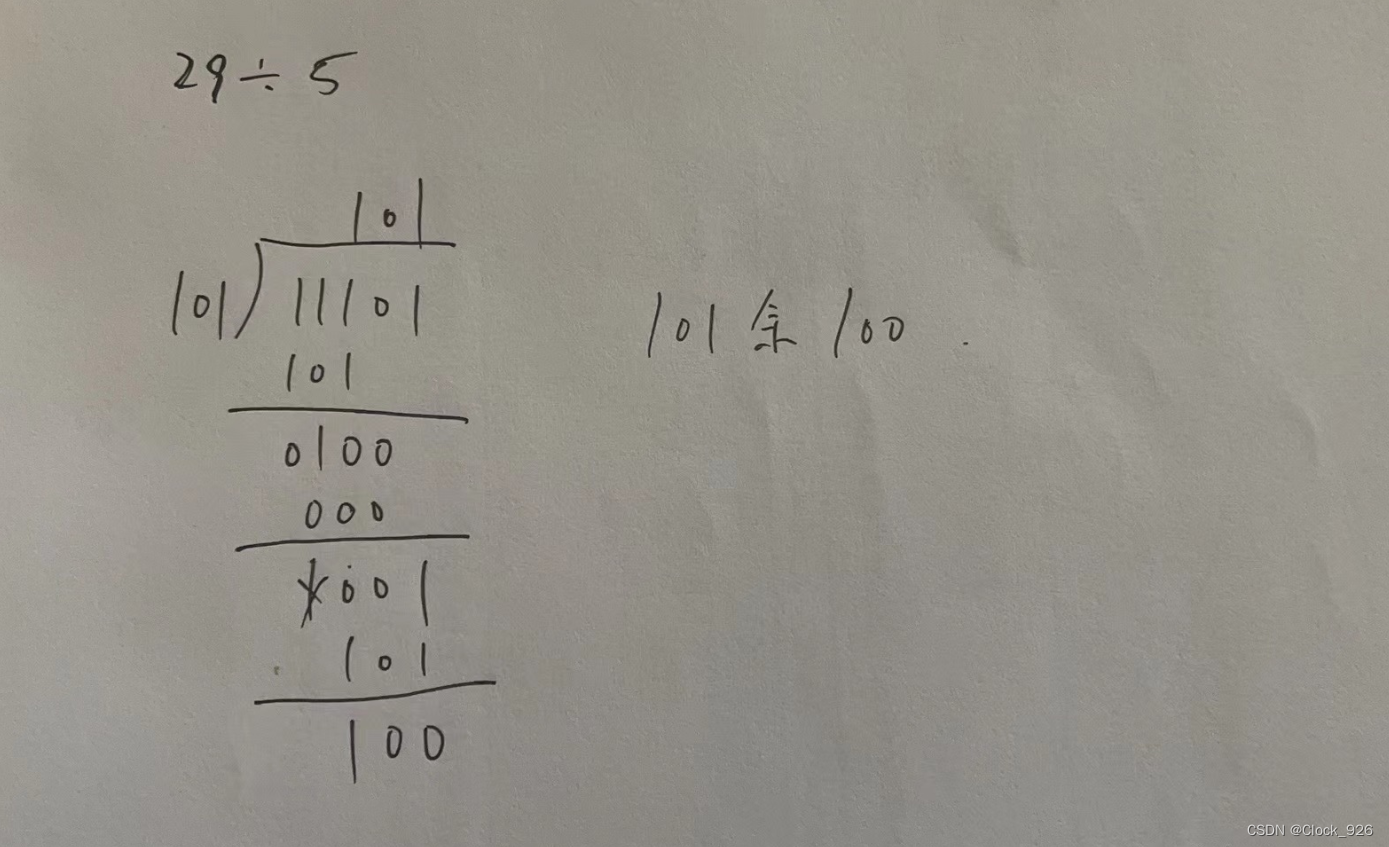

例如29➗5,计算过程:

二、代码实现

上代码:

module divider(

input clk,

input rst_n,

input [15:0] ain,

input [7:0] bin,

output reg [15:0] cout,

output reg [15:0] rem

);

integer i;

reg [15:0] a_reg;

reg [7:0] b_reg;

reg [31:0] tmp_a;

reg [31:0] tmp_b;

always@(*)begin

a_reg = ain;

b_reg = bin;

end

always@(*)begin

tmp_a = {16'h0, a_reg};

tmp_b = {b_reg, 16'h0};

for(i=0;i<16;i=i+1)begin

tmp_a = tmp_a << 1;

if(tmp_a >= tmp_b)begin

tmp_a = tmp_a - tmp_b +1;

end

else begin

tmp_a = tmp_a;

end

end

assign cout = tmp_a[15:0];

assign rem = tmp_a[31:16];

end

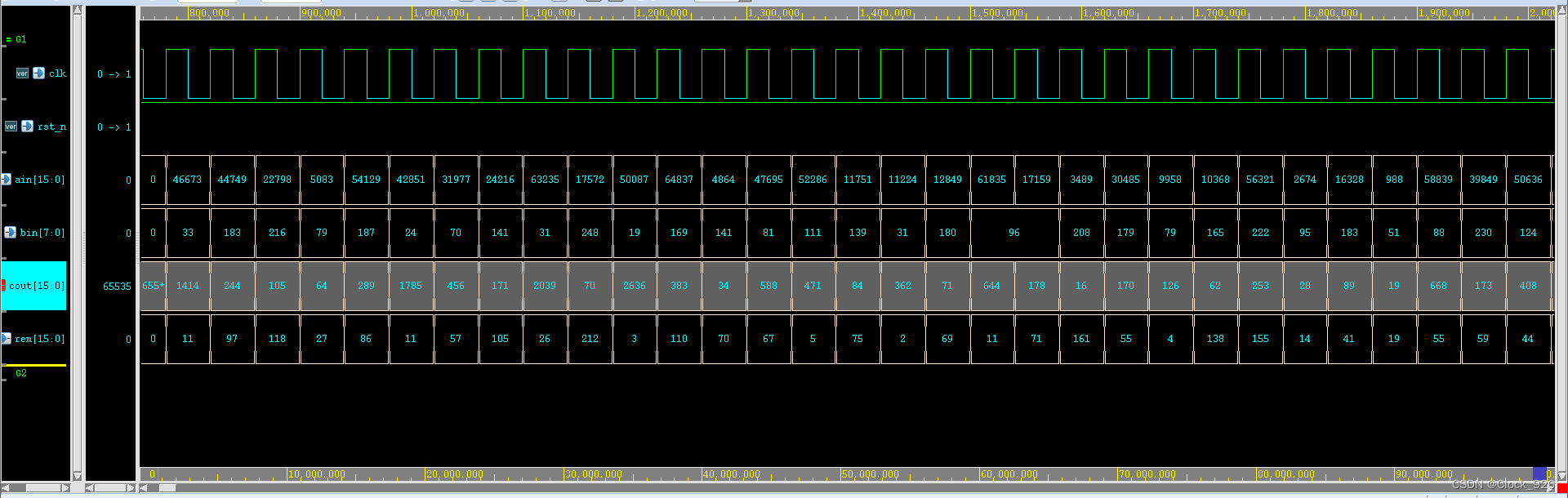

endmodule测试波形:

为了方便观察结果以十进制显示。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?