前言

参考书籍:《Verilog HDL 数字设计与综合》第二版,本文档为第10章的学习笔记。

本章将探讨Verilog中如何控制和定义时序

学习目标

- 了解分布延迟、集总延迟和路径延迟

- specify关键字设置路径延迟

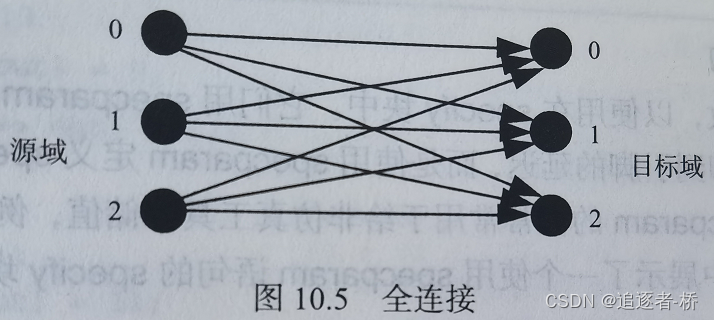

- 输入输出引脚间的并行连接和全连接

- specify块中用specparam语句定义参数

- 条件路径延迟(状态依赖路径延迟)

- rise、fall和turn-off延迟,理解如何设置min、max和typ值

- 为时序检查定义系统任务,$setup, $hold, $width

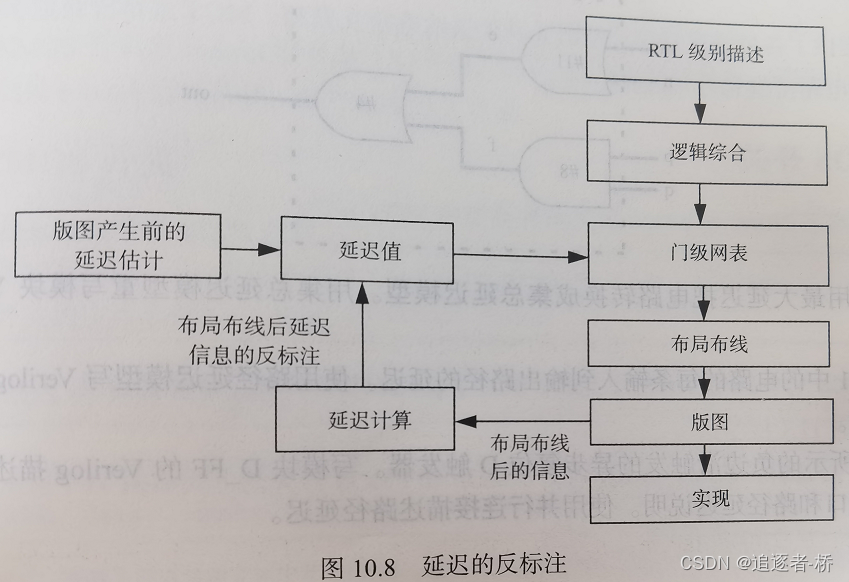

- 理解延迟反标

10.1 延迟模型的类型

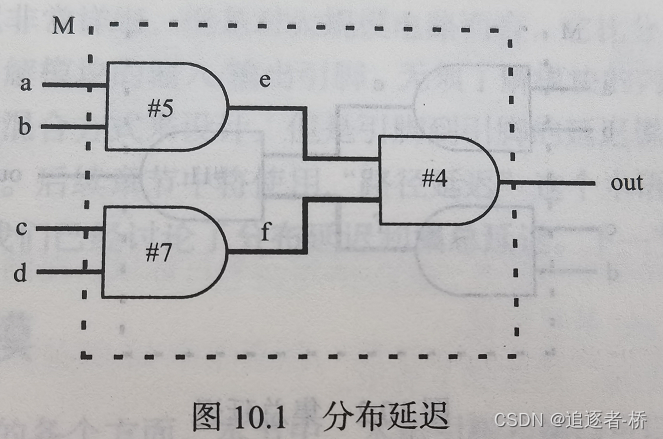

1、分布延迟

在每个独立元件的基础上进行定义,在每条语句上添加延迟#,两种建模方式:一种是将延迟赋值给独立的门;另一种是在单独的assign语句中指定延迟值。

and #10 a1(out, in1, in2); assign #10 e = a & b;

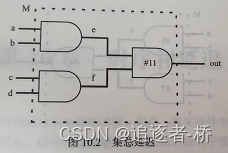

2、集总延迟

在每个独立模块的基础上定义的,将整个电路的最大延迟作用于最后的输出门延迟上。

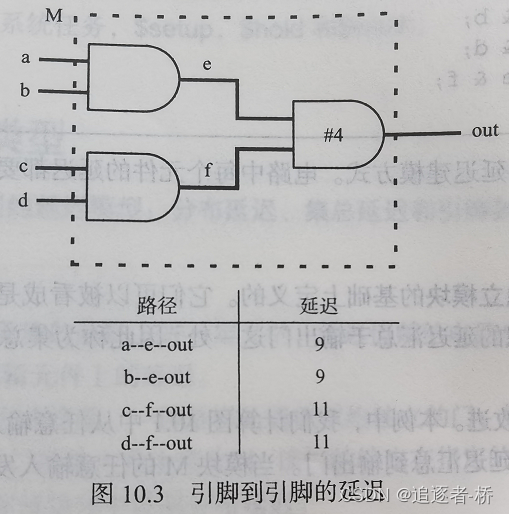

3、路径延迟

引脚到引脚的时序说明

10.2 路径延迟建模

10.2.1 specify块

关键字specify和endspecify之间给路径延迟赋值,块中不能包含其他块(initial、always)等。

- 给穿过模块的所有路径指定引脚到引脚的时序延迟

- 在电路中设置时序检查

- 定义specparam常量

//引脚到引脚的延迟

specify

(a => out) = 9;

(b => out) = 9;

(c => out) = 11;

(c => out) = 11;

endspecify10.2.2 specify块内部

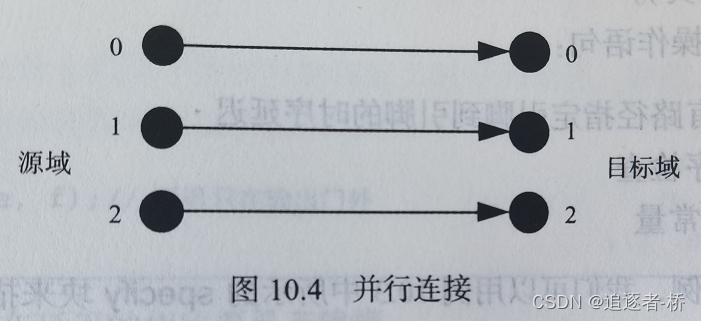

并行连接

用法:(<source_field> => <destination_field>) = <deay_value>;

<source_field>和<destination_field>的位宽必须相同

全连接

用法:(<source_field> *> <destination_field>) = <deay_value>;

每一个源域都要和目标域连接,因此位数可以不同。

specify

(a,b *> out) = 9;

(c,d *> out) = 11;

endspecify边沿敏感路径

(posedge clock => (out +: in))= (10:8); 上升延迟10,下降延迟8

specparam声明语句

在specify块内定义参数常量

specify

specparam d_to_q = 9;

(d => q) = d_to_q ;

endspecify条件路径延迟

条件表达式可以包含任意逻辑操作符、位操作符等,if语句中不能使用else结构。条件路径延迟又称状态依赖路径延迟(SDPD)。

specify

if(a) (a => out) = 9;

if(a & b) (b => out) = 9;

if({c,d} == 2'b01) (c,d *> out) = 11;

endspecify上升、下降和关断延迟

//上升延迟0->1, z->1

//下降延迟1->0, z->0

//关断延迟0->z, 1->z

specparam t-rise=9, t_fall = 13, t_turnoff = 11;

(clk => q) =(t-rise, t_fall, t_turnoff);最小最大和典型延迟值

表达形式:“min:type:max”

specparam t-rise=8:9:10, t_fall = 12:13:14, t_turnoff = 10:11:12;

(clk => q) =(t-rise, t_fall, t_turnoff);处理x状态转换

10.3 时序检查

指定路径延迟的目的是以比门延迟更高的精度仿真实际数字电路的时序。通过系统任务:$setup , $hold , $width。所有时序检查只能用在specify块里

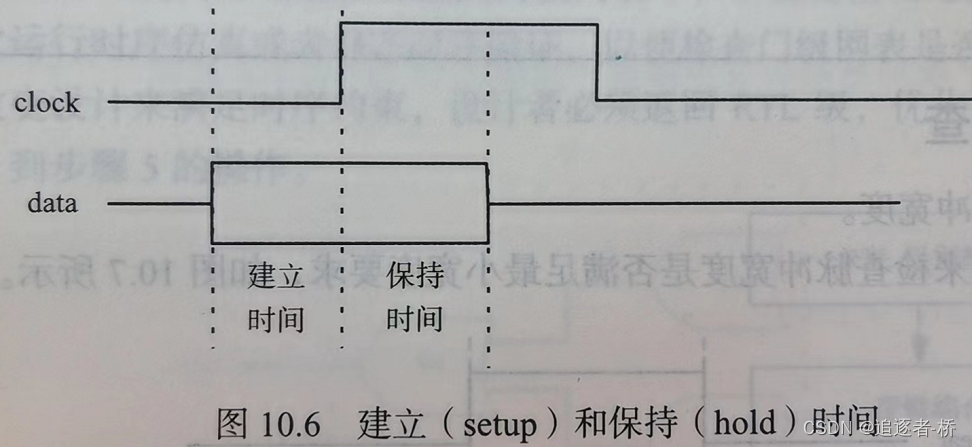

10.3.1 $setup和$hold检查

用来检查设计中时序元件的建立和保持约束。在时序元件(如边沿触发器)中,建立时间是数据必须在有效时钟边沿之前到达的最小时间,保持时间是数据在有效时钟边沿之后保持不变的最小时间。

$setup

//设置时间检查

//clock作为参考信号,data是被检查的信号

//如果(Tposedge_clk - Tdata) < 3,则报告违反约束

specify

$setup(data, posedge clock, 3);

endspecify$hold

//设置时间检查

//clock作为参考信号,data是被检查的信号

//如果(Tdata - Tposedge_clk) < 5,则报告违反约束

specify

$hold(posedge clock, data, 5);

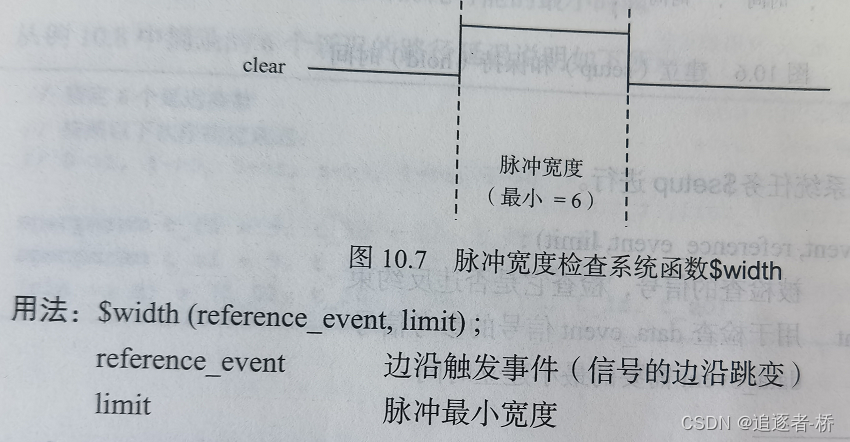

endspecify10.3.2 $width检查

检查脉冲宽度是否满足最小宽度要求

//设置宽度检查

//clock的上升沿正跳变作为reference_event

//clock的下一个下降沿负跳变作为data_event

//如果(Tdata - Tclk) < 6,则报告违反约束

specify

$width(posedge clock, 6);

endspecify

1220

1220

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?