使用Quartus13进行VHDL工程的编写与仿真

徐晓峰

2021.4.19

编写代码

-

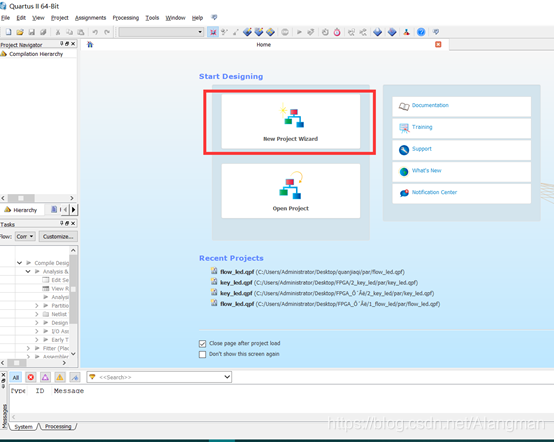

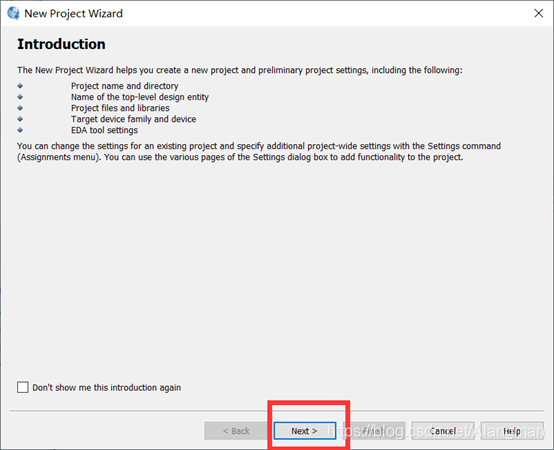

点击新建一个工程

-

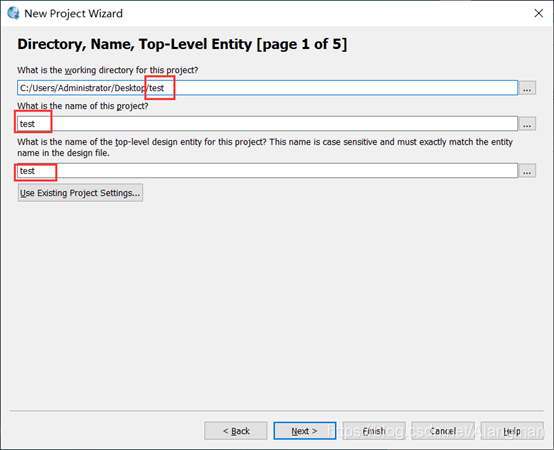

选择工程保存的路径,填写工程名称,注意,三个圈起来的应该相同

-

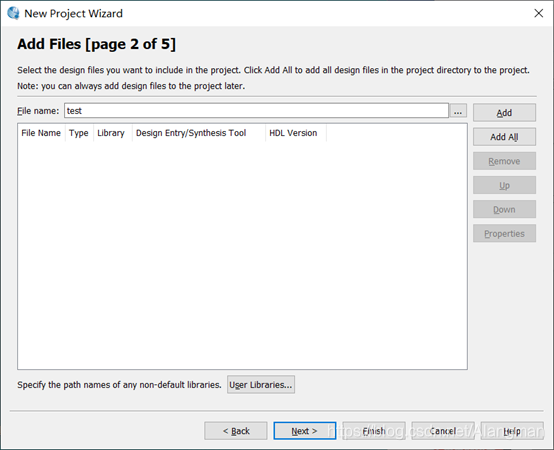

与上一步的文件名也相同;

-

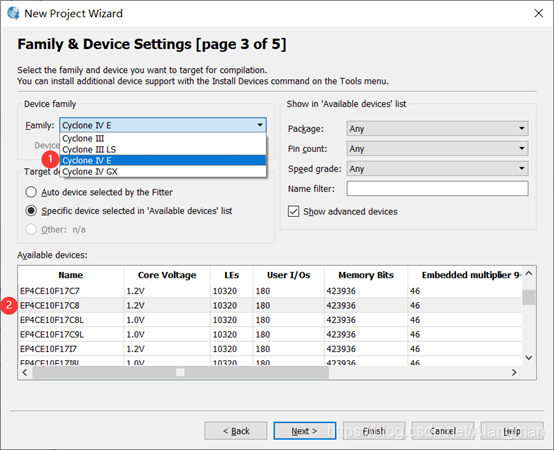

选择设备类型,一定要进行选择,否则后面编译仿真时可能会出错

我们使用的开发板芯片为EP4CE10F17C8

-

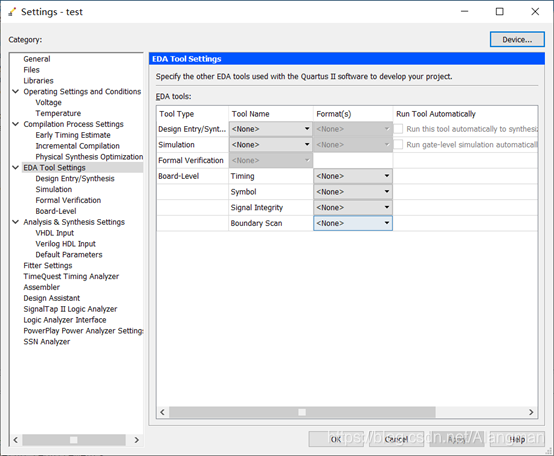

EDA Tools Settings中的仿真工具选择None,不需要自动进行波形仿真。

-

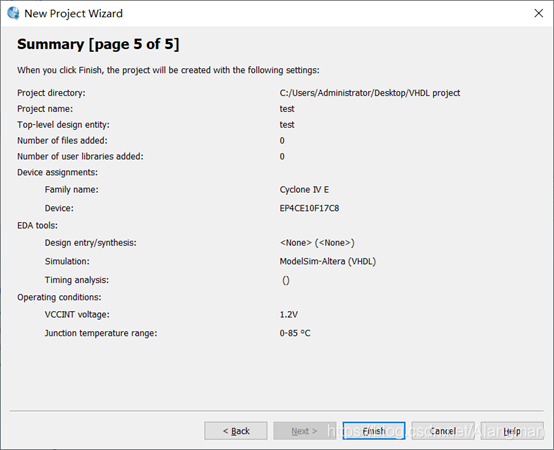

点击Finish

-

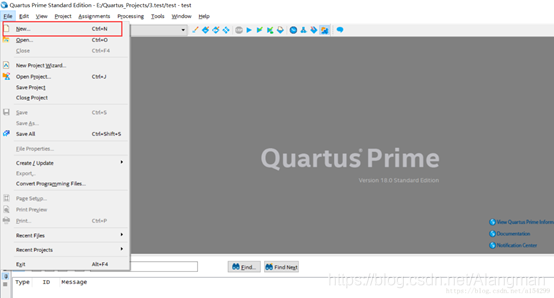

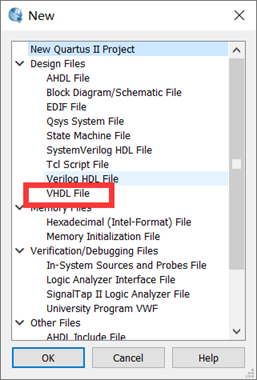

点击新建文件,选择 vhdl file

-

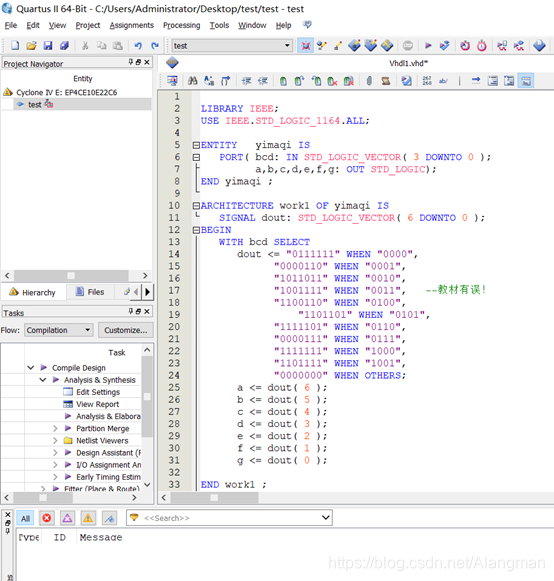

编写vhdl语言程序,以我们上次实验做的七段显示译码器为例(注意文件名和器件名一定要一致)

附上本次实验的实验代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY yimaqi IS

PORT( bcd: IN STD_LOGIC_VECTOR( 3 DOWNTO 0 );

a,b,c,d,e,f,g: OUT STD_LOGIC);

END yimaqi ;

ARCHITECTURE work1 OF yimaqi IS

SIGNAL dout: STD_LOGIC_VECTOR( 6 DOWNTO 0 );

BEGIN

WITH bcd SELECT

dout <= "0111111" WHEN "0000",

"0000110" WHEN "0001",

"1011011" WHEN "0010",

"1001111" WHEN "0011", --教材有误!

"1100110" WHEN "0100",

"1101101" WHEN "0101",

"1111101" WHEN "0110",

"0000111" WHEN "0111",

"1111111" WHEN "1000",

"1101111" WHEN "1001",

"0000000" WHEN OTHERS;

a <= dout( 6 );

b <= dout( 5 );

c <= dout( 4 );

d <= dout( 3 );

e <= dout( 2 );

f <= dout( 1 );

g <= dout( 0 );

END work1 ;

-

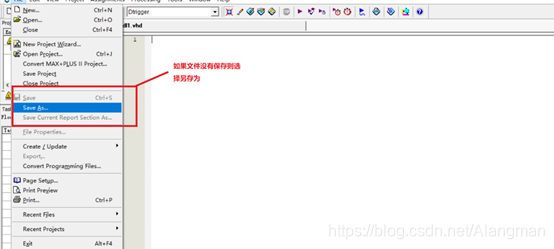

如果刚刚新建的VHDL没有保存,可以再File里选择另存为;

-

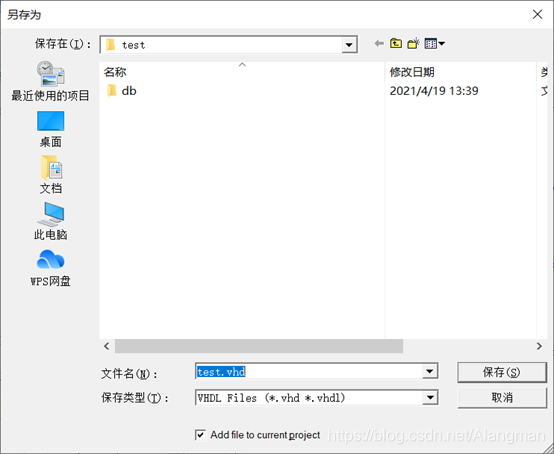

VHDL文件名和工程名相同;

-

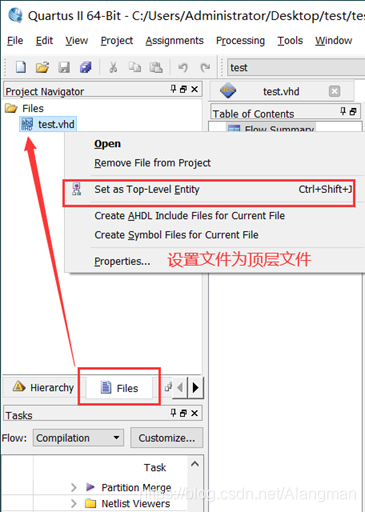

右键单击将写好的文件设置为顶层文件

-

点击编译,没有报错即VHDL文件编写成功

-

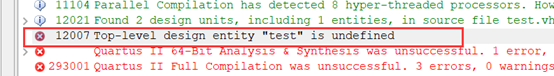

如出现以下内容,是因为项目名称叫做test,但是找不到这个名称叫test。顶级模块的名称必须与项目名称一致。

-

故更正程序如下所示

生成部件

-

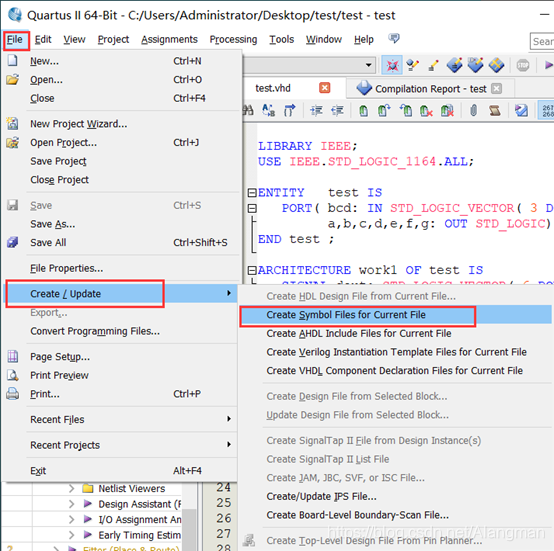

将刚才的vhdl文件生成为部件,并用它进行画图,进行如下操作:

-

点击 File->Create/Update->Create symbol files for current file,没有报错即可

生成顶层图

-

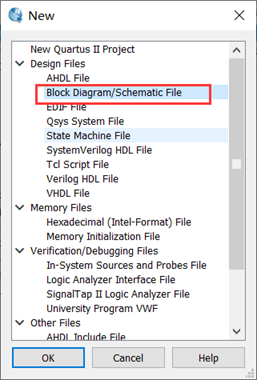

如果你想用上面的部件画一个顶层图,那么就新建一个Block Diagram/Schematic File

-

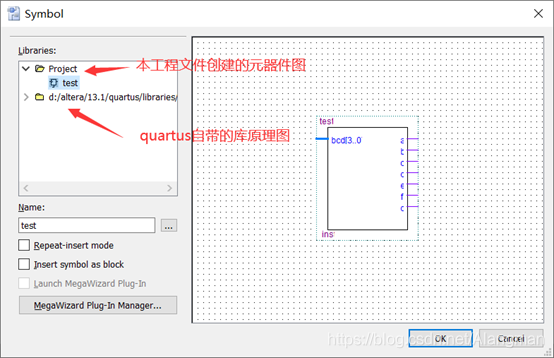

双击空白处可调出Symbol界面,在这里可以看到自己工程文件生成的部件

-

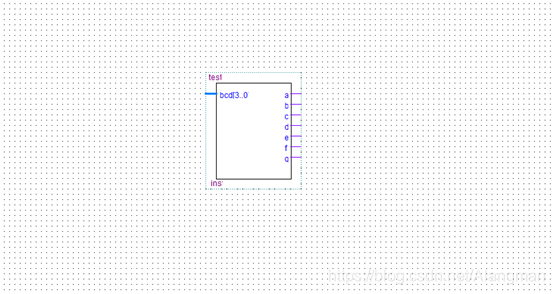

选中后点击OK即可放置在原理图上,然后进行保存即可。

仿真测试

-

对生成的部件进行仿真测试,则进行如下操作:

-

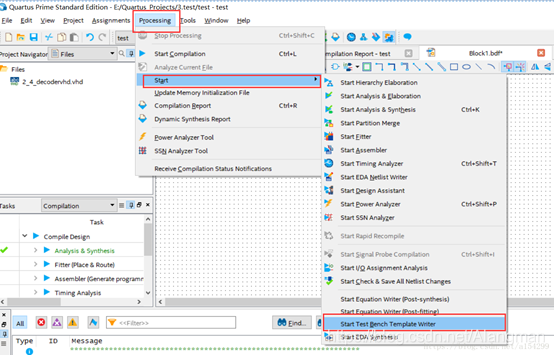

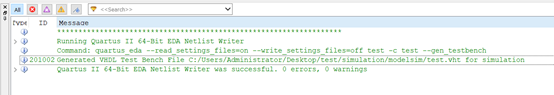

点击Processing->Start->Start Test Bench Template Writer,没有报错即可

-

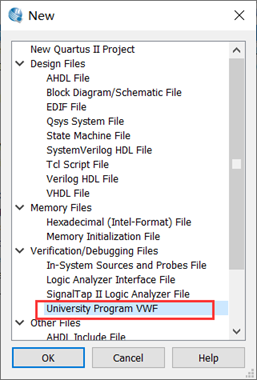

新建一个University Program VWF文件

-

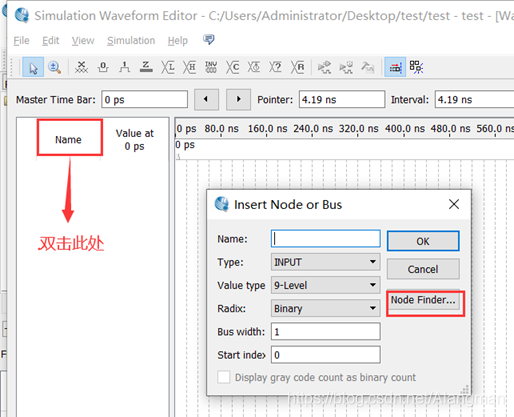

双击左侧空白处,可调出Insert Node or Bus窗口

-

点击list按钮就会显示出Entity(实体)定义的所有变量,之后全部导入即可;

-

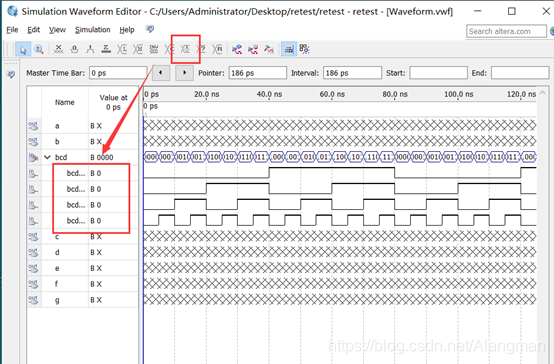

分别给四个输入信号加上激励波形,分别为10、20、40、80,满足BCD码条件

-

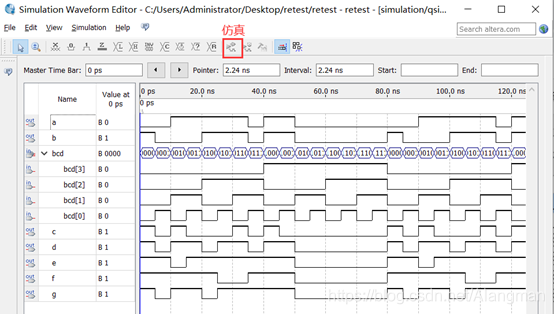

保存后点击Run Functional Simulation,稍等即可弹出仿真后的界面

-

【注】此处仿真不出图,很麻烦,需要新建仿真库https://blog.csdn.net/u013753393/article/details/50350138<> 参考本文

-

另一简便途径是,下载ModelSim-Altera。附上下载链接:https://pan.baidu.com/s/16nEjS6Tx1NHKpU_e4ale1g 提取码:1234

-

【注】想对哪个文件进行仿真,就需将哪个文件设置为顶层文件,并进行组建编译,然后重新建立一个VWF文件。

这样一个编写代码->生成部件->生成顶层图->仿真测试的流程就完成了。

下一篇:如何将写的程序下入正点原子_新起点开发板

2123

2123

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?