文章目录

一、基本概念

1. 数电中关于时序逻辑电路的分类

时序逻辑电路通常可按电路的状态变化特点或电路的输出信号特点进行分类。

- 按照电路的状态变化特点可分为:同步时序逻辑电路和异步时序逻辑电路。

- 按照电路的输出信号特点可分为:Mealy型时序逻辑电路和Moore型时序逻辑电路。

2.Mealy型电路和Moore型电路的区别

-

Moore型:Moore型电路的输出只是状态函数,输出表达式中不含输入变量,输入改变时,输出并不变化;只在输入改变,且时钟出现后,由状态的改变引起输出发生改变。

-

Mealy型:Mealy型电路的输出是输入和现态的函数,当输入改变时,输出随之改变,尽管电路状态可能由于时钟未出现而未改变。Mealy型电路输入改变,输出随之改变的特性,一方面使得Mealy型电路的输出能对输入改变做出快速响应,但另一方面又使Mealy型电路的输出序列中可能出现短暂的多余脉冲。

-

Moore型电路比Mealy型电路滞后一个时钟周期,而对同一功能的Moore型电路和Mealy型电路,它们的输出序列本身是相同的,只是Mealy型电路比Moore型电路的输出序列超前一个时钟周期出现

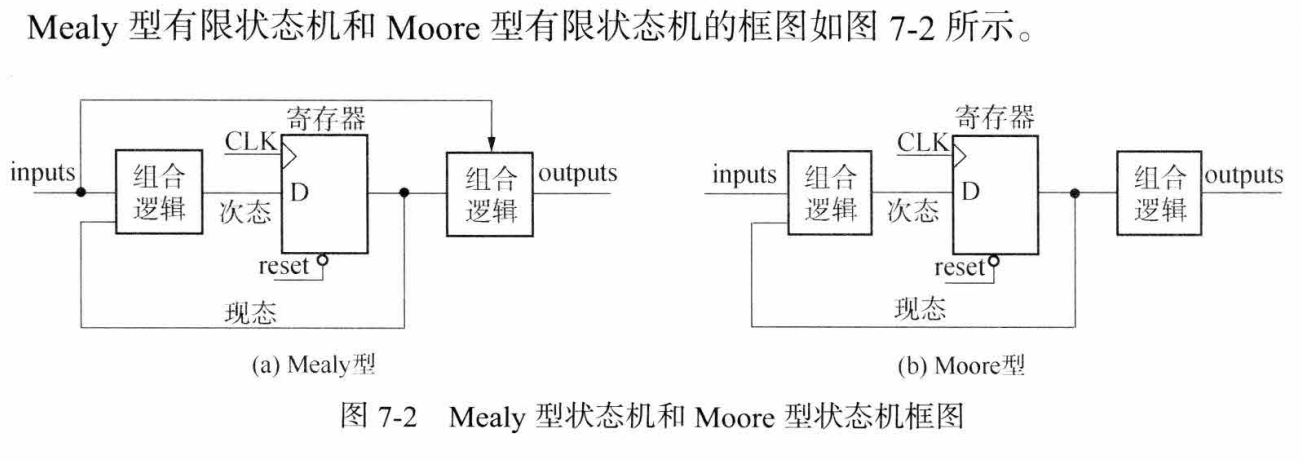

3.Mealy型有限状态机和Moore型有限状态机的框图

- 如图(a) Mealy型:输出是外部信号和电路状态的函数。

- 如图(b) Moore型:输出只是电路状态的函数。

二、一个简单的序列检测:可重叠,不可重叠的Mealy型和Moore型状态图

如题:画出101序列检测的状态图,凡收到输入序列101时,输出为1;

输入序列为:010101101

可重叠输出序列为 :000101001

不可重叠输出序列为:000001001

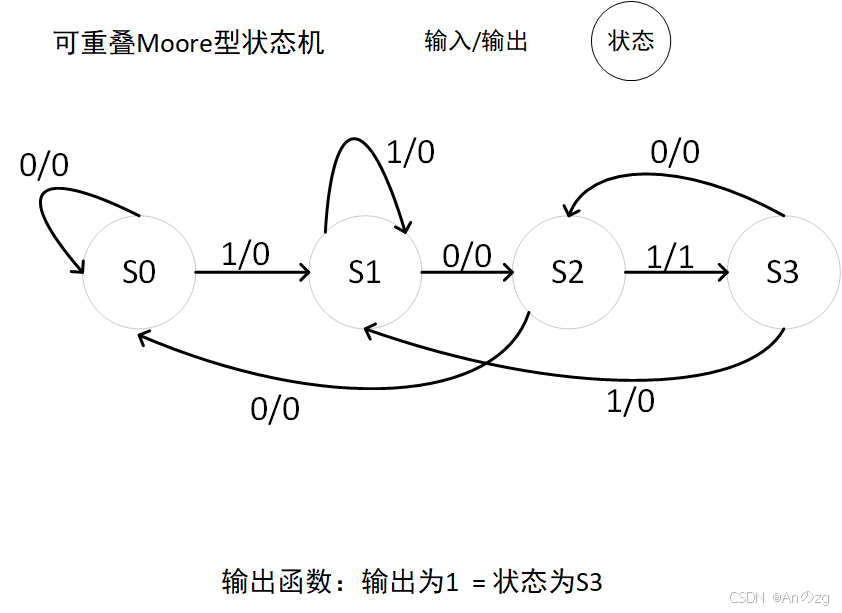

1.可重叠的Moore型状态图

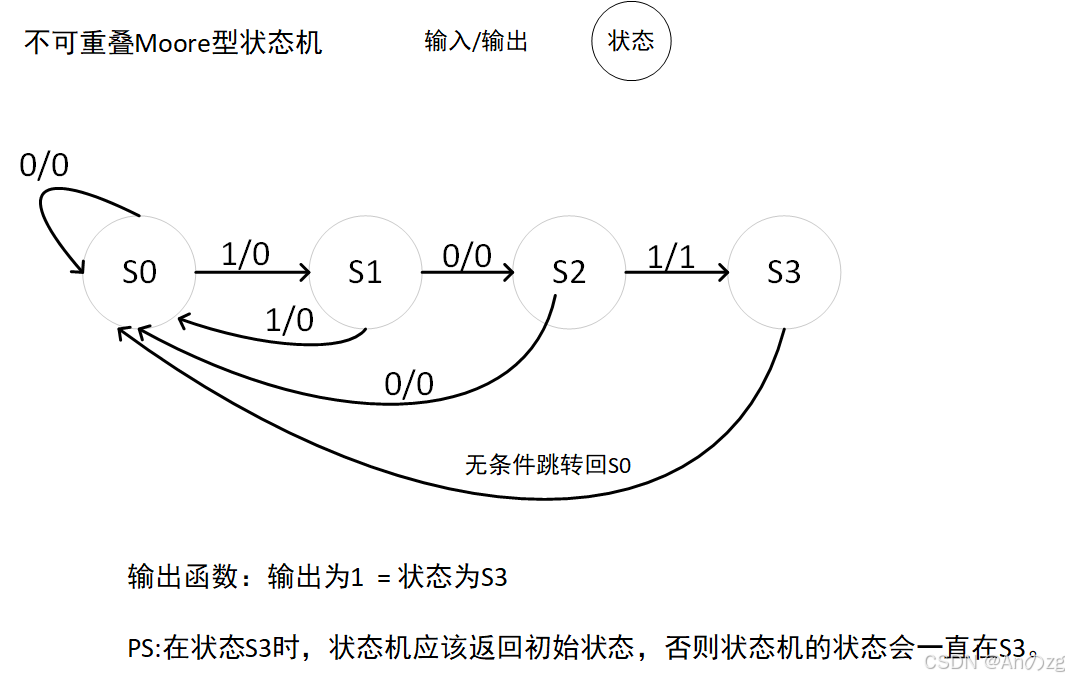

2.不可重叠的Moore型状态图

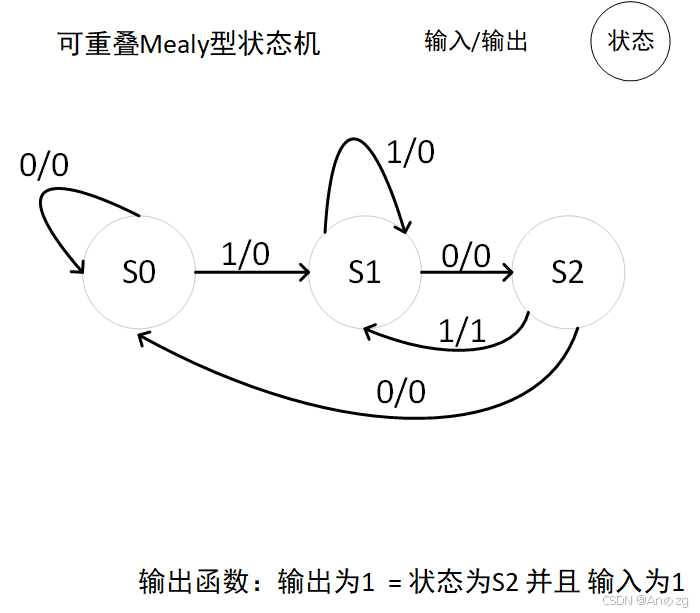

3.可重叠的Mealy型状态图

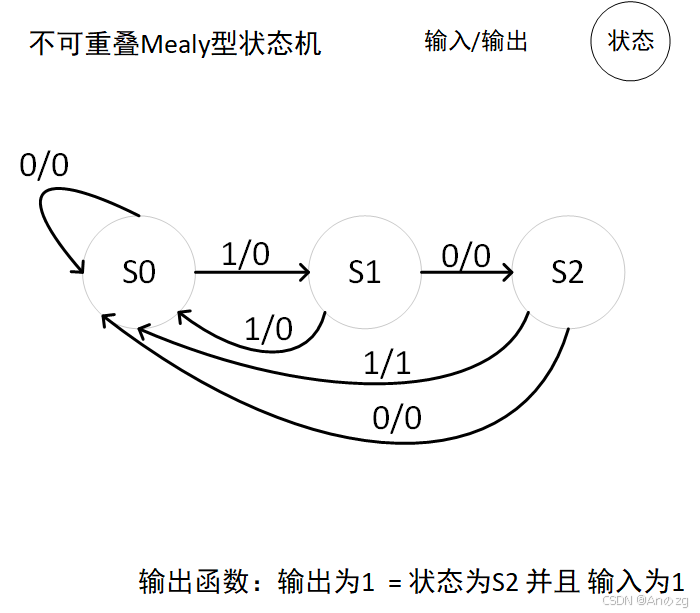

4.不可重叠的Mealy型状态图

下篇博文介绍:基于Verilog RTL代码实现状态机的序列检测

Verilog-实现基于状态机的序列检测–一段式状态机、二段式状态机、三段式状态机

本篇随笔为学习记录所用,如有错误,请各位指正批评。

1844

1844

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?