基本概念

- 数字电路分为

组合逻辑电路和时序逻辑电路。 - 逻辑门电路的基本器件:电子开关(如二极管、三极管)— 时而导通,时而截止,构成电子开关。

- SoC(System on Chip)片上系统:将电子系统中所有不同的功能块集成在一个芯片中。

- ASIC(Application Specific Integrated Circuit)专用集成电路:根据用户特定要求和电子系统的特定需要而设计制造的专用集成电路。

- ASIC芯片的制作可以采用全定制或半定制的方法:

- 全定制:适用于生产批量的成熟产品,由半导体生产厂家制造;

- 半定制:适用于生产批量小或研究试制阶段的产品;

- 目前最为流行的半定制方法:

- 复杂可编程逻辑器件(Complex Programmable Logic Device)CPLD

- 现场可编程门阵列(Field Programmable Gate Array)FPGA

- 用户通过软件编程,将自己的设计的数字系统制作在厂家生产的CPLD或FPGA芯片上,便得到所需的系统级芯片。

- SoC芯片的设计方法进一步分工细化,出现IP (Intellectual Property) 设计和SoC系统设计。

- IP:内核模块,一种已经过验证的、可重利用的、具有某种确定功能的模块。

- 衡量集成电路的两个主要参数:集成度和特征尺寸。

- 集成度:每一个芯片所包含的门的个数。

- 特征尺寸:集成电路中半导体器件加工的最小线条宽度。

- 关系:芯片面积一定时,集成度越高, 特征尺寸就越小。

- 从集成度角度来分类:小规模(SSI)、中规模(MSI)、大规模(LSI)、超大规模(VLSI)、甚大规模(ULSI)

| 分类 | 门的个数 | 典型集成电路 |

|---|---|---|

| 小规模 | 最多12个 | 逻辑门、触发器 |

| 中规模 | 12~99 | 逻辑门、触发器 |

| 大规模 | 100~9999 | 逻辑门、触发器 |

| 超大规模 | 10000~99999 | 逻辑门、触发器 |

| 甚大规模 | 106以上 | 逻辑门、触发器 |

- 逻辑门:数字集成电路的主要单元电路,按照结构和工艺分为双极型、MOS型和双极—MOS型。

- TTL:(Transistor-Transistor Logic)三极管-三极管型(现已逐渐被CMOS替换)。

- CMOS:(Complementary Metal-Oxide-Semiconductor)金属-氧化物-半导体。

数字集成电路特点

- 相较于模拟电路,优点如下:

- 稳定性高,抗干扰能力强;

- 易于设计;

- 便于集成,成本低廉;

- 可编程性;

- 高速度,低功耗;

- 便于存储、传输和处理

数字电路的分析方法

- 数字电路分析方法:

- 主要研究对象:电路的输入输出逻辑关系;

- 分析工具:逻辑代数;

- 表达输入输出关系:真值表、功能表、逻辑表达式或波形图;

- 电子设计自动化(Electronic Design Automation,EDA)工具,可以用于模拟电路、数字电路或模数混合电路仿真分析。

数字电路的设计方法

- 从给定的逻辑功能要求出发,确定输入、输出变量,选择适当的逻辑器件,设计出符合要求的逻辑电路。

- 设计过程:提出、验证、修改(三个阶段)

- 设计方法:传统的设计方式和基于EDA软件的设计方式。

EDA软件工具

- 原理图输入:设计者可以如同在纸上画电路一样,将逻辑电路图输入到计算机,软件自动检查电路的连线、电源及地线的连接、信号的连接等。

- HDL文本输入:硬件描述语言是用文本的形式描述硬件电路的功能、信号连接关系以及时序关系。常用的HDL语言有VHDL(Very High Speed Integrated Circuit) 和Verilog HDL等。

- 测试平台:当逻辑电路的设计输入到计算机后,需要在测试平台上编写或绘制激励信号,以便测试验证电路逻辑功能或时序关系的正确性。

- 仿真和综合工具:

- 仿真工具:包括对电路的功能仿真和时序仿真。功能仿真用于验证电路的功能和逻辑关系是否正确。时序仿真考虑门及连线的延时,验证系统内部工作过程及输入输出的时序关系是否满足设计要求。

- 综合工具:将HDL描述的电路的逻辑关系,转换为门和触发器等元件及其相互连接的电路形式。

数字信号与模拟信号

- 模拟信号:时间、幅值连续变化的模拟量;

- 数字信号:时间、数值离散的信号。

- 由于计算机无法直接处理模拟信号,因此需要将模拟信号转换为数字信号。

数字信号的描述方法

- 数字信号用0、1两种值表示,二值数字逻辑(Binary Digital Logic);或者高、低电平组成的数字波形,即逻辑电平(Logic Level)表示。

- 数字电路的0和1组成的二进制数

- 表示数量的大小:可以进行数值运算,常称为算术运算;

- 表示两种不同的状态:描述客观世界存在的彼此相互关联又相互对立的事物,逻辑0和逻辑1(如是与非、真与假、开与关、低与高、通与断等)

- 二值数字逻辑(数字逻辑),以高、低电平分别表示逻辑1和逻辑0两种状态。

- 高电平:信号电压在3.5~5V范围内

- 低电平:信号电压在0~1.5V范围内

- 表示数字电压的高低电平通常称为逻辑电平,不是物理量,而是物理量的相对表示。

| 电压 | 二值逻辑 | 电平 |

|---|---|---|

| 3.5~5V | 1 | H(高电平) |

| 0~1.5V | 0 | L(低电平) |

数字波形

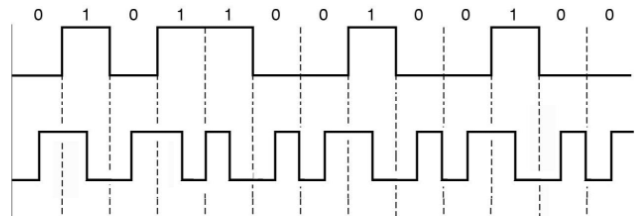

-

两种类型:非归零型,归零型。

- 一定时间间隔T,称为1位(bit),或者一拍

- 如果在一个时间拍内高电平代表1,低电平代表0,称为非归零型。

- 如果在一个时间拍内有脉冲代表1,无脉冲代表0,称为归零型。

- 数值信号只有两种取值,故称为二值信号;数字波形又称为二值位形图。

- 非归零型信号的每位数据占用一拍时间。每秒钟所传输数据的位数称为

数据率或比特率(Bit Rate)。

- 一定时间间隔T,称为1位(bit),或者一拍

-

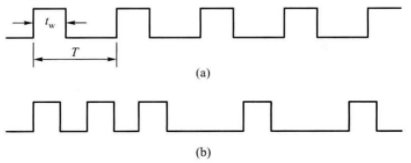

周期与非周期

- 周期性数字波描述

- 周期 T T

- 周期性数字波描述

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1542

1542

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?