MOS 开关的实例声明应以下列关键字之一开头:

cmos nmos pmos rcmos rnmos rpmos

cmos和rcmos开关的介绍博主放在后面的博文中,本篇只介绍MOS~

pmos关键字代表P型金属氧化物半导体(PMOS)晶体管,nmos关键字代表 N 型金属氧化物半导体(NMOS)晶体管。PMOS和NMOS晶体管导通时,源极和漏极之间的阻抗相对较低。rpmos关键字代表电阻式 PMOS 晶体管,rnmos关键字代表电阻式 NMOS 晶体管。与 PMOS 和 NMOS 晶体管相比,电阻式PMOS和电阻式NMOS晶体管在导通时,其源极和漏极之间的阻抗要高得多,例如静态 MOS 网络中的负载器件就是 rpmos 和 rnmos 晶体管。这四个MOS开关类似于bufif逻辑门的单向数据通道。

其延迟指定应为 0、1、2 或 3 个延迟。如果延迟指定为3,第一个延迟应决定上升延迟,第二个延迟应决定下降延迟,第三个延迟应决定到 z 的转换延迟,三个延迟中最小的延迟应决定到 x 的转换延迟。如果延迟指定包含两个延迟,第一个延迟应决定输出上升延迟,第二个延迟应决定输出下降延迟,两个延迟中较小的延迟应适用于到 x 和 z 的输出转换。如果延迟只指定了一个延迟,则应指定所有输出转换的延迟。如果没有指定延迟,则通过开关的传播延迟应为零。

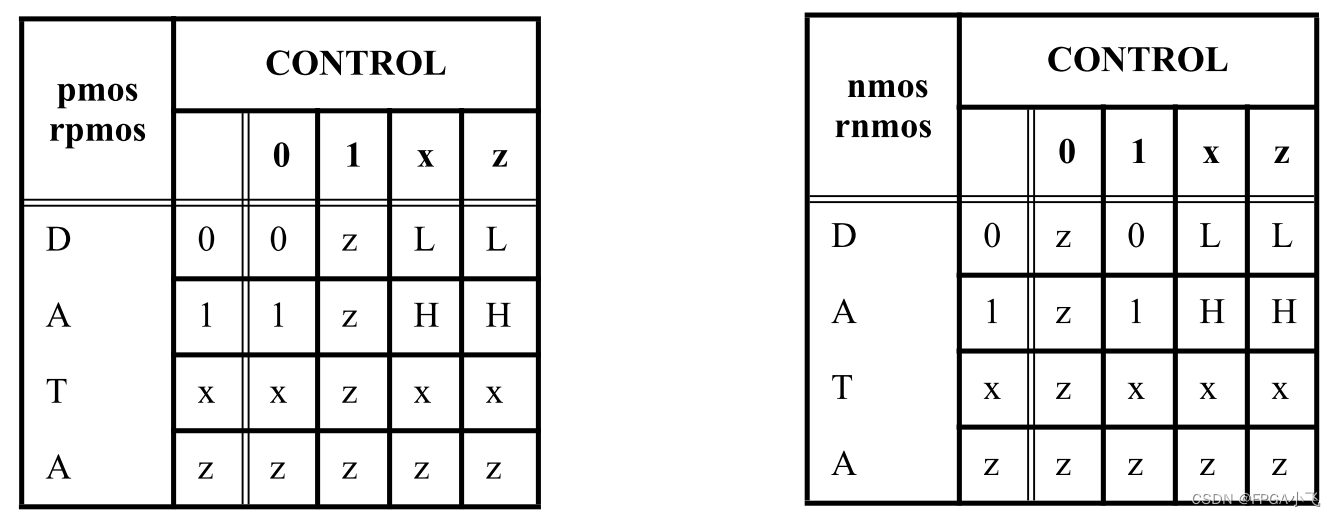

数据输入值和控制输入值的某些组合可使这些开关输出0,1两个值中的任何一个,而不偏向任何一个值。这些开关的逻辑表中有两个符号代表这种未知结果。符号 L 表示值为 0 或 z 的结果。符号 H 表示值为 1 或 z 的结果,转到 H 和 L 的延迟应与转到 x 的延迟相同。

这四个开关有一个输出端、一个数据输入端和一个控制输入端。端口列表中的第一个端口应连接到输出端,第二个端口应连接到数据输入端,第三个端口应连接到控制输入端。

表1列出了这些开关的逻辑真值表:

例如下面的示例声明了一个 pmos 开关:

pmos p1 (out, data, control);

其中输出为 out,数据输入为 data,控制输入为 control,实例名称为 p1。

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

2515

2515

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?