xilinx FPGA jesd204b ADC篇(0):JESD204术语-CSDN博客

xilinx FPGA jesd204b ADC篇(1):什么是JESD204-CSDN博客

xilinx FPGA jesd204b ADC篇(2):JESD204的意义-CSDN博客

xilinx FPGA jesd204b ADC篇(3):高速数据转换器的输出接口-CSDN博客

xilinx FPGA jesd204b ADC篇(4):JESD204B接口介绍-CSDN博客

xilinx FPGA jesd204b ADC篇(5):JESD204B接口的关键-CSDN博客

xilinx FPGA jesd204b ADC篇(6):JESD204B IP核简介-CSDN博客

xilinx FPGA jesd204b ADC篇(7):JESD204B IP核端口介绍-CSDN博客

xilinx FPGA jesd204b ADC篇(8):JESD204B IP核寄存器-CSDN博客

xilinx FPGA jesd204b ADC篇(9):JESD204B IP核设计实现-CSDN博客

xilinx FPGA jesd204b ADC篇(10):JESD204B IP核的AXI4-lite配置接口读写-CSDN博客

xilinx FPGA jesd204b ADC篇(11):JESD204B ADC硬件实现架构-CSDN博客

xilinx FPGA jesd204b ADC篇(12):JESD204B ADC数据采集实现-CSDN博客

*******私信博主请加V:FPGA_GO*******

博主小飞继续和大家分享xilinx FPGA jesd204b ADC篇的第11部分相关内容~

数据信号电平

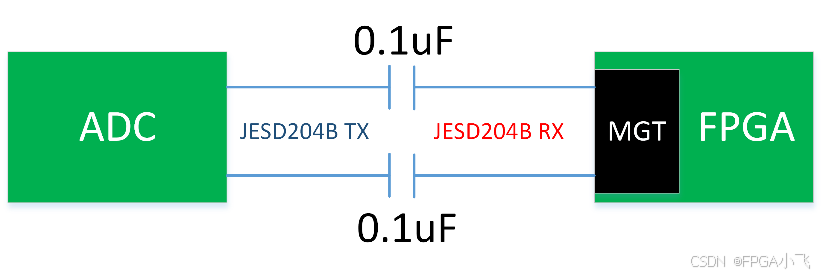

ADC与FPGA之间的JESD204B数据传输采用的是CML电平标准,且为交流耦合,不需要外部匹配,使用起来很方便。FPGA接收端的MGT都会有内部匹配电路,无需我们自己设置外部上下拉电阻,如图1所示为ADC与FPGA之间的JESD204B数据通路。

图1:JESD204B数据传输交流耦合

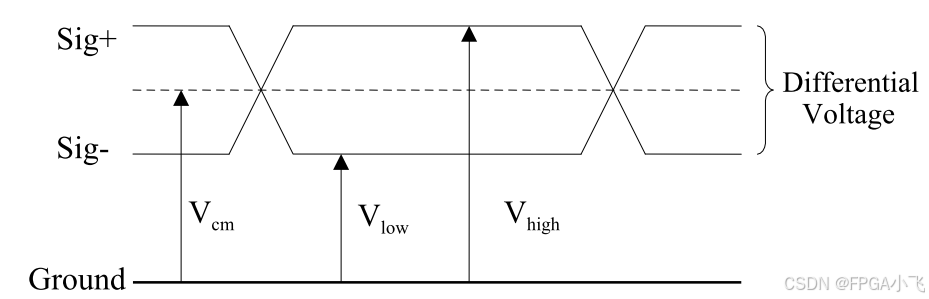

CML电平标准的详细内容网上一大堆,博主小飞这里就不详细介绍了,其电平的示意图如图2所示。

图2:CML信号电平示意图

一般来说,Vhigh为1.2V, Vlow为0.8V,共模电压VCM为1V。因此差分信号的VPP=2×(Vhigh-Vlow)=800mV.

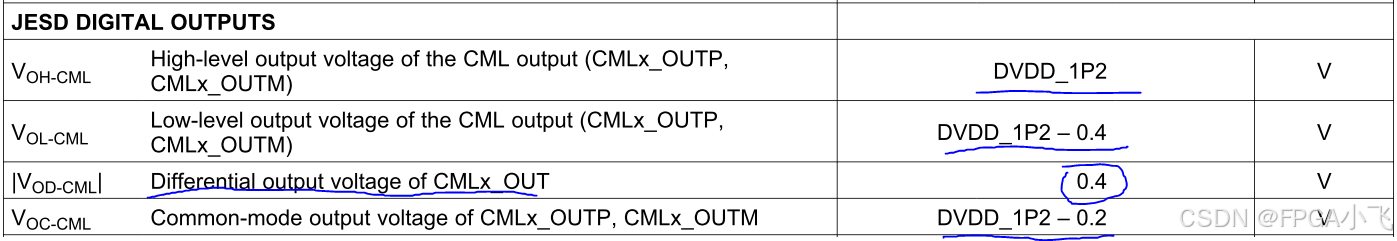

图3:典型ADC的CML信号输出电平

JESD204B数据采集系统整体结构概述

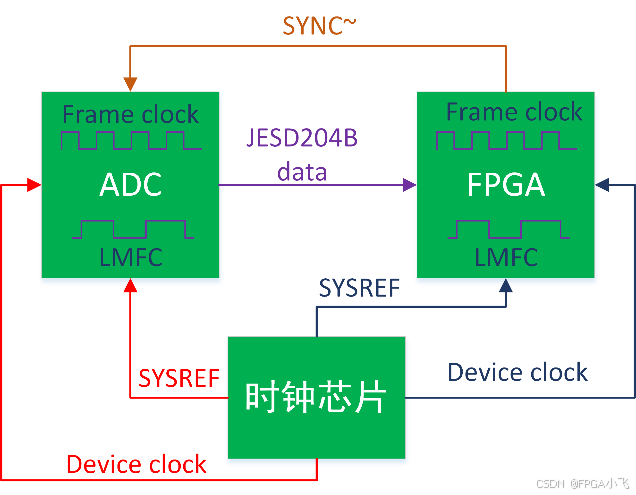

如图4为JESD204B系统的整体硬件连接示意图,博主小飞把开发JESD204B ADC系统所有需要的信号都在其中标识出来了。

图4:JESD204B协议的外部互连时钟与控制

在谈具体的JESD204B协议内容之前,咱们需要先了解实现该协议的几个关键性信号的概念:

1)Device clock(设备时钟)

设备时钟是JESD204B系统里每个芯片(ADC、DAC、FPGA)的参考时钟。每个芯片的设备时钟必须同源,且每个芯片内部的帧时钟和本地多帧时钟均由设备时钟产生,这些时钟之间的倍数关系均依赖于JESD204B的不同子类(subclass),子类的具体定义在后文介绍)。

子类0:设备时钟、帧时钟、多帧时钟的倍数关系由芯片制造商决定。

子类1:多帧时钟周期必须是设备时钟周期的整数倍。

子类2:除了必须满足多帧时钟周期必须是设备时钟周期的整数倍这个条件外,发送端设备时钟周期必须与接收端设备时钟周期成整数倍关系。

设备时钟的电平标准可以是CMOS、LVDS、LVPECL或者CML等,具体情况由芯片制造商决定。

2)Frame clock(帧时钟)和Local multi-frame clock(本地多帧时钟)

JESD204B协议的应用层、数据链路层数据的处理均由帧时钟负责,帧时钟和多帧时钟是由外部输入的设备时钟在芯片内部产生的,对于某些应用,链路数据不仅以帧为格式,几个帧数据还能组成多帧数据,而多帧数据此时必须对齐于多帧时钟。总的来说,帧和多帧时钟必须满足如下要求:

(1)发送和接收设备的帧时钟必须相同。

(2)发送和接收设备的多帧时钟必须相同。

(3)帧时钟和多帧时钟必须同源。

(4)在每个设备内部,帧和多帧时钟必须上升沿对齐。

(5)JESD204B系统内所有的时钟必须同源。

(6)对子类1而言,帧和多帧时钟的相位由设备时钟和SYSREF信号决定。

3)SYNC信号

SYNC接口用于传输从接收器到发送器的信号SYNC~(该信号低电平有效),该信号从接收器输出时,需要与接收器内的帧时钟同步,且与发送器之间必须是直流耦合.顾名思义,该信号就是从FPGA发出,ADC接收,可以用来同步ADC的输出数据,具体用法后文会给出。

4)SYSREF信号

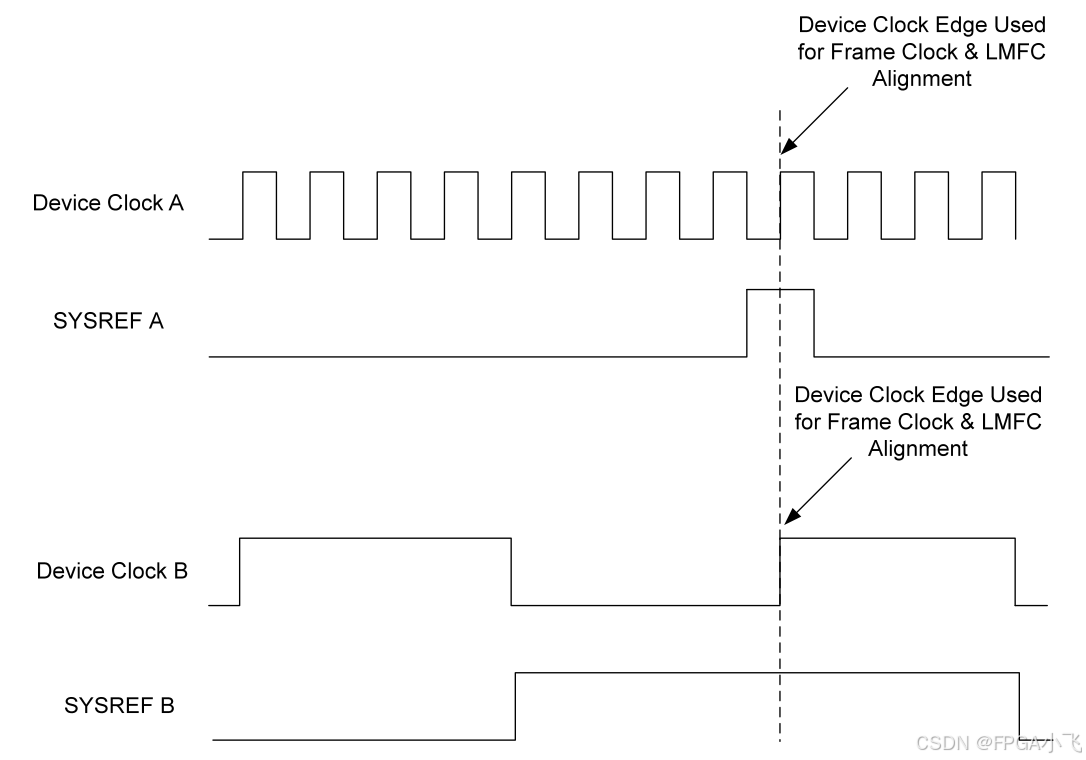

SYSREF在子类1中使用,用于实现系统的确定性延迟。系统中的每个设备都必须引入该信号,且该信号必须与设备时钟同源,用来确定设备内部帧时钟和多帧时钟的相位。该信号可以是周期性时钟信号、单脉冲信号、间歇性周期信号的一种,但对于周期或者间歇性周期SYSREF,它的周期必须是LMFC的整数倍。设备时钟的上升沿采集到SYSREF信号0→1变化时,就确定了LMFC和帧时钟的相位。如图5为SYSREF被设备时钟采样的时序图。

图5:SYSREF采样

SYSREF和设备时钟的相位关系必须保持完全同步,用来实现确定性延迟测量。因此二者的电平标准、PCB走线、阻抗匹配等硬件条件最好一致。

2363

2363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?