Verilog学习笔记一

有关模块代码的学习(方法不唯一)

本人将根据教材《Verilog数字系统教程》-----(夏宇闻)学习总结

本文章为实例主题(一)

1.16位半加器

module halfadd(A,B,sum,cout);

input [15:0] A,B;

output [15:0] sum;

output cout ;

wire [15:0] sum;

wire cout ;

assign {cout,sum} = A+B;

endmodule

2.测试电路一

module Test(Error,Wait,Valid,Clear,Out);

input Error,Wait,Valid,Clear;

output Out ;

wire T1,T2,Out;

assign T1 = ~(Error&Wait);

assign T2 = ~(Valid|Clear);

assign Out = T1&T2;

endmodule

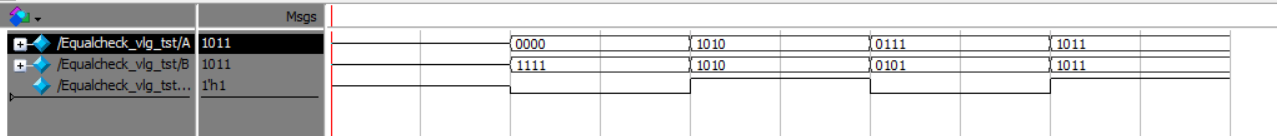

3.4bit 相等比较器

code:

module Equalcheck(A,B,Result);

input [3:0]A,B;

output Result;

//assign Result=(A==B);//这句话也可

assign Result = (A==B)?1:0;

endmodule

testbench

`timescale 1 ps/ 1 ps

module Equalcheck_vlg_tst();

reg [3:0] A;

reg [3:0] B;

// wires

wire Result;

Equalcheck i1 (

.A(A),

.B(B),

.Result(Result)

);

initial

begin

#100 A=4'b0000;B=4'b1111;

#100 A=4'b1010;B=4'b1010;

#100 A=4'b0111;B=4'b0101;

#100 A=4'b1011;B=4'b1011;

#100 $stop;

end

endmodule

4.1bit 全加器

module add_1bit(A,B,Cin,sum,cout);

input A,B,Cin;

output sum,cout;

assign {cout,sum} = A+B+Cin;

endmodule

5. 8bit单向总线缓冲器

code

module tri_buf(Dout,Din,en);

input en;

input [7:0] Din;

output [7:0] Dout;

assign Dout = (en)?Din:8'bz;

endmodule

testbench

`timescale 1 ps/ 1 ps

module t();

reg [7:0] Din;

reg en;

wire [7:0] Dout;

tri_buf i1 (

.Din(Din),

.Dout(Dout),

.en(en)

);

initial

begin

en=0;

Din=0;

#100 en=1;

#100 Din=8'b10110110;

#100 Din=8'b11111111;

#100 Din=8'b10101010;

#100 Din=8'b01010101;

#100 Din=8'b11010111;

#100 $stop;

end

endmodule

6.带同步清零的约翰逊移位计数器

module SHIFT (A,clr,clk);

input clk,clr;

output [2:0]A;

reg[2:0] A ;

always@(posedge clk)

if(clr)

A <= 3'b000;

else

begin

A[0] <= ~A[2];

A[2:1] <= A[1:0];

end

endmodule

7.Case实现4选1多路选择器

module mux4_1(in1,in2,in3,in4,sel,dout);

input in1,in2,in3,in4;

input [1:0]sel;

output dout;

reg dout;

always@(*)

case (sel)

2'b00: dout =in1;

2'b01: dout =in2;

2'b10: dout =in3;

2'b11: dout =in4;

default dout = 1'bx;

endcase

endmodule

8.Case实现3-8译码器

module decode3_8(in,out);

input [2:0]in;

output [7:0] out;

reg [7:0] out;

always@(in)

case (in)

3'b000: out=8'b1111_1110;

3'b001: out=8'b1111_1101;

3'b010: out=8'b1111_1011;

3'b011: out=8'b1111_0111;

3'b100: out=8'b1110_1111;

3'b101: out=8'b1101_1111;

3'b110: out=8'b1011_1111;

3'b111: out=8'b0111_1111;

default out = 8'bz;

endcase

endmodule

9. 异步清零,异步置数触发器

module DEF1(q,out,clk,clr,set);

input q,clk,clr,set;

output out;

reg out;

always@( posedge clk or negedge clr or negedge set)

begin

if(!clr)

out <= 1'b0;

else if(!set)

out <= 1'b1;

else

out <= q;

end

endmodule

10.异步清零,同步置数8bit计数器

module count (clk,rst,load,datain,out);

input clk,rst,load;

input [7:0]datain;

output [7:0] out;

reg [7:0] out;

always@(posedge clk or negedge rst)

begin

if(!rst)

out <= 8'h00;

else if(load)

out <= datain;

else

out <= out +8'h1;

end

endmodule

11.带输入输出缓冲的16bit半加器

module bufadd (A,B,C,clk,rst);

input [15:0]A,B;

input clk,rst;

output[16:0]C;

reg [15:0]a,b;

reg [16:0]c;

always @(posedge clk)

if (!rst)begin

a <= 16'b0;

b <= 16'b0;

end

else

begin

a<=A;

b<=B;

end

/*always @(posedge clk)

begin

if(!rst)

c<=17'b0;

else

c<=a+b;

end

assign C=a+b;*/

//上面注释的话可代替下面的话。

assign c=a+b;

always @(posedge clk)

begin

if(!rst)

C<=17'b0;

else

C<= c;

end

endmodule

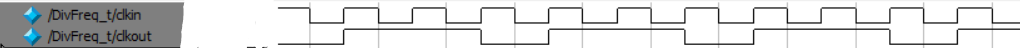

12.不同占空比的分频器

code:

module DivFreq (clkin,clkout,rst);

input clkin,rst;

output clkout ;

reg [1:0] out ;

reg clkout;

always @(posedge clkin)

if (!rst)

out <= 2'b00;

else if (out ==2'b10)

out <=2'b00;

else

out <=out +2'b01;

always @(posedge clkin)

if (out == 2'b00)

clkout <=1'b1;

else if (out == 2'b10)

clkout <=1'b0;

endmodule

testbench:

`timescale 1 ps/ 1 ps

module DivFreq_t();

reg clkin;

reg rst;

wire clkout;

DivFreq i1 (

.clkin(clkin),

.clkout(clkout),

.rst(rst)

);

always #50 clkin = ~clkin;

initial

begin

clkin = 0;

rst = 1;

#10 rst = 0;

#110 rst = 1;

#10000 $stop;

end

endmodule

13. 8bit 并入串出寄存器

module paratoserial(clk,load,parain,serialout);

input clk,load;

input [7:0]parain;

output serialout;

reg serialout;

reg [7:0]data;

always @(posedge clk)

if(load )

data <= parain;

else

data <= (data<<1);

always @(posedge clk)

if (load)

serialout <=1'b0;

else

serialout <=data[7];

endmodule

14. 4bit 串入串出寄存器

module sisoreg(clk,din,dout);

input clk,din;

output dout;

reg dout;

reg [3:0]q;

always @(posedge clk)

begin

q[0]<= din;

q[3:1]<=q[2:0];

dout <= q[3];

end

endmodule

15.上升沿捕捉电路

module btn(clk,rst,Signal, pos_btn);

input clk, rst,Signal;

output pos_btn;

reg buf1,buf2;

always@(posedge clk)

begin

if(!rst)

begin

buf1 <= 1'b0;

buf2 <= 1'b0;

end

else

begin

buf1 <= Signal;

buf2 <= buf1;

end

end

assign pos_btn = (buf1)&(~buf2);

endmodule

作者寄语

本文章大多为电路模板代码,有少许测试代码。

这些程序大同小异,理解为主即可。

最后,如有问题,可评论,私信。

一个神奇的链接,欢迎打开

3799

3799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?