I2C七宗罪(连载)

I2C第七罪

由于前段时间工作上的事情比较杂乱, 导致第七罪姗姗来迟,既然是大结局,当然就应该让大家更加深刻的来理解I2C.。我们先来复习一下大家共有的对I2C的认知:

1. I2C的SCL(Clock)总是由Master来驱动;

2. I2C的SDA (Data)则不同,Master和Slave分别都驱动。

这两点想必读者都没有什么疑问,因为前面的六宗罪都已经说得比较多了,我们今天要说的是另外一种特殊情况,就是Slave也会去Drive。

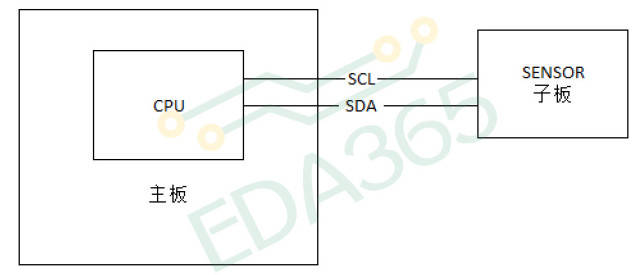

先来看一个例子,我的一个项目发生过这样一件事情,CPU在访问板子上的另外一颗SENSOR时,一直Fail,我们非常仔细检查了时序,都是准确的。

注意:这里我们发现是有一个知识盲点,导致一直找不到Root Cause。

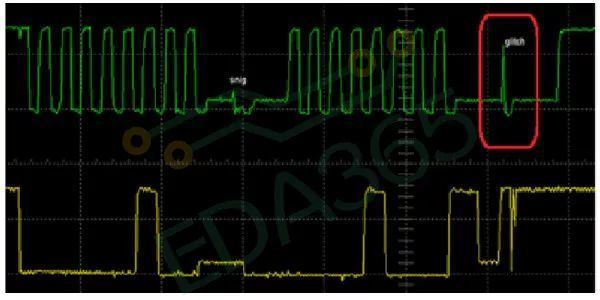

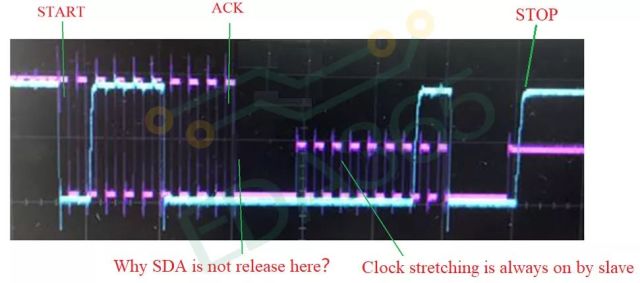

细心的工程师会在测量过程中发现, SCL上有下图这样的尖尖的毛刺,毛刺有矮的也有高的,于是我们认为SCL上这种尖毛刺会导致Slave的状态机误触发,跑飞了。

整整一个星期我们都是这么认为的,尝试各种方法试图去消除这个毛刺。

因为信号从主板通过连接器到子板,我们认为这里的SCL信号很容易受到外部的干扰,比如从空间耦合过来的噪声。

所以在信号上加电容、加匹配、降低上拉电阻等等,试图滤除毛刺。

得到的效果是,即便我们滤除的毛刺有改善,可问题依然存在,只是稍有好转。

虽然说,现在拿着结果来讲故事听起来很轻松,其实那个过程真的很难受,我们接着往下看。

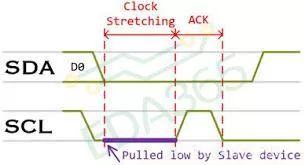

俗话说三人行必有我师,有个聪明的工程师突然想到I2C有个Clock stretch的机制,来看这张图,我们看到Slave把SCL拉到低,这是什么情况呢?

先来叙述一下Clock Stretch:

1.当Master是高速I2C设备,Slave是Low Speed设备时,Master输出的SCL的频率超出了Slave的承受范围,此时Slave跟不上Master的速度怎么办?Slave就要想办法告诉Master。

大家知道为什么这里会看到右边矮矮的Glitch吗?

因为Master此时是想驱动SCL高电平,而Slave却拖住SCL不让变为高电平,这个其实是一种想象,实际测试是看不到的,这里是为了方便大家理解。

2.我们再来看一张图,加深一下理解,Slave会强行把SCL拉低,拖住Master,这和之前我们对I2C的认知是完全相反的,此时Slave 是输出SCL信号,而Master则是检测SCL状态的输入信号。

举个例子:

正常情况下Master/Slave都是通过在SDA上的ACK信号来确认一笔操作的成功,如图:

但是如果Slave来不及怎么办?

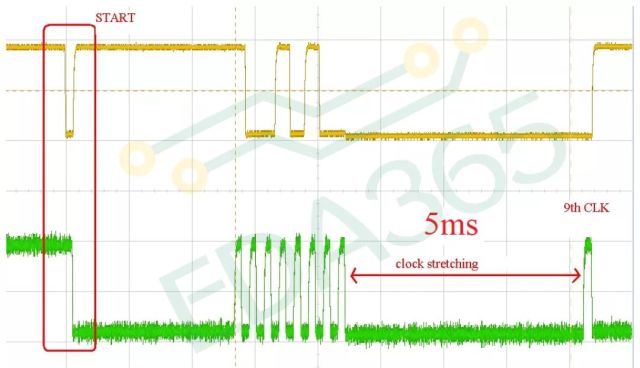

(看下图)Slave直接把SCL信号拖住告知Master:兄弟我还没有准备好,你先等等我啊。

此时Master要做的事情就是乖乖等着,并且一直检测SCL的状态(输入信号),当Slave松开SCL信号,由于上拉电阻的存在,SCL自然变高,Master检测到SCL变高后,才开始检测ACK信号,然后继续下一步操作。

说了那么多I2C stretch,想必大家应该理解了。

回到最上面我们遇到的CPU和SENSOR之间的I2C问题,我们测量得到毛刺确实是罪魁祸首。

因为此时CPU和SENSOR进入了Clock Stretch, Sensor拉低了SCL,而CPU Master不断地检测SCL的状态,期待高电平的到来,此时毛刺就误导了CPU,CPU看到尖的毛刺就认为Slave已经松开了SCL,就立刻开始下一步的动作,此时Slave很冤枉了,自己明明拉低了SCL让Master等着,可是这位兄弟怎么这么不听话呢?

解决的方法很简单,CPU的I2C控制器在进入Clock Stretch时,检测SCL并且判断高电平时有一个De-Glitch的功能,我们之前没有打开,打开后就可以滤除Glitch这样的窄脉冲了。

简单一点讲,就是当检测到一个SCL的高,用一个计数器继续连续计数,只有发现连续的40个高电平才认为是SCL真的拉高了,否则就认为是毛刺,不予理睬。

聪明的人很多,我们再来说说最近碰到的另外一件关于Clock Stretching的事情。

紫色的线有一段半高, 其实原因也简单,就是因为此时Slave拉低SCL,但是Master不支持Clock Stretch,此时就发生了冲突。

Master不支持Clock Stretch,我们就需要通过软件的方式去模拟,此时有两件事需要实现:

1. Master要把SCL切换为输入,然后不停检测SCL的状态;

2. Master在检测SCL状态一定要做De-bounce或者De-Glitch的滤波。

看完了上面的叙述,想必大家都可以理解原因。可是这样会让软件工程师们很麻烦,那么应该怎样绕开Clock Stretch呢? 聪明的工程师总有自己的办法。

我们和Slave芯片的Vendor确认,每次Slave在做ACK后,芯片需要最多5ms的Clock Stretch延时。

我们拿到这个数字后,软件工程师只要注意在Master每次得到ACK后,先等待5ms后再对Slave做下一笔操作。

在这个5ms期间Master完全不用关心 SCL信号上是高电平和低电平,因为5ms以后Slave肯定松开了SCL,也就是说SCL肯定是高电平了。

这种方法就避免Master的SCL信号切换为输入,还要不停地检测SCL的状态,最重要的是不需要做软件的De-bounce或者De-Glitch算法。

自此I2C的七宗罪就结束了,希望这七宗罪可以cover所有硬件设计过程中的I2C问题,到目前我还没有发现有其它超出这七个范围的问题。

第一罪 https://www.eda365.com/forum.php?mod=viewthread&tid=187412&highlight=I2C%C6%DF%D7%DA%D7%EF

https://www.eda365.com/forum.php?mod=viewthread&tid=187412&highlight=I2C%C6%DF%D7%DA%D7%EF

第二罪 https://www.eda365.com/forum.php?mod=viewthread&tid=187961&highlight=I2C%C6%DF%D7%DA%D7%EF

https://www.eda365.com/forum.php?mod=viewthread&tid=187961&highlight=I2C%C6%DF%D7%DA%D7%EF

第三罪 https://www.eda365.com/forum.php?mod=viewthread&tid=191884&highlight=I2C%C6%DF%D7%DA%D7%EF

https://www.eda365.com/forum.php?mod=viewthread&tid=191884&highlight=I2C%C6%DF%D7%DA%D7%EF

第四罪 https://www.eda365.com/forum.php?mod=viewthread&tid=197543&highlight=I2C%C6%DF%D7%DA%D7%EF

https://www.eda365.com/forum.php?mod=viewthread&tid=197543&highlight=I2C%C6%DF%D7%DA%D7%EF

第五罪 https://www.eda365.com/forum.php?mod=viewthread&tid=201223&highlight=I2C%C6%DF%D7%DA%D7%EF

https://www.eda365.com/forum.php?mod=viewthread&tid=201223&highlight=I2C%C6%DF%D7%DA%D7%EF

第六罪 https://www.eda365.com/forum.php?mod=viewthread&tid=257204&highlight=I2C%C6%DF%D7%DA%D7%EF

https://www.eda365.com/forum.php?mod=viewthread&tid=257204&highlight=I2C%C6%DF%D7%DA%D7%EF

本文探讨了I2C通信中的最后一罪——时钟延展(Clock Stretching)问题,解释了如何通过软件手段解决Master与Slave设备间的速度不匹配问题,并提出了规避时钟延展的有效策略。

本文探讨了I2C通信中的最后一罪——时钟延展(Clock Stretching)问题,解释了如何通过软件手段解决Master与Slave设备间的速度不匹配问题,并提出了规避时钟延展的有效策略。

9495

9495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?