以前一直用的Vivado自带的Simulation做仿真,最近在学习用ModelSim跑仿真,本人的感受就是:ModelSim在对较小的工程进行时序仿真时,相较于Simulation编译速度更快、门级仿真效果会更好,时序中出现的一些毛刺会呈现出来。ModelSim主要用于FPGA设计的仿真和调试阶段,而Vivado则更加全面,可以用于整个FPGA设计流程的实现和验证。总的来说各有各的优点,联合起来仿真药效更好。

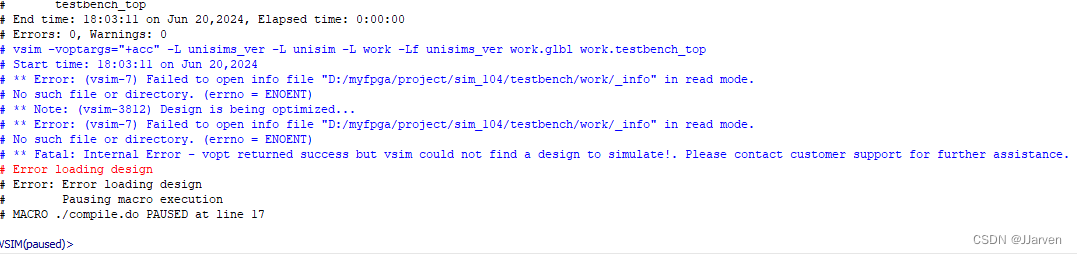

笔者在学习过程中,测试一个时钟缓冲IP BUFGCE和时钟选择IP BUFGMUX遇到的一个问题,利用的是特权提供的模板工程,然后自己编写完测试脚本testbench.v和compile.do文件后,直接进行仿真会报错,如下图所示。

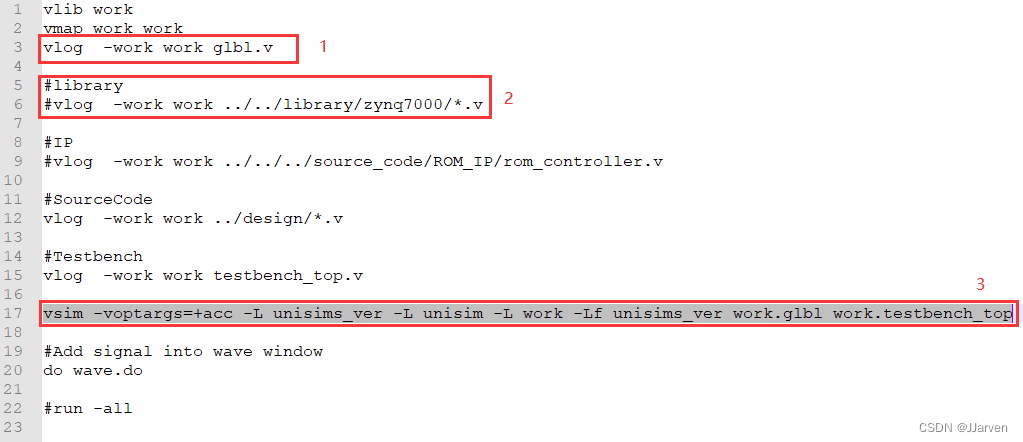

看了一下ModelSim报错的信息,显示的是在compile.do文件中的第17行有问题。用notepad++打开该文件,找到第17行的脚本代码:vsim -voptargs=+acc -L unisims_ver -L unisim -L work -Lf unisims_ver work.glbl work.testbench_top,这段代码的作用是启动仿真器,为什么会在启动仿真器的时候报错呢?查看work里面添加的.v文件,在方框1中添加了一个glbl.v文件,glbl.v是Vivado设计工具的全局时钟缓冲模块,用于将全局时钟信号分配到设计中的所有时钟缓冲器中。它是一个Verilog源文件,包含一个顶层模块,该模块通过实例化其他模块来生成全局时钟缓冲器网络。在设计中使用该模块可以保证时钟缓冲器的相位和延迟一致性,并减小时钟抖动,提高设计的时序性能。glbl.v文件通常由Vivado工具自动生成,用户一般不需要手动编辑它。

看了一下ModelSim报错的信息,显示的是在compile.do文件中的第17行有问题。用notepad++打开该文件,找到第17行的脚本代码:vsim -voptargs=+acc -L unisims_ver -L unisim -L work -Lf unisims_ver work.glbl work.testbench_top,这段代码的作用是启动仿真器,为什么会在启动仿真器的时候报错呢?查看work里面添加的.v文件,在方框1中添加了一个glbl.v文件,glbl.v是Vivado设计工具的全局时钟缓冲模块,用于将全局时钟信号分配到设计中的所有时钟缓冲器中。它是一个Verilog源文件,包含一个顶层模块,该模块通过实例化其他模块来生成全局时钟缓冲器网络。在设计中使用该模块可以保证时钟缓冲器的相位和延迟一致性,并减小时钟抖动,提高设计的时序性能。glbl.v文件通常由Vivado工具自动生成,用户一般不需要手动编辑它。

那为什么会在一个Vivado自动生成的文件会编译报错呢?我以为是在方框2中的库有问题,因为特权用的平台是A7系列FPGA,我是Zynq架构的FPGA导致的编译错误。有模板进行排除错误最快的方式就是控制变量法,我就新建了一个Zynq的Project重新进行IP库的编译,更新了工程中的库文件,在ModelSin命令行输入VISM do compile.do,还是报错!

接着控制变量法,在方框1中的glbl.v文件是模板工程原始的.v文件,特权用的Vivado版本是2019,而笔者用的是2022版本,对于全局时钟缓存的代码或许存在一定的差异。笔者在创建联合仿真路径的时候,用的是2022版本,其中的各种编译库文件也是2022版本的,所以大概率问题在这儿!

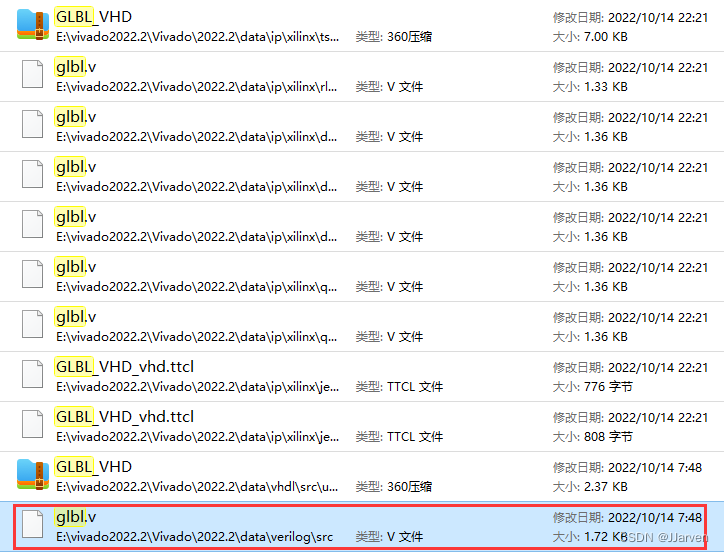

特权在介绍glbl.v的时候是一笔带过的说在安装Xilinx路径下的,如果是初学者肯定就是一头雾水,但是,不懂就去学,上百度找度娘。直接就是暴力一点,到自己安装路径下查找这个文件。

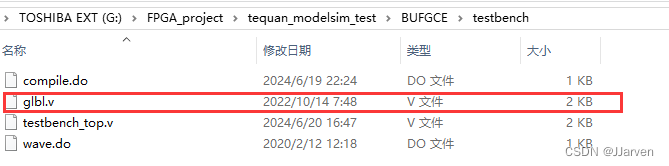

安装路径下有很多glbl.v文件,但是只需要找到全局的时钟缓存文件,该文件在data\verilog\src下,复制后替换模板工程中的glbl.v文件。

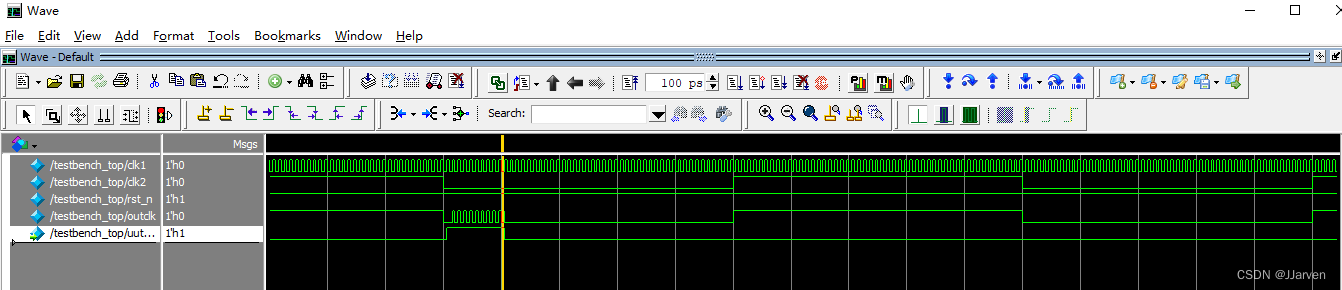

再次编译仿真,报错解决,进入正确的波形仿真页面,仿真波形正确!完结,撒花!

624

624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?