//高速电路设计实践

目录

1、LVDS介绍

Low-Voltage Different Signaling,低压差分信号,支持的最高速率为3.125Gbps,一般应用于点到点的组合。

LVDS的应用场景很多,比如并行高速总线SPI4.2的I/O接口电平即为LVDS,它的功耗是最小的,与TTL和CMOS相比,功耗不会随着工作频率的升高而相应增大。

需要重点注意的是:

(1)LVDS接收方对信号的共模电平要求很弱。差分对内单个信号的电平范围在0~2.4V均可,LVDS的发送/接收方对电源和直流偏置没有特殊要求,使得其特别适合板间长距离信号的传输。

(2)LVDS接收端对输入差分对信号摆幅的要求是100mV。

(3)端接方法:LVDS电平在接收端增加100Ω并联电阻来实现端接。相比于LVPECL,端接方法更简单。端接电阻的作用:实现电流向电压的转化;实现阻抗匹配。

(4)信号沿变化速率较低。信号变化沿速率越低,EMI值越小。

(5)空闲输入引脚应浮空,以防噪声的引入;空闲输出引脚应浮空,以减小功耗。

(6)LVDS不适用于数据速率为2Gbps以上的应用。(应该考虑LVPECL或CML电平)

2、案例:空闲输入引脚处理有误导致FPGA检测到错误输入

问题:某设计中FPGA的LVDS接口作为板间高速互连接口,主控板FPGA上的空闲的LVDS引脚做上、下拉处理。插入业务板瞬间,在主控板上未用的LVDS输入端口上,能不断检测到逻辑状态的变化。

解决分析:

由于空间有限,空闲LVDS引脚的上下拉电阻被放置在较远处,并通过约1000mil的走线连接到FPGA,走线附近存在大量的板间接口信号走线。插拔业务板时,空闲的LVDS引脚摆幅超过100mV。查明原因是没有严格执行差分对走线规则。

LVDS电平的摆幅很小,输入端出现的100mV的摆幅可以被认作是有效的逻辑状态。最终通过对空闲端口上下拉走线的删除使得问题解决。

拓展:

高速差分对常常被作为板间互连接口信号,可以抑制共模噪声,但差分信号线上的共模噪声可能成为一种EMI源。解决方法有两种(1)在PCB上,增大单端信号与差分对信号的间距;(2)降低单端信号的驱动电流(选择低驱动能力的电流)

3、LVDS端口保护

LVDS是常用的板间互连接口。开路状态时,接收器的输出端将保持为逻辑1;当输入接口引入了噪声,且达到接收端的阈值100mV,接收器的输出端翻转为逻辑0。

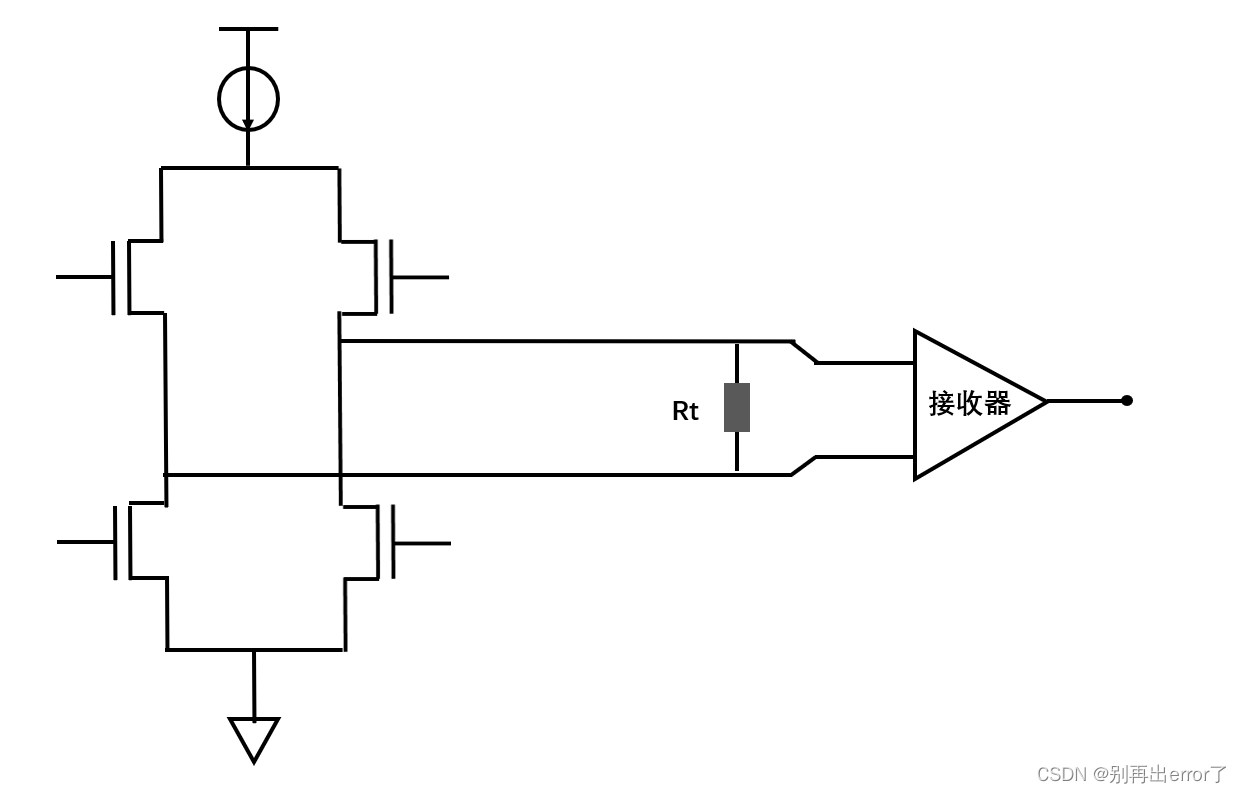

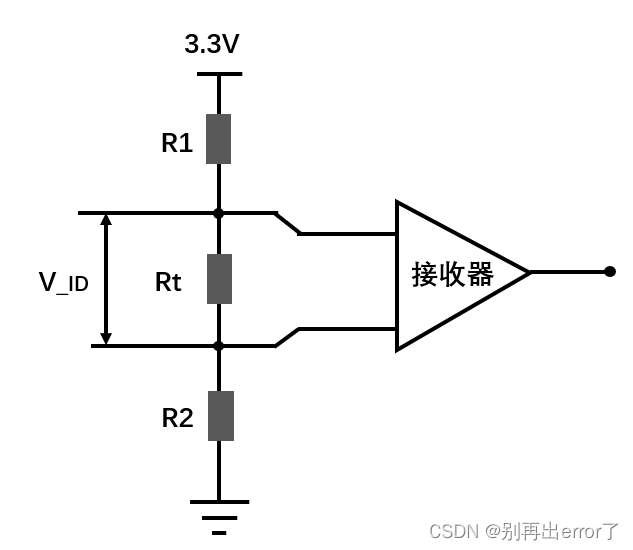

这种情况可以通过外加保护电路在解决。如图,增加两个电阻构成偏置电路。LVDS接收器输入端浮空时,使得产生偏置电压V_ID,提供了更大的噪声冗余。

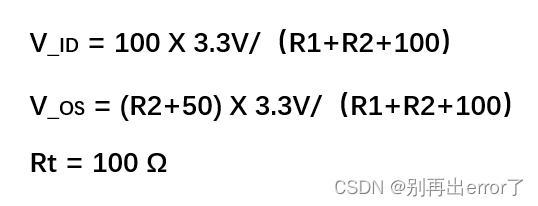

R1和R2阻值的计算方法为:

第一个等式是为了得到25mV的偏置电压,使得有25mV的噪声冗余。

第二个等式是为了保证输出共模电平1.25V(在LVDS的共模电平范围1.125~1.375V之间)。

注意:三个电阻都应该尽量靠近接收端,且偏置电流应该远远小于LVDS提供的3.5mV电流。

缺点:导致占空比失真;造成PCB布局限制。

DONE!!

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?