今天给大侠带来简介Xilinx Spartan-7,Spartan-7 延续了28nm工艺,更加巩固了 Xilinx 在 28nm 的领导地位,今天聊聊 Spartan-7到底有哪些特色、优势,相比前一代有什么不同点,最主要的是,作为使用者,我们应该在怎么选择使用这款新的器件。话不多说,上货。

近日,赛灵思公司再度取得一项里程碑式成就——Spartan 系列器件销量突破 10 亿!这是赛灵思其他产品组合都尚未企及的重要里程碑。作为赛灵思成本优化型产品系列中的旗舰款,Spartan 系列器件始终备受业界青睐,每一代产品都能为工业、消费和汽车应用带来全新的前沿功能,包括任意连接、传感器融合以及嵌入式视觉。首款 Spartan 器件于 1998 年面世。此后,赛灵思不断推出新一代 Spartan 器件,以期提供新型解决方案和灵活应变的技术来满足行业需求。

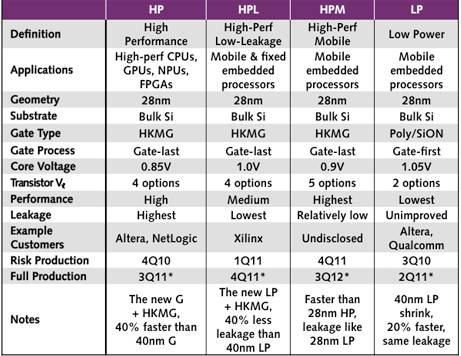

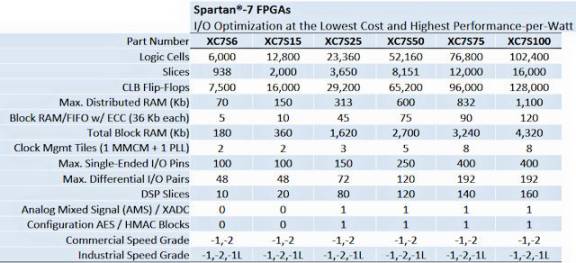

Spartan-7采用台积公司 (TSMC) 的 28nm HPL 成熟工艺,所以功耗自然要比Spartan-6低很多,基本架构还是延续了7系列的CLB架构,增强了DSP和BlockRAM的性能,砍掉了高速串行收发器,所以产品定位低于Artix-7,市场定位依然是成本敏感领域,主要包括有工业、消费类应用以及汽车应用的理想选择。

Spartan-7的特色

01

降低功耗

赛灵思在开发 7 系列(Artix®-7、Kintex®-7 以及 Virtex®-7)器件过程中与台积公司 (TSMC) 通力合作,共同开发出了 28nm HPL 工艺。高介电层金属闸 (HKMG) 工艺提供了高性能与低功耗的最佳组合,Spartan-7 FPGA 采用与成熟的 7 系列相同的 28nm HPL 工艺,以及相同的器件结构,从而使其成为结构紧凑的成本优化型 FPGA 系列器件。

该产品系列具备很高的逻辑和 I/O 性能,功耗也得到严格控制。而且该期间可在两种不同内核电压下工作,使用户能够在最高性能与最低功耗之间平衡。与竞争对手的28nm LP工艺对比如下表:

02

性能更强

-

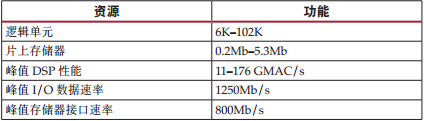

凭借高效率的 7 系列 CLB 架构、增强型 DSP 和 Block RAM等,系统时钟频率提高了30%以上,

-

逻辑资源数量6000~102000,可以实现复杂的功能,

-

增强型 DSP 模块在 551MHz 频率下可提供高达 176 GMAC 的性能

-

MicroBlaze ™ 软核处理器运行速率超过 200DMIPS。

03

更高的逻辑与IO比

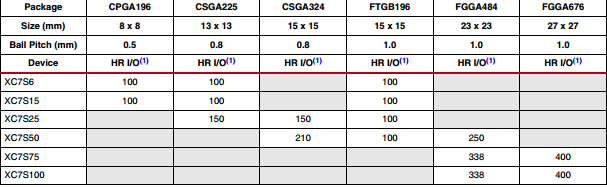

对于低成本器件来说,良好的逻辑与IO比,有利于降低系统整体成本,相比前代产品,Spartan-7的逻辑资源更为丰富,而且减小了器件的封装尺寸,从而降低了系统的复杂度;最小的封装尺寸仅为 8mm,对于尺寸与功耗都有限制的应用领域非常有杀伤力。

更高速的软内存控制器,可以支持DDR3-800,下图为Spartan-7系列的封装图。

04

安全与加密

支持器件的DNA序列号,这是一个57bit的二进制序列,在器件生产的时候烧死到芯片里面,每个芯片都是唯一标识。这个序列,用户可以通过JTAG读出来,然后进行设计加密,而且还支持AES256 CBC Mode 比特流解密与 SHA-256 比特流对称认证,对于保护知识产权非常有帮助。

05

模拟XDAC支持

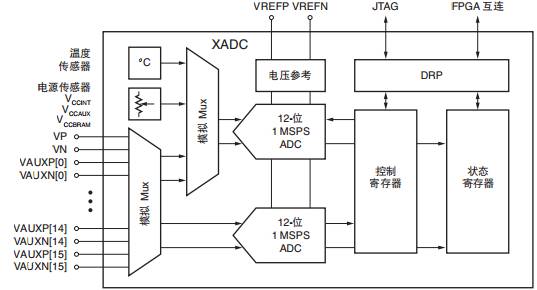

XADC 包含两个 12 位、1MSPS ADC,具有独立的跟踪与保持放大器 ,一个片上多路复用器,多达 17 个外部模拟输入 以及片上热传感器和电源传感器。

06

Vivado开发流程

Vivado 的专家级布局布线技术实现更快的时序收敛和 20% 的利用率提升。可利用很多设计重用功能将针对某款器件或某个系列而构建的部分设计或 IP 打包,便于以后重复用于采用类似架构的另一款器件或系列。例如,设计人员可创建用在Spartan-7 FPGA 中的 IP 核。随着系统要求的不断提高,设计人员可在 Artix-7 FPGA 中重用这一 IP 核。

Spartan-7 家族

结语

Spartan-7器件,降低了功耗,提高了单位封装面积的逻辑资源,增加了很多有用的功能,如果价格合适,相比于前代产品还是很有竞争力的。

NOW现在行动!

推荐阅读

AXI总线详解-AXI4读写操作时序及AXI4猝发地址及选择

ZYNQ中DMA与AXI4总线-DMA简介

AXI总线详解-不同类型的DMA

AXI-Lite 自定义IP

观察 AXI4-Lite 总线信号

点击上方字体即可跳转阅读哟

3338

3338

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?