这篇文章解决两个问题:

1、多版本安装Vivado,强制切换工程文件打开的默认版本;

2、卸载安装Vivado导致工程文件没有和Vivado关联。

解决方法:

主要三个步骤:

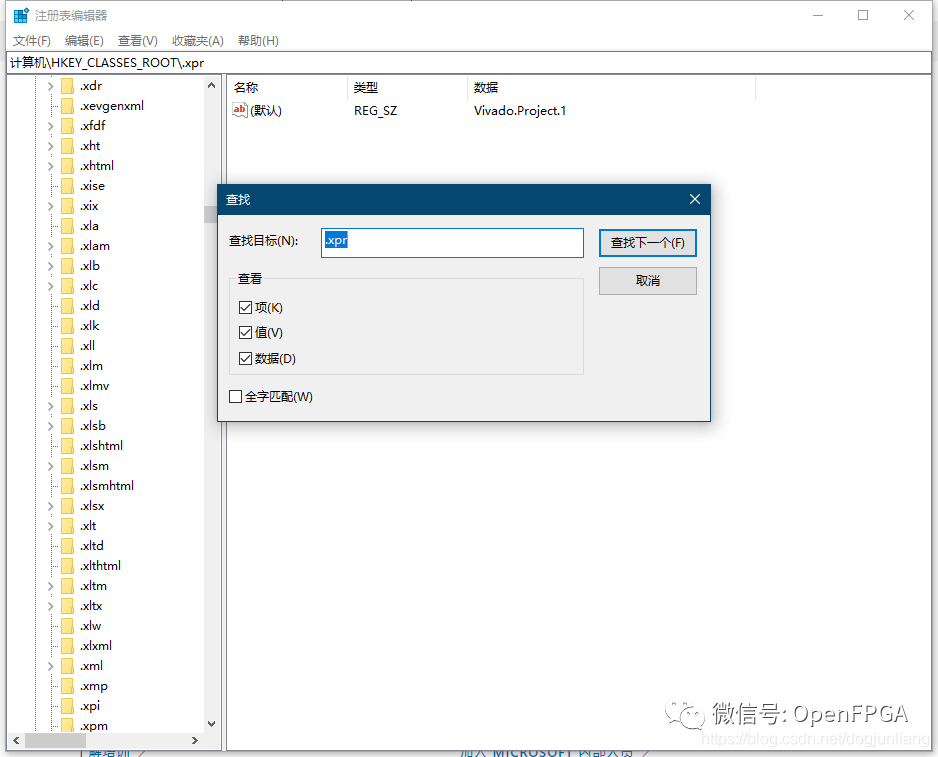

打开注册表,找到HKEY_CLASSES_ROOT

找到.xpr,其中有一个Vivado.Project.1,查找Vivado.Project.1文件夹

修改.xpr文件的默认打开Vivado的版本

一、打开注册表,找到HKEY_CLASSES_ROOT

Win+R打开运行,输入框中输入“regedit”,选择“确定”,搜索HKEY_CLASSES_ROOT,具体目录如下:计算机\HKEY_CLASSES_ROOT\Vivado.Project.1

二、

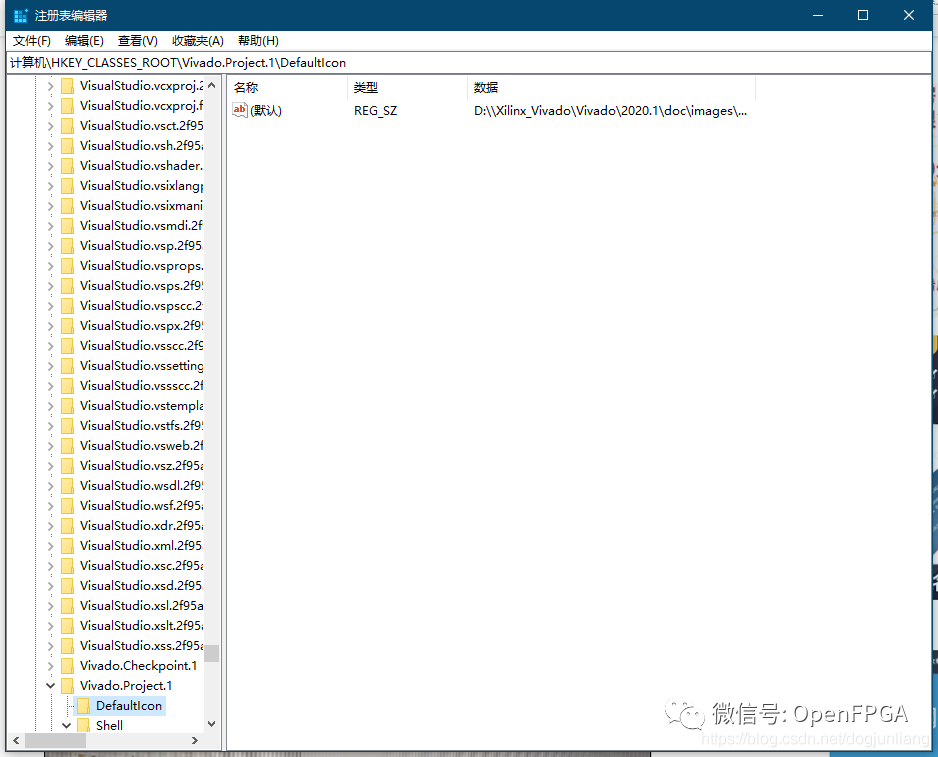

找到.xpr,其中有一个Vivado.Project.1,查找Vivado.Project.1文件夹

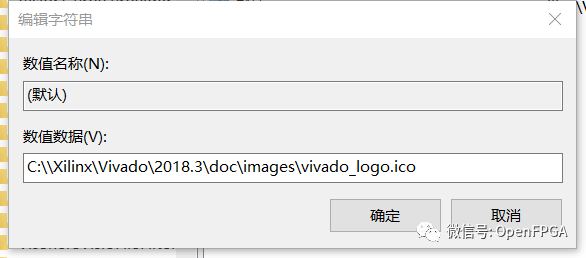

修改DefaultIcon文件夹的默认值。这个值是关联工程文件的logo,修改新版本或者想要版本目录,参考值如下:

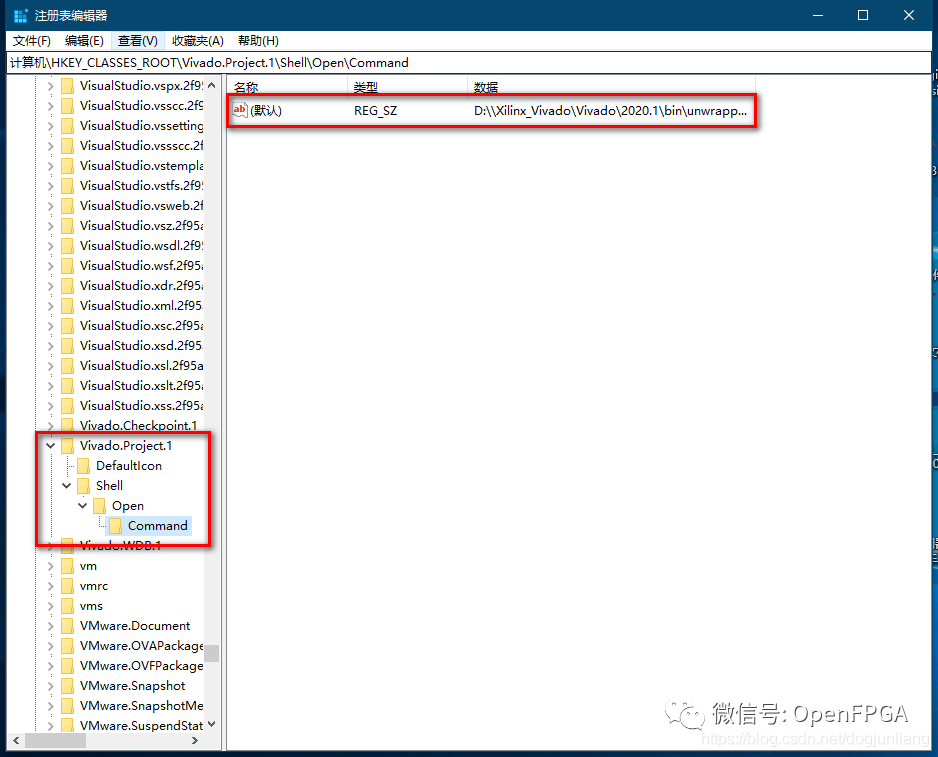

修改.xpr文件的默认打开Vivado的版本

这个设置格式不能修改,可以修改目录,设置格式参考如下:

C:\\Xilinx\Vivado\2018.3\bin\unwrapped\win64.o\vvgl.exe C:\\Xilinx\Vivado\2018.3\bin\vivado.bat "%1"第一个“vvgl.exe”目录位置,空格,”vivado.bat”目录位置,空格, "%1"

上诉格式不能修改。

通过上面几个步骤就可以完成目标。

NOW现在行动!

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

| 文件名 | 主标题 | 内容简单介绍 | 是否有中文版 | |

| UG476 | 7 Series FPGAs GTX/GTH Transceivers | GTX和GTH介绍,PCIe、serdes等学习必备 | 否 | |

| UG471 | 7 Series FPGAs SelectIO Resources | 描述 7 系列 FPGA 中可用的 SelectIO资源。 | 否 | |

| UG1114 | PetaLinux Tools Documentaton | PetaLinux 工具文档 参考指南 | 是,V2019.2 | |

| UG949 | UltraFAST 设计方法指南(适用于 Vivado Design Suite) | 赛灵思® UltraFast™ 设计方法是用于为当今器件优化设计进程的一套最佳实践。这些设计的规模与复杂性需要执行特定的步骤与设计任务,从而确保设计每一个阶段的成功开展。依照这些步骤,并遵循最佳实践,将帮助您以最快的速度和最高的效率实现期望的设计目标 | 是,V2018.1 | |

| IP手册 | pg057 | FIFO Generator | FIFO生成器IP使用手册 | 否 |

| pg104 | Complex Multiplier | 复数乘法器IP使用手册 | 否 | |

| pg122 | RAM-Based Shift Register | 移位寄存器IP使用手册 | 否 |

推荐阅读

【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

高速串行通信常用的编码方式-8b/10b编码/解码

Verilog计时(微秒、毫秒和秒)脉冲的产生及同步整形电路

再说System Verilog 与 Verilog 的关系

本文介绍如何解决Vivado多版本安装后工程文件默认打开版本的问题,包括通过注册表修改默认打开版本的方法,以及如何处理因卸载安装而导致的工程文件与Vivado脱钩的情况。

本文介绍如何解决Vivado多版本安装后工程文件默认打开版本的问题,包括通过注册表修改默认打开版本的方法,以及如何处理因卸载安装而导致的工程文件与Vivado脱钩的情况。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?