一.不通系列fpga对高速口的叫法不一样:

artix7——GTP

kintex7——GTX

virtex7——GTH

二.高速口的架构基本一致————4对rx/tx对+1个时钟模块(包含4个cpll+1个Qpll)

1:一个高速口【一个高速bank:(eg:bank116)】

2:如果需要更高的线速率则就需要更高频的pll(QPLL>cpll)一般在配置ip里面选择

3:一个时钟模块可以接2对差分时钟:满足于tx和rx不同时钟的需求。

三:我们暂时就理解PCS是transceiver的协议部分,较软核的东西,PMA是更偏硬核的东西。

四:

1.GTX里面,CPLL的频率范围为1.6GHz~3.3GHz,支持的最高线速度为6.6Gb/s。QPLL的工作频率在低波段模式时为5.93 GHz到8.0GHz,在高波段的工作频率为9.8GHz~12.5GHz。

2.CPLL通常用于低速率传输通常在3.125G以下,QPLL通常用于高速率传输,QPLL的时钟更加精确,原则是能用QPLL就不用CPLL

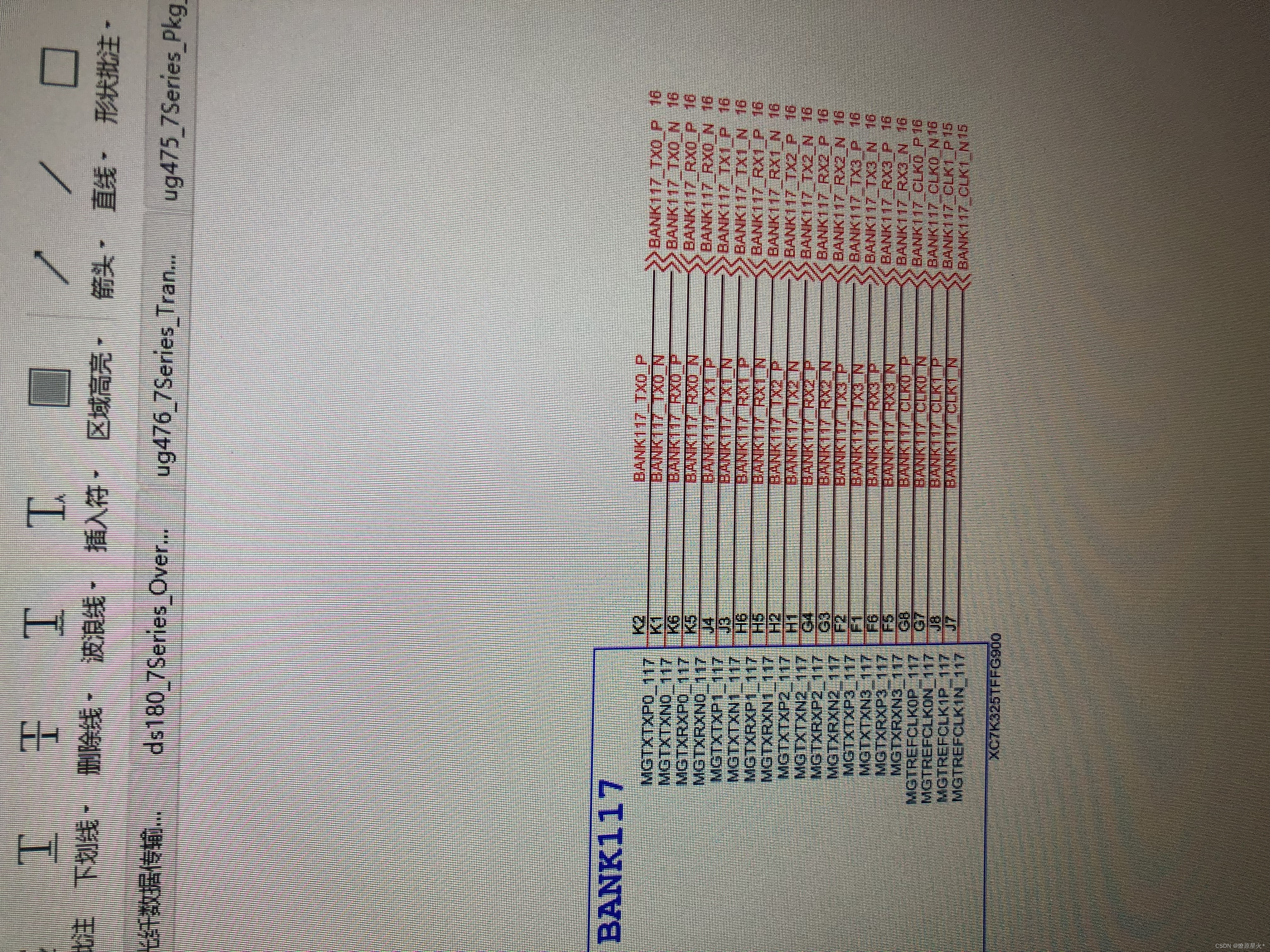

五:K7-325T

___注意图三的bank117的channel 0/1 对应图二的x0y11 和 x0y10

六:高速口运用实例

光纤传输:

1. ibert——是对高速口的硬件链路的检查工具,烧录示列工程看眼图。

2.transceiver——打开示列工程修改参考发送模块(修改想传输的数据,通过光纤。)

重要接口:a.发送数据的时钟 b.接收数据的时钟c.发送数据d.接收数据 e.高速口初始化完成信号.f.发送k码。g.接收k码——具体步骤参考黑金工程光纤

七:

虽然K7系列GTX最高可以跑到12.5Gbps,但这跟速度等级和封装都有关系,是在-3的速度等级,FF封装下才有的最高速度12.5Gbps。——eg : 而现在手头的芯片型号是K7480TFFG901-1,所以最高支持8.0Gbps。其实这在配置IP核的时候就会发现了,线速范围是(0.5-8.0)。所以IP核都是严格和工程的器件相关联的,这点Vivado越做越好了

八:就利用aurora 8B/10B 协议用修改官方例程即可

代码信号解析

//---------------- Transmit Ports - TX Data Path interface -----------------

.gt0_txdata_in (gt0_txdata_i),

//------------------- Transmit Ports - TX Gearbox Ports --------------------

.gt0_txcharisk_in (gt0_txcharisk_i),

//---------------- Receive Ports - FPGA RX interface Ports -----------------

.gt0_rxdata_out (gt0_rxdata_i),

//----------------- Receive Ports - RX8B/10B Decoder Ports ---

.gt0_rxcharisk_out (gt0_rxcharisk_i), 九:TX如下:

同步:包括定期时间的修正同步功能。

SOF:开始码

EOF:结束码

空闲时:发送LFSR(伪随机码),防止EMI.

十:GT的结构

十一:高速口的参考时钟只能最多供给3个quad使用(南,中,北)。如果这三个quad要同时使用一种协议时钟相位一定小一点。最好用同一个晶振给时钟芯片。

十二:高速口的参考时钟有推荐的时钟频率,因为协议的不同推荐频率不同在UG476 51页

十三:修改光口ip配置后,xdc是不会自己改变的。————一定注意

十四:1Gbit/s等于1000Mbit/s,而1Mbit/s等于1000kbit/s,因此1Gbit/s等于1000x1000=1,000,000kbit/s

十五:

通过xilinx官方手册说明:如果GT配置K28.5——bc码——[3:0]ctl4b'0001——00_00_00_bc

1410

1410

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?