下面是8b10b编码器的设计步骤。

-

确定数据输入和输出接口。例如,您需要确定8位并行数据输入和10位串行数据输出。

-

计算数据带宽。这与芯片中可用的时钟速度密切相关。

-

选择编码表。根据应用选择最佳编码表,8b10b编码器至少应使用一张编码表。详细了解和选择编码表有利于改善编码器的性能。

-

编写编码器的状态机。编码器的状态应针对输入数据,在状态转移前确定符号的输出。同样,状态也应该考虑插入或删除代码的位置。

-

关联状态机的输出符号。在每个状态中,都必须关联与该状态相关联的输出符号。此项工作需要根据编码表中编码符号的特点进行。

-

设计电路。设计电路包括选择元件,例如寄存器、计数器、直接构成,以及各种传输门、存储器等。

-

编写Verilog代码。将状态机转换为描述硬件电路的Verilog代码。

-

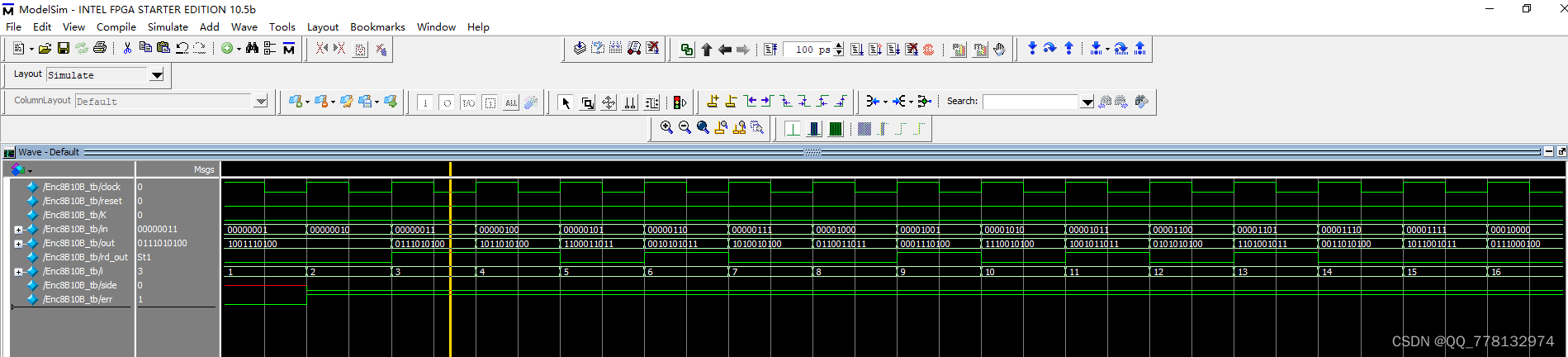

进行仿真测试。使用Verilog开发环境进行仿真测试,并通过仿真验证电路功能。

-

实现和验证。用Verilog将设计转换为FPGA或ASIC的物理实现,并通过测试验证设计性能。

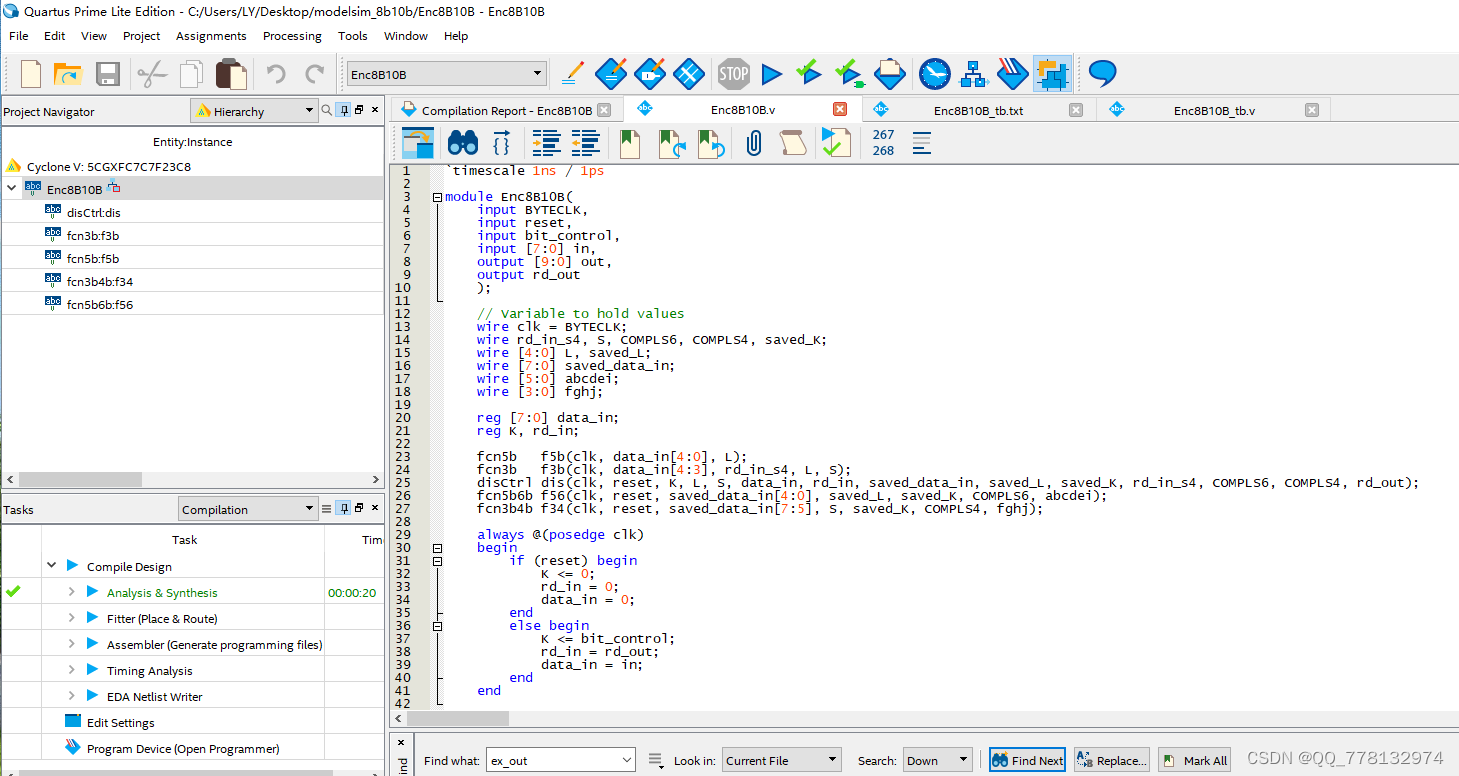

工程截图和仿真截图如下:

顶层模块代码如下:

`timescale 1<

订阅专栏 解锁全文

订阅专栏 解锁全文

1093

1093

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?