本编文章是AXI Central Direct Memory Access v4.1的阅读笔记

硬件规格部分

简介:

AXI CDMA为嵌入式系统提供了高性能的片上互联

The AXI CDMA provides high-bandwidth Direct Memory Access (DMA) between a memory-mapped source address and a memory-mapped destination address using the AXI4 protocol. An optional Scatter

Gather (SG) feature can be used to offload control and sequencing tasks from thesystem CPU.

初始化,状态和控制寄存器都是通过AXI4-Lite slave接口控制

特点概要

- Independent AXI4-Lite slave interface for register access

- Fixed 32-bit data width

- Optional asynchronous operation mode

- Independent AXI4 Master interface for the primary CDMA datapath. Parameterizable width of 32, 64, 128, 256, 512, and 1,024 bits with fixed-address burst (key hole) support.

- Independent AXI4 Master interface for optional Scatter/Gather function. Fixed 32-bit data width.

- Optional Data Realignment Engine for the primary CDMA datapath. Available with 32

and 64-bit datapath widths. - Provides Simple DMA only mode and an optional hybrid mode supporting both Simple

DMA and Scatter Gather automation. - Support for up to 64-bit Address Space

模式:

Register Direct Mode

吞吐量一般,使用简单,占用的逻辑资源少一些。

Scatter/Gather Mode

高吞吐量,减少CPU的干预,释放CPU。使用要复杂一些,也更加消耗逻辑资源。

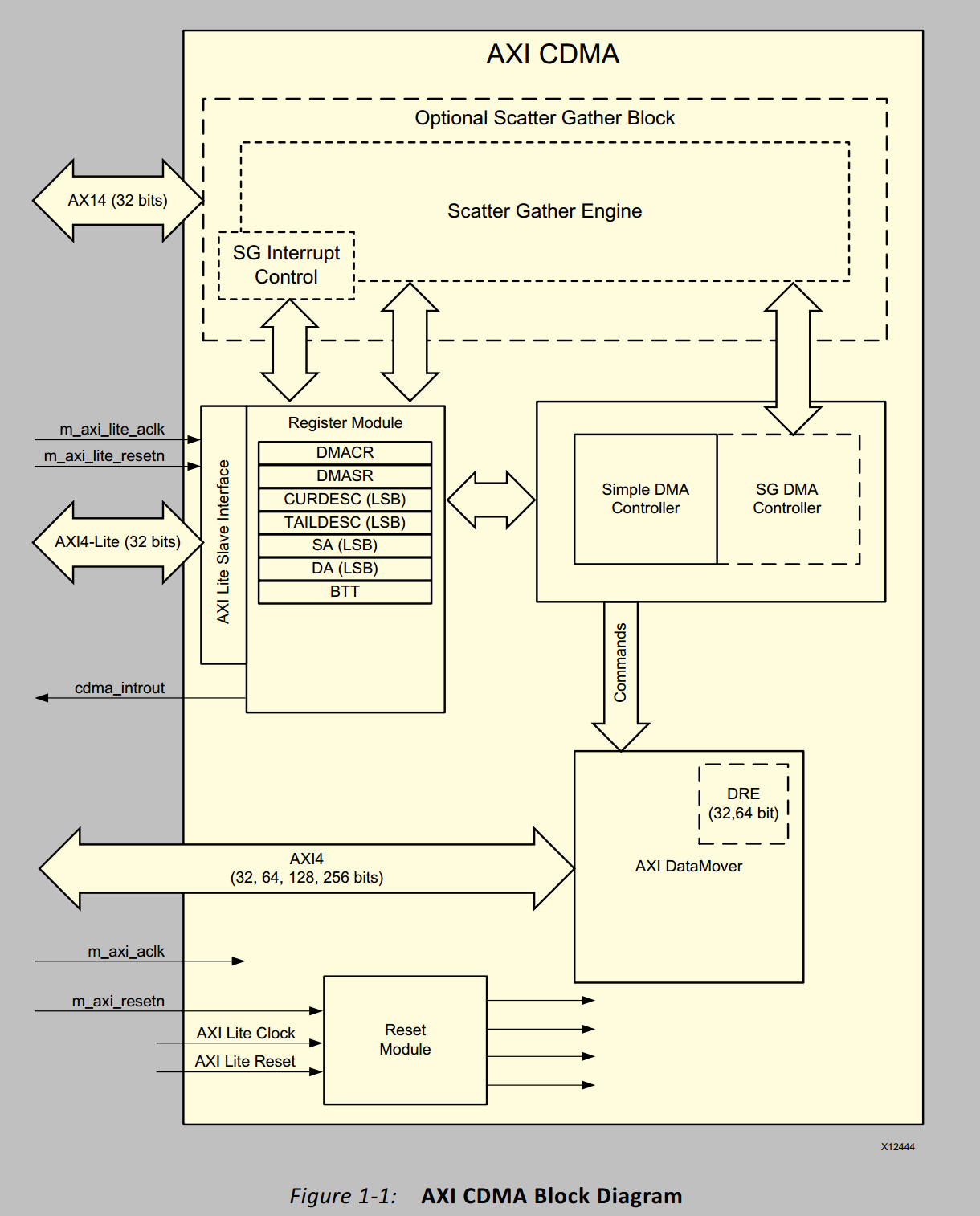

AXI CDMA的结构框图

DataMover

The DataMover is used for high-throughput transfer of data. The DataMover provides CDMA operations with 4 KB address boundary protection, automatic burst partitioning, and can queue multiple transfer requests. Furthermore, the DataMover provides byte-level data realignment (for 32-bit and 64-bit data widths) allowing the CDMA to read from and write to any byte offset combination.

Unaligned Transfers

The AXI DataMover core optionally supports the Data Realignment Engine (DRE). When the DRE is enabled, data is realigned to the byte (8 bits) level on the Memory Map datapath (32-bit,64-bit).

If the DRE is enabled, data reads can start from any Address byte offset. Similarly, when the DRE is enabled, the writes can happen at any byte offset address. For example, if Memory Map Data Width = 32, data is aligned if it is located at address offsets of 0x0, 0x4, 0x8, 0xC, etc. Data is unaligned if it is located at address offsets of 0x1, 0x2, 0x3 and so forth.

Note: Performing unaligned transfers when DRE is disabled will give unpredictable results

执行不对齐传输会出现不可预测的结果,那这种方式的优势是什么?

关于Register Space要注意的

The registers are 32-bits wide, and the register memory space must be aligned on 128-byte (80h) boundaries.

AXI CDMA Register Summary

这个寄存器偏移地址的表格可能会经常使用,具体的寄存器经参考官方文档

| Address Spa |

|---|

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

171

171

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?