本编文章将对VGA的RTL代码,封装成AXI Stream,并且在vivado 里用TPG进行测试

本篇文章的VGA RTL代码在【ZYNQ-7000开发之一】基础上修改,封装好的VGA Stream可以方便我们实现视频图像处理

TGP 等的规范说明可以到官网下载最新版本

本文所使用的开发板是Miz702(兼容zedboard)

PC 开发环境版本:Vivado 2015.2 Xilinx SDK 2015.2

其它:VGA显示器

AXI Stream原理

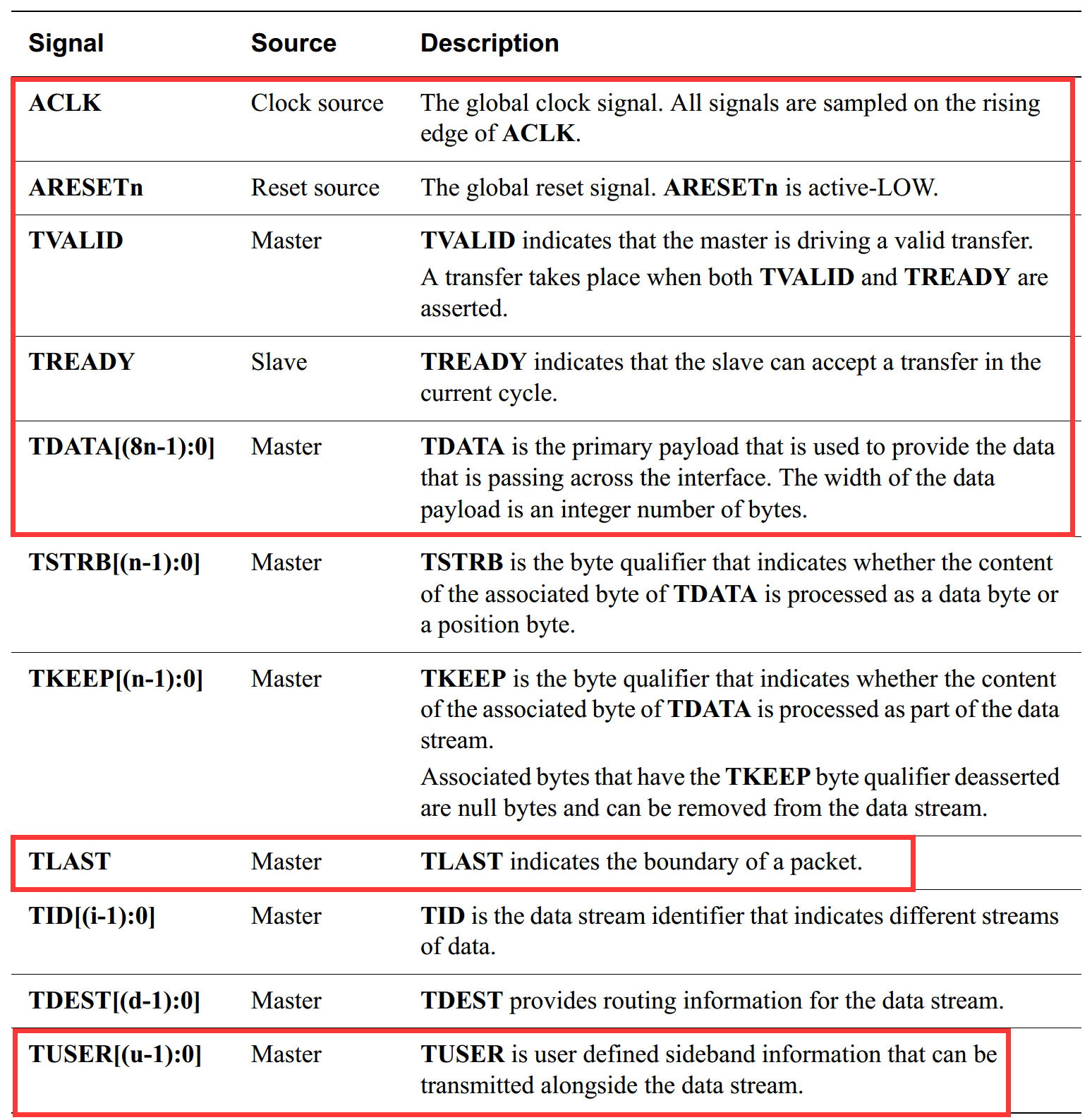

首先这里列出axi stream的信号,红框里的是要用到的

核心的信号是,TVALID,TREADY,TLAST,TUSER

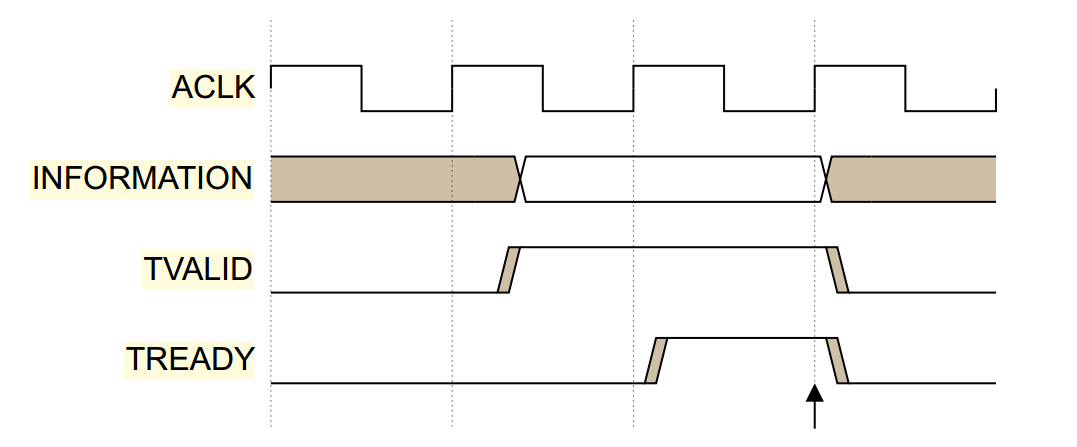

TVALID和TREADY握手信号

在TVALID和TREADY同时有效的时候,数据才有效。对于TPG来说,大部分时间TVALID是有效的,TREADY由我们自己控制。

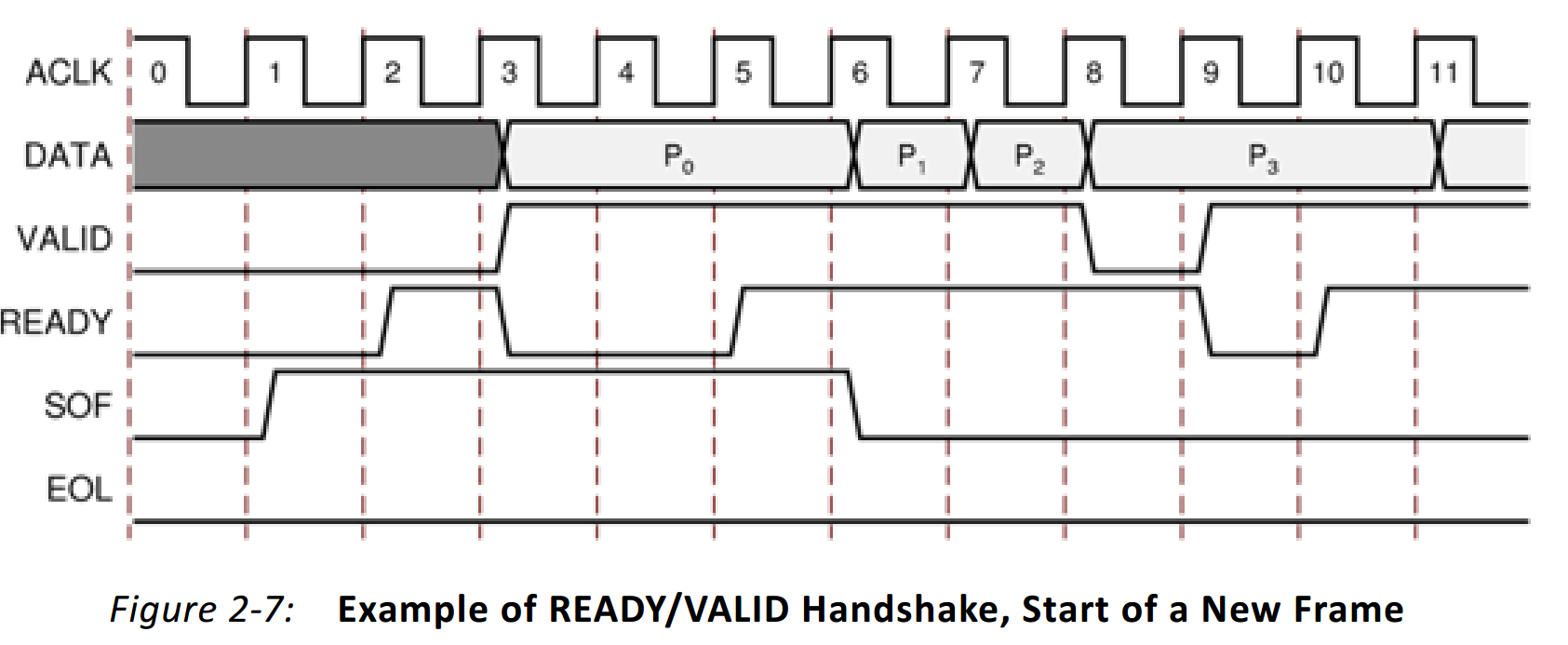

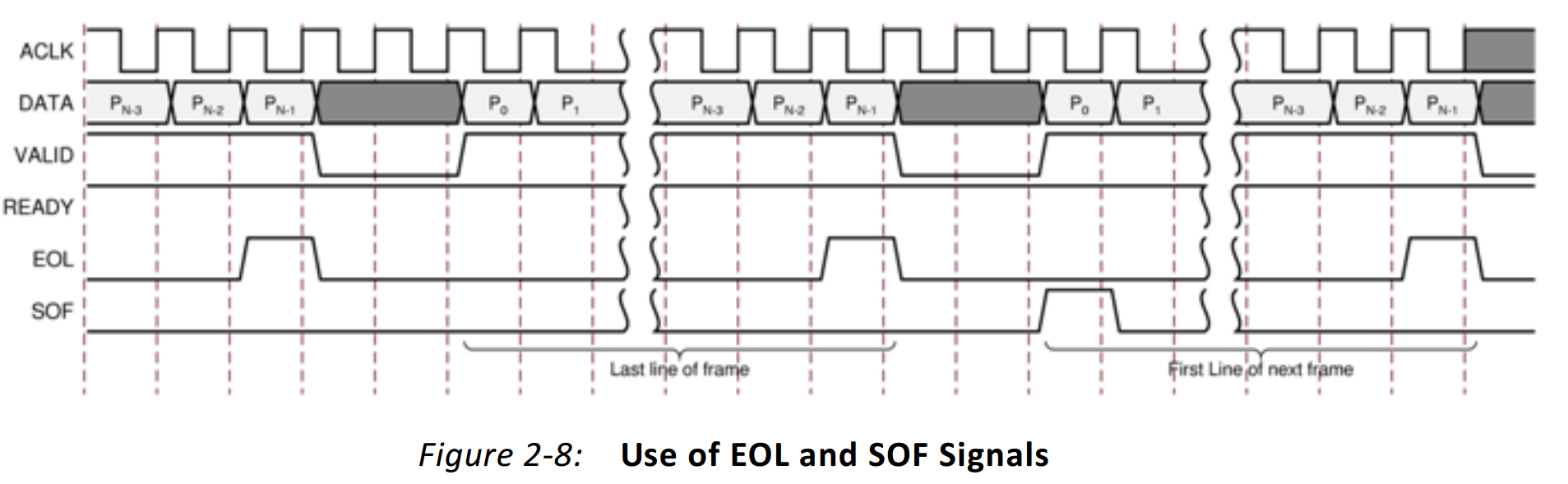

TUSER(SOF,Start Of Frame),代表每一帧的开始。TLAST(EOL,End Of Line),代表每一行的结束。

这里给出TPG的时序图,比较简洁,要理解之后才好把RTL封装成AXI Stream

封装AXI Stream

打开vivado,建立一个工程(选择zed)

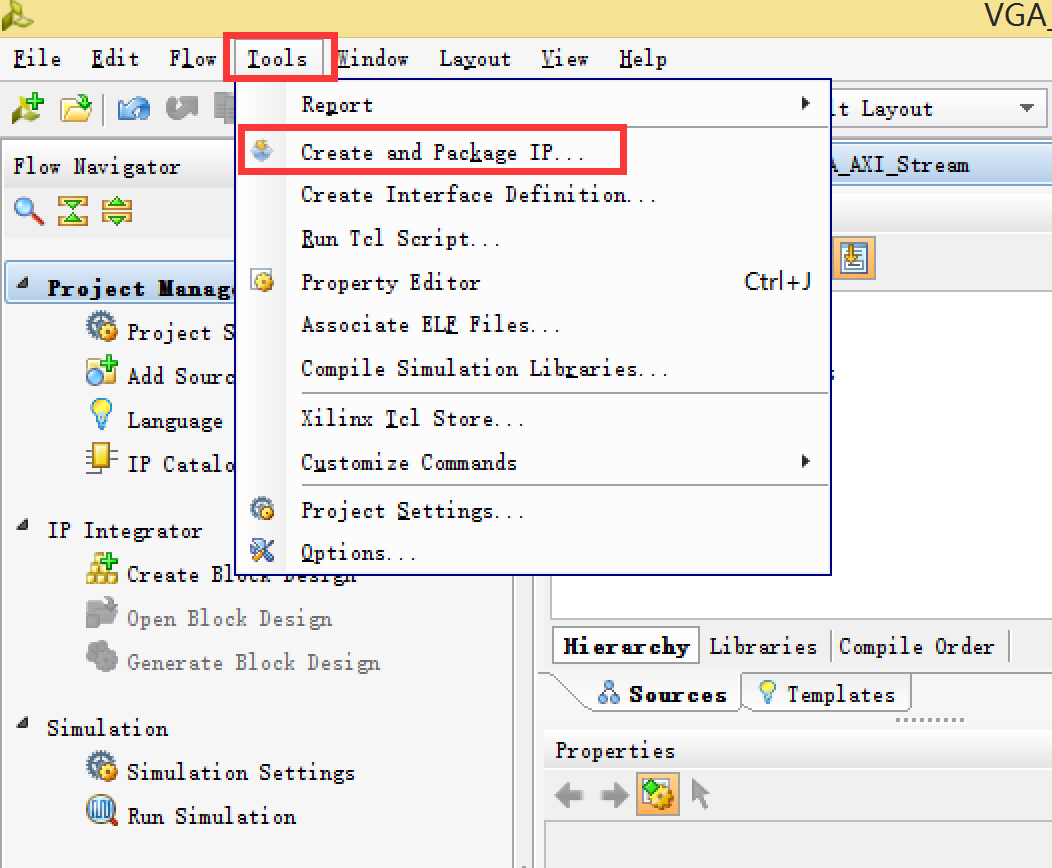

选择Tools->Create and Package IP

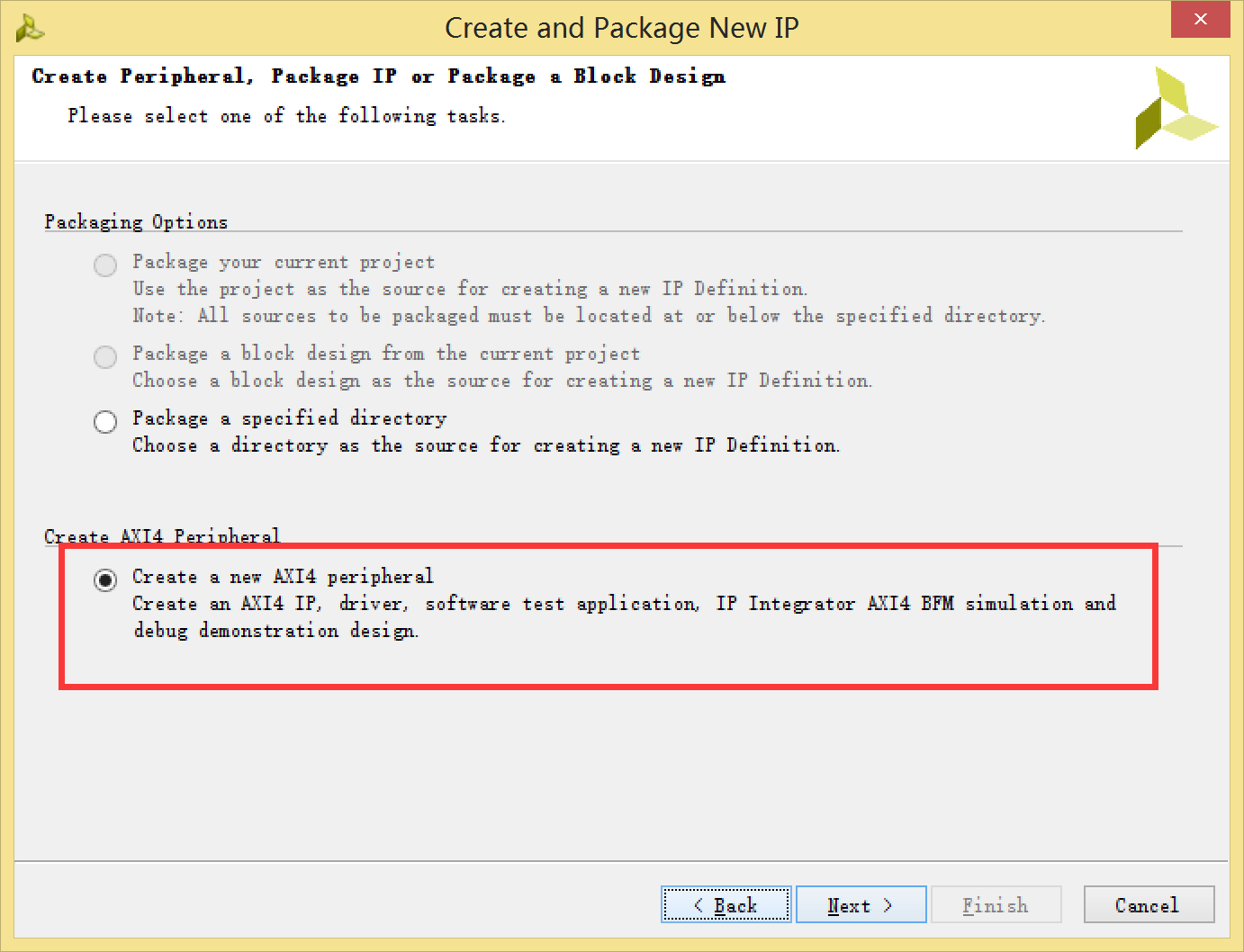

点击NEXT,选择Create AXI4,如图所示

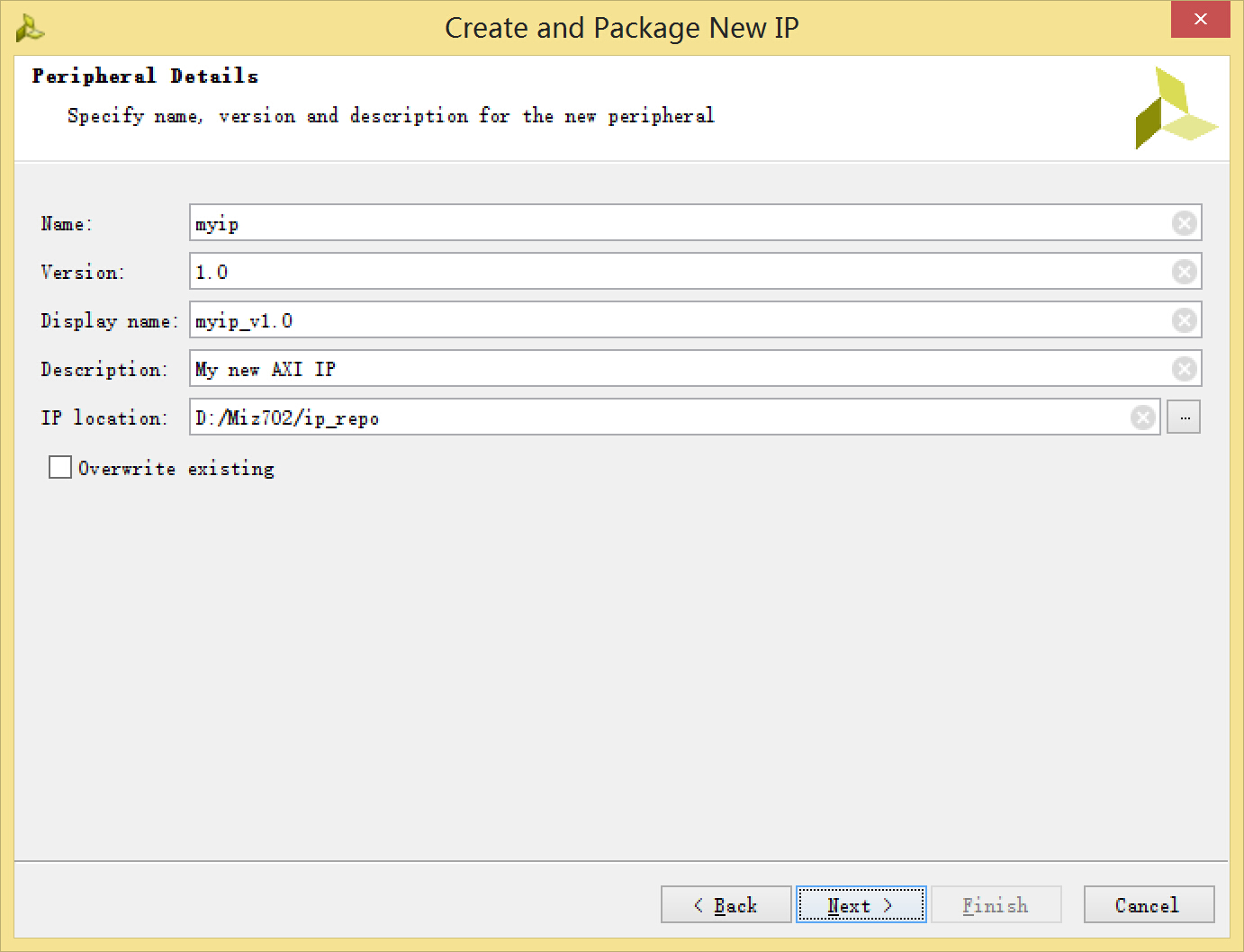

输入好name和路径后,点击NEXT

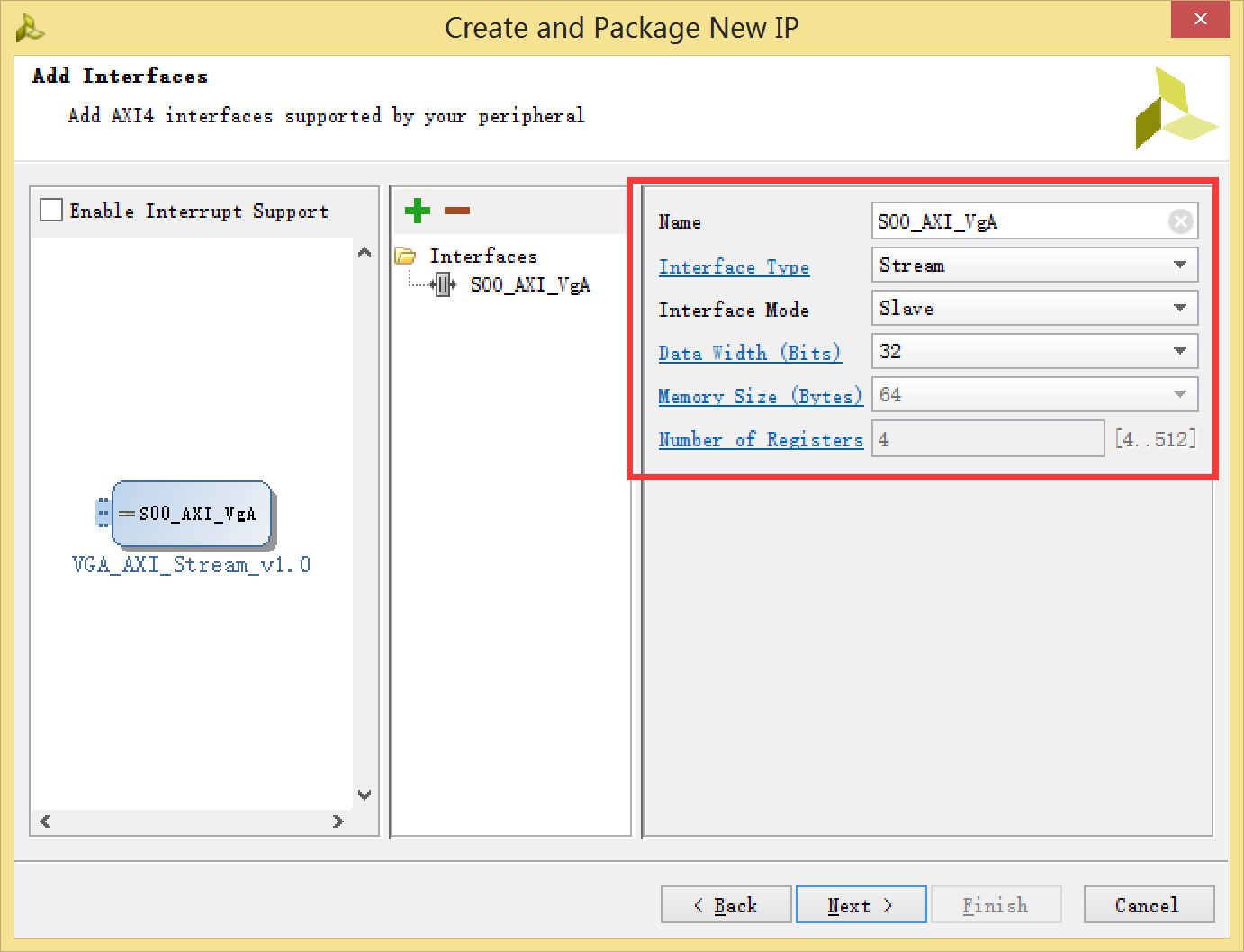

按照如下配置

点击NEXT,选择Edit IP,然后点击Finish

这时会弹出一个新的IP 编辑界面,这个可以看到VIVADO已经自动生成了一些必要的AXI Stream相关的代码,我们在这个基础上修改很方便

把VGA_AXI_Stream_v1_0.v文件里的代码,修改如下

`timescale 1 ns / 1 ps

module myip_v1_0 #

(

// Users to add parameters here

// User parameters ends

// Do not modify the parameters beyond this line

// Parameters of Axi Slave Bus Interface S00_AXIS_VGA

parameter integer C_S00_AXIS_VGA_TDATA_WIDTH = 32

)

(

// Users to add ports here

input wire clk_25mhz,

output wire hsync,

output wire vsync,

output wire [11:0] rgb,

output reg led,

// User ports ends

// Do not modify the ports beyond this line

// Ports of Axi Slave Bus Interface S00_AXIS_VGA

input wire s00_axis_vga_aclk,

input wire s00_axis_vga_aresetn,

output wire s00_axis_vga_tready,

input wire [C_S00_AXIS_VGA_TDATA_WIDTH-1 : 0] s00_axis_vga_tdata,

input wire [(C_S00_AXIS_VGA_TDATA_WIDTH/8)-1 : 0] s00_axis_vga_tstrb,

input wire s00_axis_vga_tlast,

input wire s00_axis_vga_tvalid,

input wire s00_axis_vga_tuser

);

// Instantiation of Axi Bus Interface S00_AXIS_VGA

myip_v1_0_S00_AXIS_VGA # (

.C_S_AXIS_TDATA_WIDTH(C_S00_AXIS_VGA_TDATA_WIDTH)

) myip_v1_0_S00_AXIS_VGA_inst (

.S_AXIS_ACLK(s00_axis_vga_aclk),

.S_AXIS_ARESETN(s00_axis_vga_aresetn),

.S_AXIS_TREADY(s00_axis_vga_tready),

.S_AXIS_TDATA(s00_axis_vga_tdata),

.S_AXIS_TSTRB(s00_axis_vga_tstrb),

.S_AXIS_TLAST(s00_axis_vga_tlast),

.S_AXIS_TVALID(s00_axis_vga_tvalid),

.S_AXIS_TUSER(s00_axis_vga_tuser),

.clk (clk_25mhz),

.rst_n (s00_axis_vga_aresetn),

.video_en (video_en),

.h

该博客详细介绍了如何将VGA的RTL代码封装为AXI Stream,以便在ZYNQ-7000开发板上使用TPG进行测试。通过Vivado创建和配置IP,修改必要的源代码,然后在硬件工程中应用,最终在开发板上实现了25MHz时钟的Color Bar效果。

该博客详细介绍了如何将VGA的RTL代码封装为AXI Stream,以便在ZYNQ-7000开发板上使用TPG进行测试。通过Vivado创建和配置IP,修改必要的源代码,然后在硬件工程中应用,最终在开发板上实现了25MHz时钟的Color Bar效果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6571

6571

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?