应用PlanAhead进行I/O规划

一、 建立I/O引脚规划项目

下面通过一个简单的实例介绍如何创建PlanAhead项目,进行I/O规划。

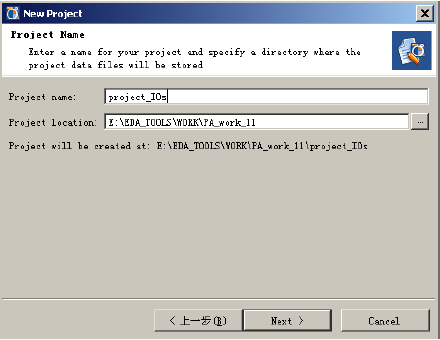

1. 在PlanAhead的开始界面中单击【Create a New Project】,在弹出的窗口中单击【Next】按钮,出现图10-38所示的新项目窗口。在此窗口中输入项目名和路径。

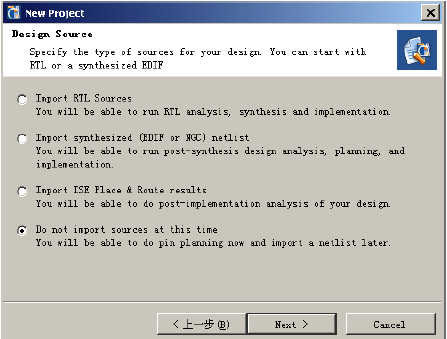

2. 单击【Next】,出现图10-39所示窗口,选择新项目类型,这里选择【Do not import sources at this time】。

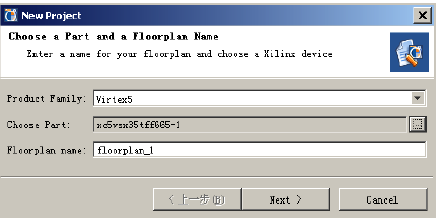

3. 单击【Next】按钮弹出图10-40所示对话框,使用默认值。

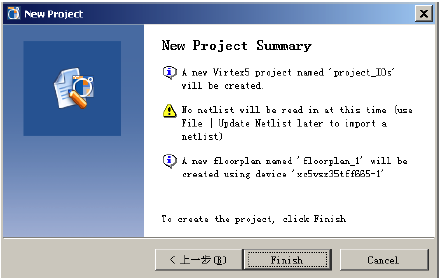

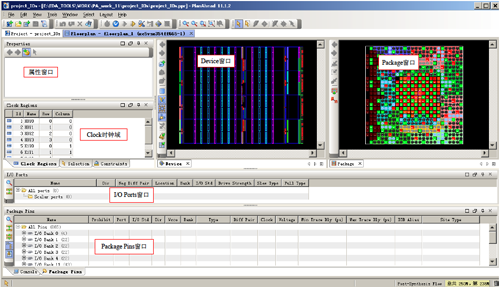

4. 单击【Next】打开图10-41所示新项目总结对话框,单击【Finish】按钮,完成新项目的建立。默认的I/O规划窗口如图10-42所示。

二、 检查器件的I/O 资源

1. 交叉定位功能。

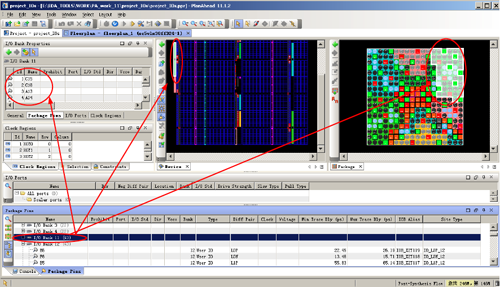

在图10-43 的【Package Pins】窗口选择一个I/O Bank 或者选择一个I/O Pin,工具会将选中的对象定位到【Device 】或【Package 】的对应部位, 并高亮显示, 而且在【Properties】和【Clock Regions】窗口显示相应的资源属性和时钟域信息。

与Package Pins 交叉定位功能类似,在【Clock Regions】选择某个对象,在其他几个窗口也可以定位并高亮显示相应的对象。如图10-44 所示。

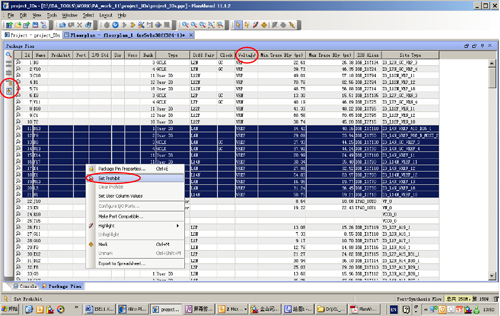

2. 设置禁止I/O 分配。

最大化【Package Pins】,如图10-45 所示,  和

和 按钮配合,完成对器件引脚的

按钮配合,完成对器件引脚的

排序,如图中我们将所有VREF 引脚排在一起,选中所有VREF 引脚,右键功能选择【Set Prohibit】,禁止所有VREF 引脚的分配。

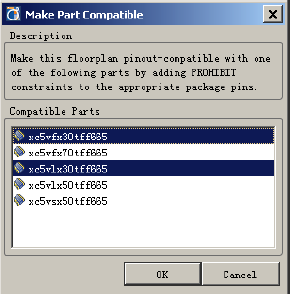

三、 定义兼容器件

在FPGA 设计开发阶段,PlanAhead 允许设计者定义互相兼容的芯片,这种方式可以将一个I/O约束应用于多个FPGA。

在【Device】或者【Package】窗口,在右键弹出菜单中选择【Make Part Compatible…】,选择互相兼容的器件。如图10-46。

四、 导入、分析I/O端口列表

PlanAhead能够导入多种不同格式的文件用于I/O引脚的规划。在产生综合网表之前,可以导入CSV、UCF和RTL格式的文件进行I/O引脚的分析和分配。但需要注意的是,使用这种早期I/O引脚规划方法的时候,因为没有综合网表,I/O分配工具和DRC校验工具不清楚设计中的时钟和各时钟之间的关系,也不清楚高速逻辑的具体情况,所以其分析并不完整。如果可能的话,导入综合网表后,再进行I/O分配。

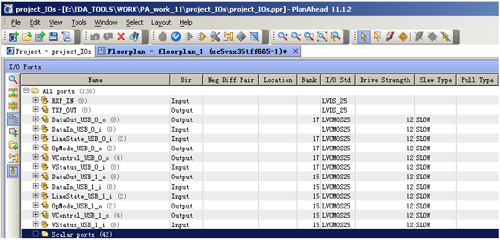

运行命令【File】→【Import I/O Port…】→【From CSV…】导入CSV格式文件,CSV文件目录是PlanAhead_Tutorial\Sources\IO_port_import.csv。最大化【I/O Ports】窗口,如图10-47所示,可以看到默认情况下所有Ports的分布。单击【I/O Ports】窗口旁边的 按钮,观察端口排列的变化。图中显示了各个端口的常用属性。

按钮,观察端口排列的变化。图中显示了各个端口的常用属性。

五、 清除导入的I/O约束

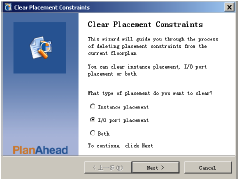

设计者可以在【Clock Regions】窗口、【I/O Ports】窗口或者【Package Pins】窗口选择一个或多个对象,或者单击 按钮取消所有选择,再运行【Tools】→【Clear Placement Constraints】命令,打开图10-48所示窗口,其中有三个选项,【Instance placement】清除实例的布局规划,【I/O port placement】清除I/O端口布局规划,【Both】上述两种对象均清除。

按钮取消所有选择,再运行【Tools】→【Clear Placement Constraints】命令,打开图10-48所示窗口,其中有三个选项,【Instance placement】清除实例的布局规划,【I/O port placement】清除I/O端口布局规划,【Both】上述两种对象均清除。

在这个例子中,我们在【Package Pins】窗口选中一个指定的Pin脚,以选择【I/O port placement】为例。

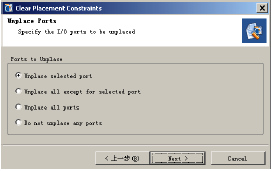

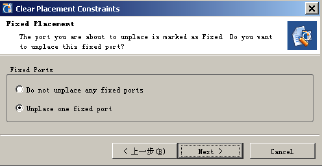

单击【Next】按钮,打开图10-49所示对话框。选择【Unplace selected port】选项,单击【Next】,打开图10-50所示对话框,选中【Unplace one fixed port】,单击【Next】按钮,在出现的窗口单击【Finish】,清除一个I/O约束。

需要注意的是,这里的操作过程会随着设计者是否选择了对象,选择了几个对象,操作界面稍微有所不同。

六、 建立、配置I/O端口

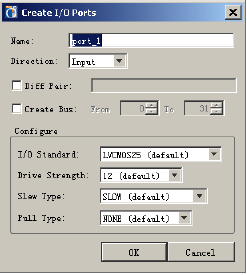

在【I/O ports】窗口的右键菜单中选择【Create I/O Ports…】,弹出图10-51所示对话框,输入端口名如port_1,可以更改端口属性,也可以建立总线类型的端口。单击【OK】按钮,可以看到【I/O ports】窗口增加了一个端口。

配置I/O端口的操作方式与此类似,在右键菜单中选择【Configure I/O Ports…】即可。

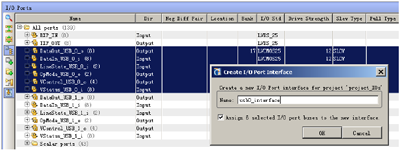

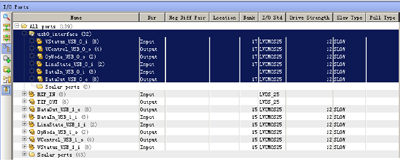

七、 建立I/O端口的管理接口

最大化【I/O Ports】窗口,选择所有*USB_0*的端口,运行右键菜单命令【Create I/O Port Interface…】,在弹出的对话框中输入usb0_interafce,如图10-52,单击【OK】,可以看到,这些*USB_0*端口有了一个管理接口,名为usb0_interface,如图10-53。使用这个方法,可以方便PCB管理。

八、 分配I/O端口

PlanAhead提供了多种分配I/O端口的方法,可以自动分配,也有几种半自动分配方式,如将I/O端口分配到一个I/O Bank中【Place I/O Ports in an I/O Bank】,将I/O端口分配到一个指定的区域【Place I/OPorts in an Area】,和顺序分配I/O端口【Place I/O Ports Sequentially】。

需要注意,为了保证I/O分配的正确性,需要在执行I/O分配之前,打开I/O分配自动DRCs校验功能。执行【Tools】→【Options】→【General】,打开【Automatically enforce legal I/O placement】功能。

1. 自动分配I/O端口。

运行【Tools】→ 【Autoplace I/O Ports】即可完成I/O端口的自动分配。

2. 将I/O端口放置到一个I/O Bank中。

在图10-53所示的【I/O ports】窗口选择usb0_interface端口,在右键菜单中运行【Place I/O Ports in an I/O Bank】,或者在【Package】窗口单击 按钮,可以看到与usb0_interafce相关的引脚都粘贴到鼠标上,在【Package】窗口拖动鼠标,找到合适的位置后单击鼠标左键,就可以完成I/O 端口的分配。

按钮,可以看到与usb0_interafce相关的引脚都粘贴到鼠标上,在【Package】窗口拖动鼠标,找到合适的位置后单击鼠标左键,就可以完成I/O 端口的分配。

清除对usb0_interface 端口的分配,以方便进行下面的操作。

3. 将I/O 端口放置到一个区域中。

在图10-53 所示的【I/O ports】窗口选择usb0_interface 端口,在右键菜单中运行【Place I/O Ports in an Area】,或者在【Package】窗口单击 按钮,这时可以在【Package】窗口拖动鼠标,画出一个适合放置所有I/O 端口的矩形框,释放鼠标,即可完成I/O 端口的分配。

按钮,这时可以在【Package】窗口拖动鼠标,画出一个适合放置所有I/O 端口的矩形框,释放鼠标,即可完成I/O 端口的分配。

清除对usb0_interface 端口的分配,以方便进行下面的操作。

4. 顺序放置I/O 端口。

在图10-53 所示的【I/O ports】窗口选择usb0_interface 端口,在右键菜单中运行【Place I/O Ports Sequentially】,或者在【Package】窗口单击 按钮,这时可以在【Package】窗口拖动鼠标,按顺序放置所有I/O 端口,直到分配完所有的I/O 端口。需要说明的是,这里描述的是综合前I/O 端口分配,应用的是CSV 文件,没有综合网表,时钟引脚、高速收发器和差分对不会被工具自动处理,因此,进行此类引脚分配时需要特别注意。

按钮,这时可以在【Package】窗口拖动鼠标,按顺序放置所有I/O 端口,直到分配完所有的I/O 端口。需要说明的是,这里描述的是综合前I/O 端口分配,应用的是CSV 文件,没有综合网表,时钟引脚、高速收发器和差分对不会被工具自动处理,因此,进行此类引脚分配时需要特别注意。

九、 分配高速收发器和时钟逻辑

可以将综合后网表文件导入PlanAhead,然后在PlanAhead 中完成关键时钟,以及相关联的I/O 端口的分配。例如: PlanAhead 可以对某些逻辑进行分组,像高速收发器(Gigbit Transceiver,简称GT),以及相关联的I/O 对,再对这些分组进行逻辑位置的规划、端口的分配等操作。

完成分配,PlanAhead 还可以对完成的设计网表进行DRC、WASSO 校验,以防止规划出错。

打开一个基于网表的项目,完成逻辑对象布局及I/O 端口的分配。

1. 在PlanAhead 中运行【File 】→ 【Open Project 】, 打开如下文件

PlanAhead_Tutorial/Projects/project_cpu_netlist/project_cpu_netlist.ppr。

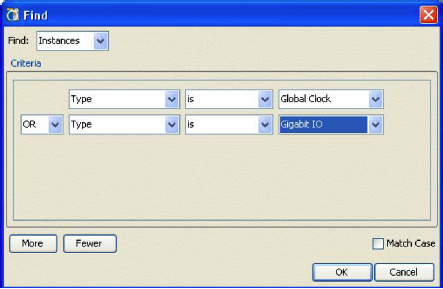

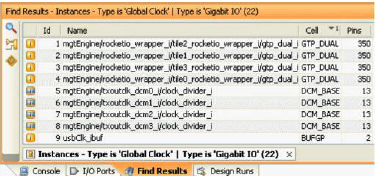

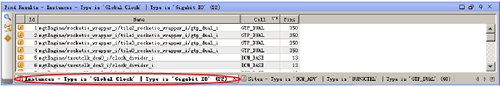

2. 切换到【Floorplan – io_planning_fp】窗口,运行【Edit】→【Find…】,打开图10-54 所示的查找对话框,按图中所示设置,单击【OK】。在查找结果中,单击【Cell】列两次,就会看到图10-55 所示结果,图中显示了项目中用到的时钟以及高速I/O 资源。

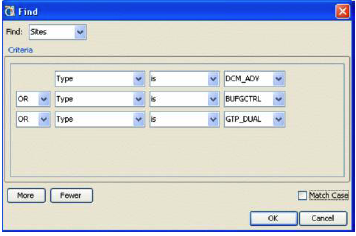

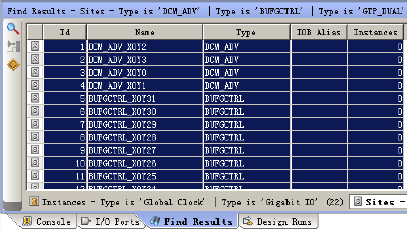

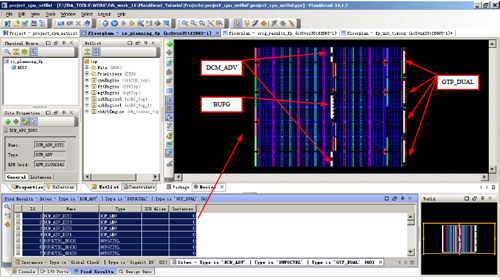

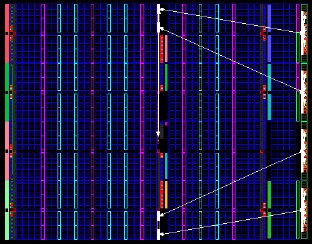

3. 再查找一次,按图10-56 所示设置查找选项,单击【OK】开始查找。图10-57为查找结果,选择所有查找结果,可以在【Device】窗口看到所选元素在器件中的具体位置,如图10-58 所示。

4. 创建位置约束。

在查找窗口选择Instance 标签,如图10-59 所示。可以看到设计中用到的全局时钟、高速I/O 资源。在【Device】窗口选择 按钮,在Device 中创建位置约束。在查找窗口选择第一个GTP_DUAL,按住鼠标左键不放,将其拖放到图10-60 所示的GTP_DUAL 区域,当鼠标由圆形变为加号时,说明找到一个合适的位置,释放左键,这样就完成了一个对象的位置。用同样的方法放置剩余的对象,包括DCM 和BUFG。

按钮,在Device 中创建位置约束。在查找窗口选择第一个GTP_DUAL,按住鼠标左键不放,将其拖放到图10-60 所示的GTP_DUAL 区域,当鼠标由圆形变为加号时,说明找到一个合适的位置,释放左键,这样就完成了一个对象的位置。用同样的方法放置剩余的对象,包括DCM 和BUFG。

需要注意的是,由于DCM 和BUFG 是相互关联的,所以放置DCM 和BUFG 时,相关联的对象要靠近放置。

完成位置约束的【Device】视图,如图10-60 所示。

十、 设计规则DRC 和同步翻转噪声WASSO 检查

在PlanAhead 中可以完成DRC 和WASSO(Weighted Average Simultaneously Switching Noise)的检查。

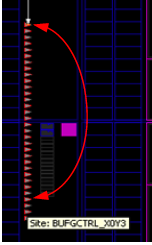

1. 在工具栏单击 运行DRC 检查,弹出图10-61 窗口,按照图中所示设置各参数,单击【OK】按钮,开始DRC 检查。检查结果如图10-62 所示,有一个错误,从【Violation Properties】窗口可以看到,错误的原因是因为DCM 在DCM_ADV_X0Y3 位置,而BUFG 在BUFGCTRL_X0Y5 位置,并提示要纠正此错误,需要将DCM 和BUFG 放置在相同的半边区域内。因为X0Y3 位于器件中部上半部分,所以只需要将BUFG 约束到上半部分就可以了。

运行DRC 检查,弹出图10-61 窗口,按照图中所示设置各参数,单击【OK】按钮,开始DRC 检查。检查结果如图10-62 所示,有一个错误,从【Violation Properties】窗口可以看到,错误的原因是因为DCM 在DCM_ADV_X0Y3 位置,而BUFG 在BUFGCTRL_X0Y5 位置,并提示要纠正此错误,需要将DCM 和BUFG 放置在相同的半边区域内。因为X0Y3 位于器件中部上半部分,所以只需要将BUFG 约束到上半部分就可以了。

在Virtex-5 器件中,BUFG 分布在器件的中心位置,而且分为上半部分和下半部分。上半部分BUFG 供芯片顶部DCM 用,下半部分BUFG 供芯片底部DCM 用。图10-63 所示为BUFG 修改后的位置。再次运行DRC,会弹出【No violation found】对话框。

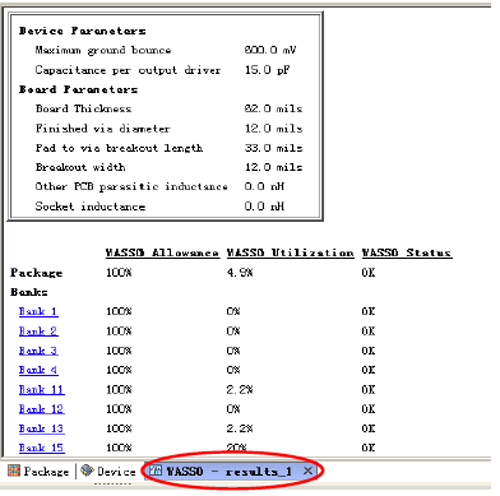

2. 运行【Tools】→【Run WASSO Analysis】,在弹出的对话框中使用默认值,单击【OK】,开始进行WASSO 分析,分析结果如图10-64 所示。

十一、 导出器件和I/O 引脚配置文件

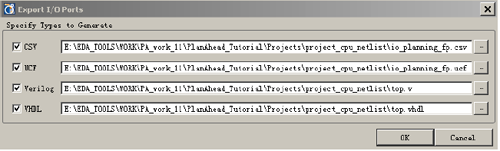

运行【File】→【Export I/O Ports】命令,弹出图10-65 所示对话框,设置要导出的文件。

1770

1770

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?