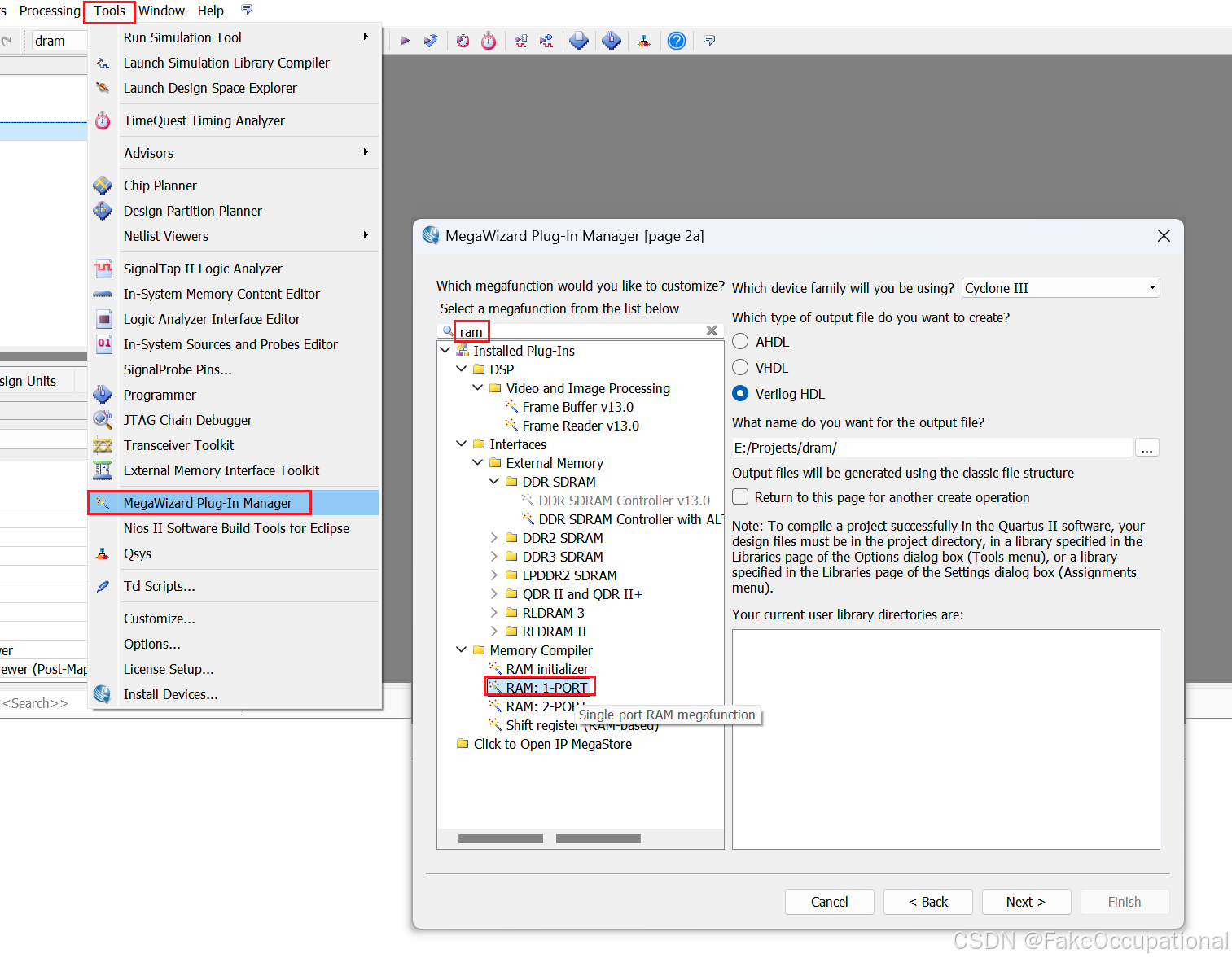

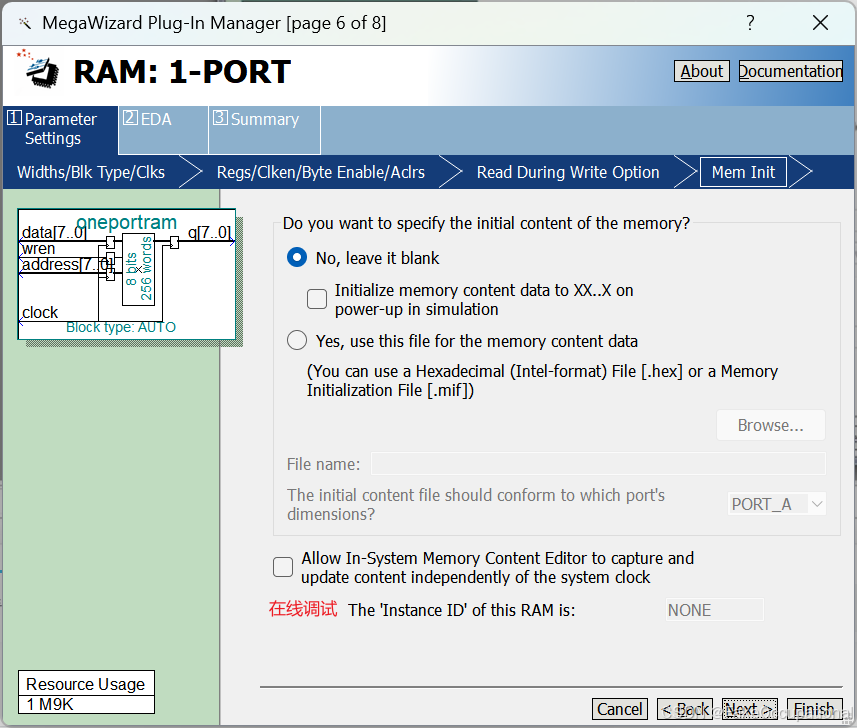

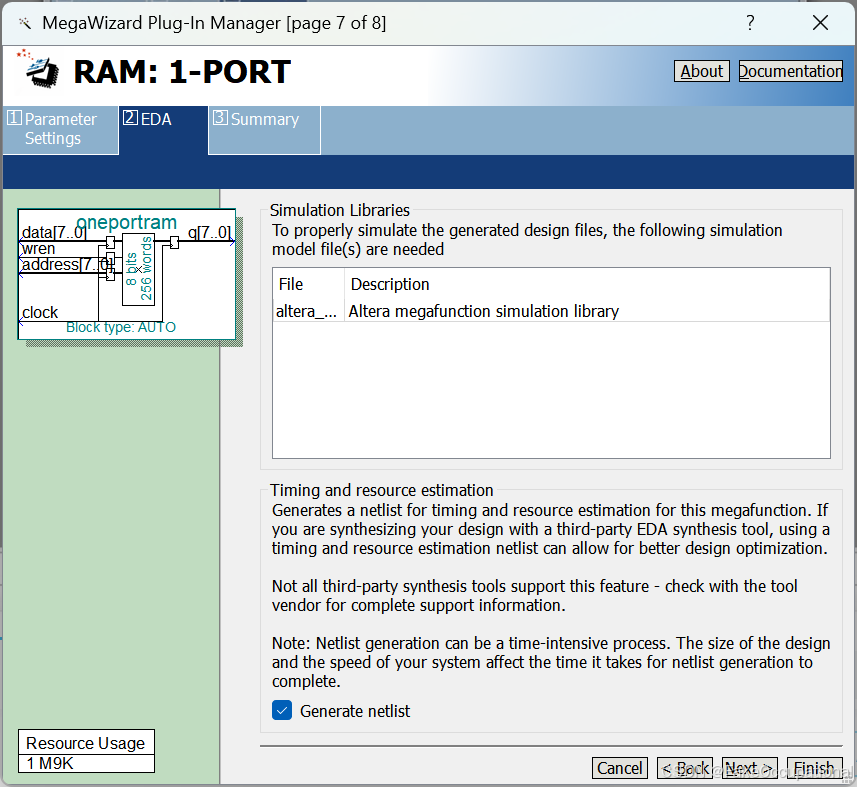

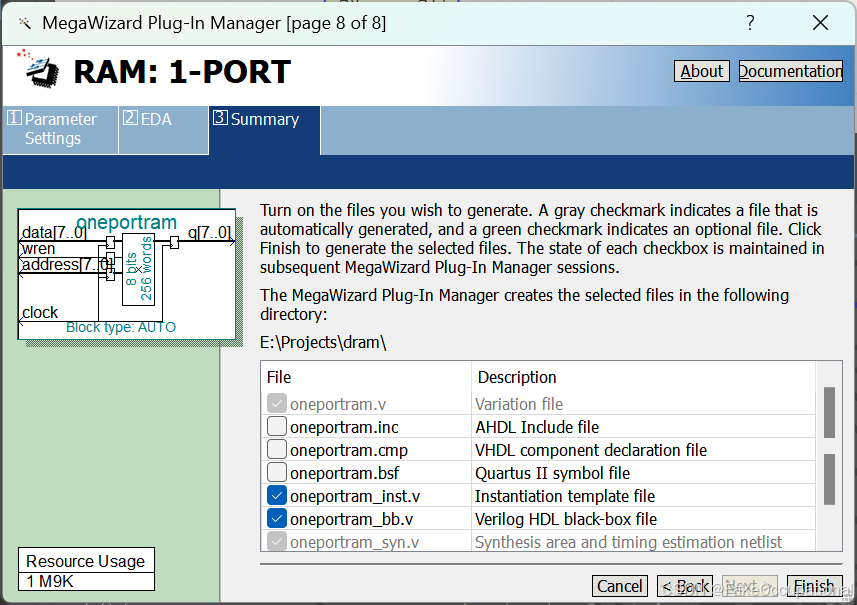

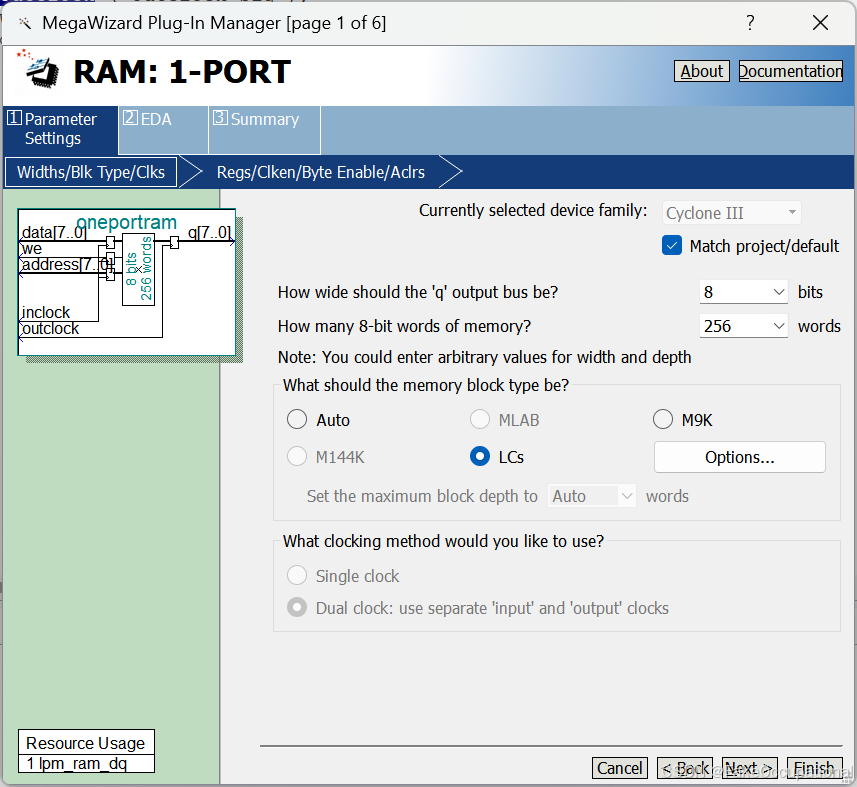

创建RAM模块

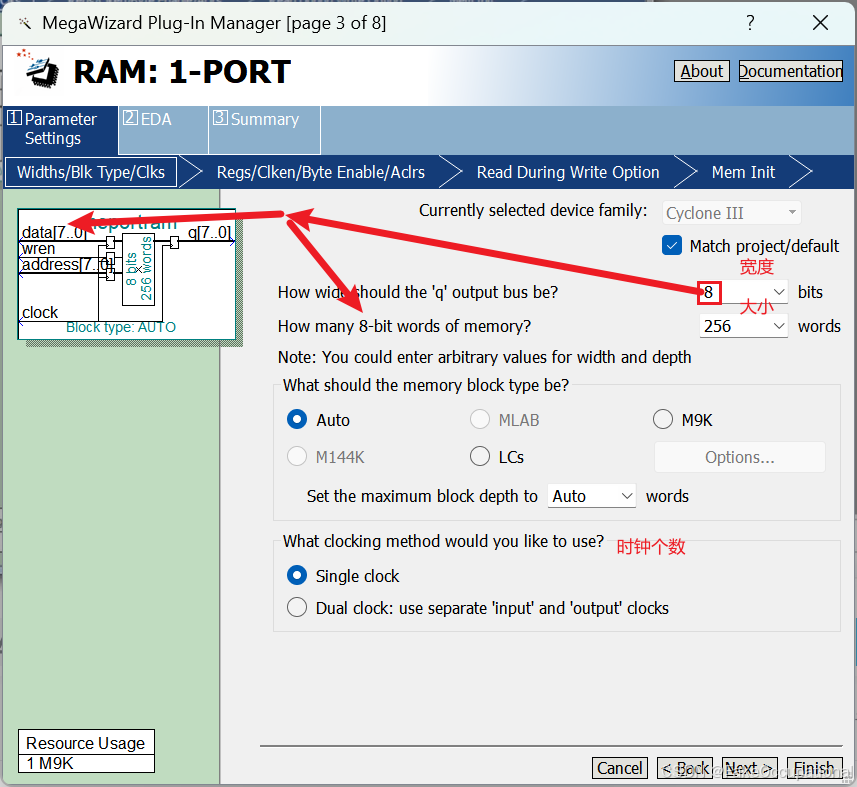

- 配置数据宽度和RAM的大小

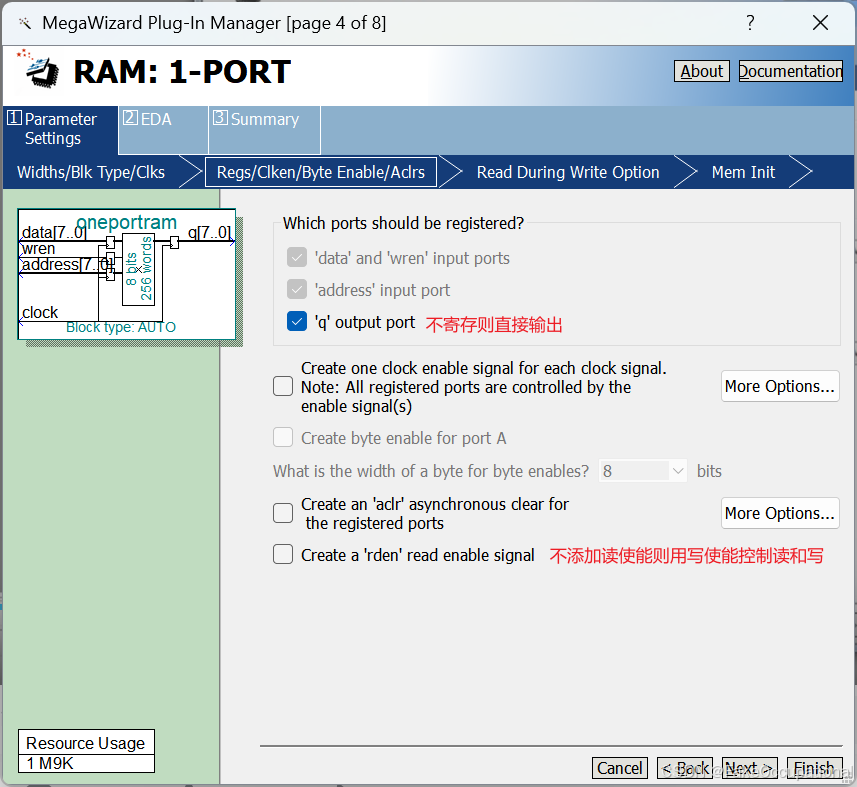

- 下面的复选框用于在线调试

实例化模块代码

// 顶层模块

module dram (

input wire clk, // 时钟信号

input wire wr_en, // 写使能信号

input wire [ADDR_WIDTH-1:0] addr, // 地址总线

input wire [DATA_WIDTH-1:0] data_in, // 数据输入

output wire [DATA_WIDTH-1:0] data_out // 数据输出

);

// 参数定义

parameter ADDR_WIDTH = 8; // 地址宽度,根据需要调整

parameter DATA_WIDTH = 8; // 数据宽度,根据需要调整

// 内部信号声明

wire clock_sig;

wire wren_sig;

wire [ADDR_WIDTH-1:0] address_sig;

wire [DATA_WIDTH-1:0] data_sig;

wire [DATA_WIDTH-1:0] q_sig;

// 将顶层模块的端口连接到内部信号

assign clock_sig = clk;

assign wren_sig = wr_en;

assign address_sig = addr;

assign data_sig = data_in;

assign data_out = q_sig;

// 实例化单端口RAM

oneportram oneportram_inst (

.address ( address_sig ),

.clock ( clock_sig ),

.data ( data_sig ),

.wren ( wren_sig ),

.q ( q_sig )

);

endmodule

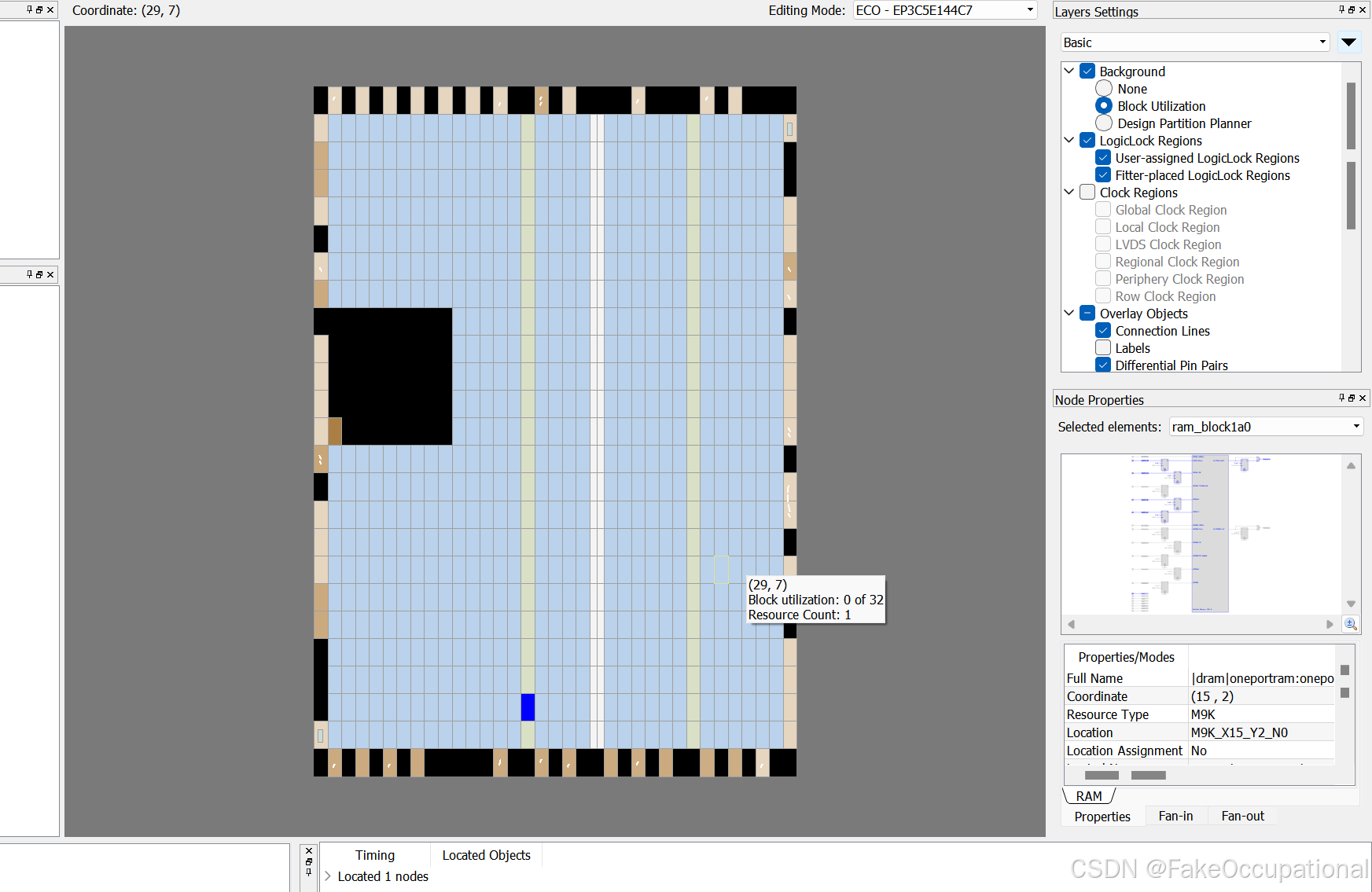

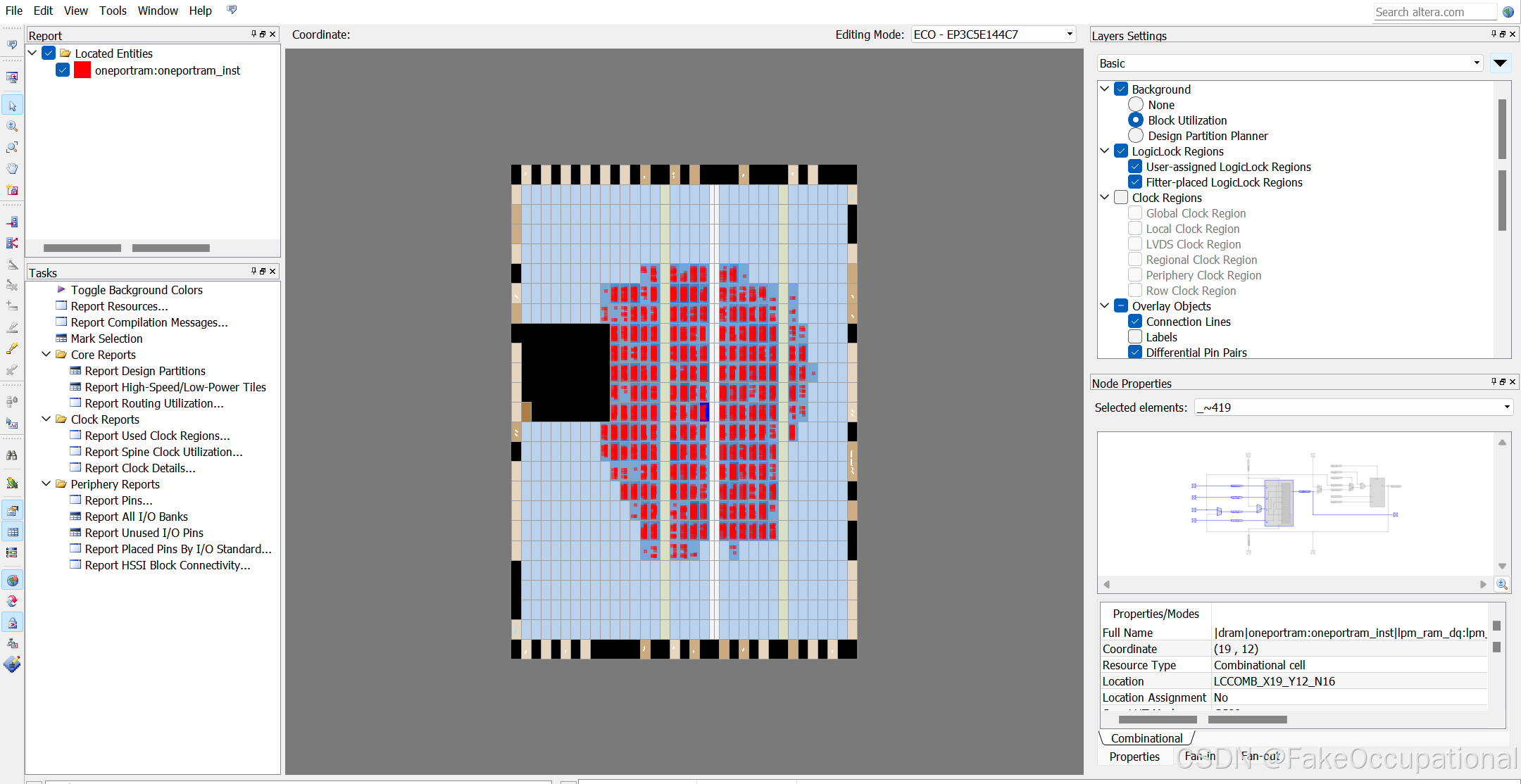

效果

- RAM (Random Access Memory) IP使用芯片内部的资源实现,在Cyclone III 系列芯片中,可通过嵌入式块RAM(BRAM)或 LUT实现。可在chip planer中显示具体实现:

eRAM实现(Embedded RAM,嵌入式RAM)

- eRAM(Embedded RAM,嵌入式RAM) 直接集成在芯片内部的存储器模块(eRAM 通常是 SRAM)

- 在Cyclone IV系列芯片中,嵌入式块RAM(BRAM)的结构都是M9K,当然在进行设计时,如果我们的逻辑资源足够,我们也可以使用逻辑资源(也就是分布式RAM)。如果逻辑资源紧张,可以指定使用BRAM。

LUT实现(Distributed RAM)

- 将数据存储在LUT中,在iCE40LPHXFamilyDataSheet和其他一些文献中将这种方法称为分布式RAM(Distributed RAM)实现。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?