根据FPGA的封装不同,不同型号的FPGA的引脚多少和定义都有所区别,那么在工程中,管脚应该如何配置呢?不用的管脚又该如何设置呢?下面来总结一下。

FPGA的管脚一般分为两大类:专用管脚(占比20%-30%)和用户自定义管脚(占比70%-80%)

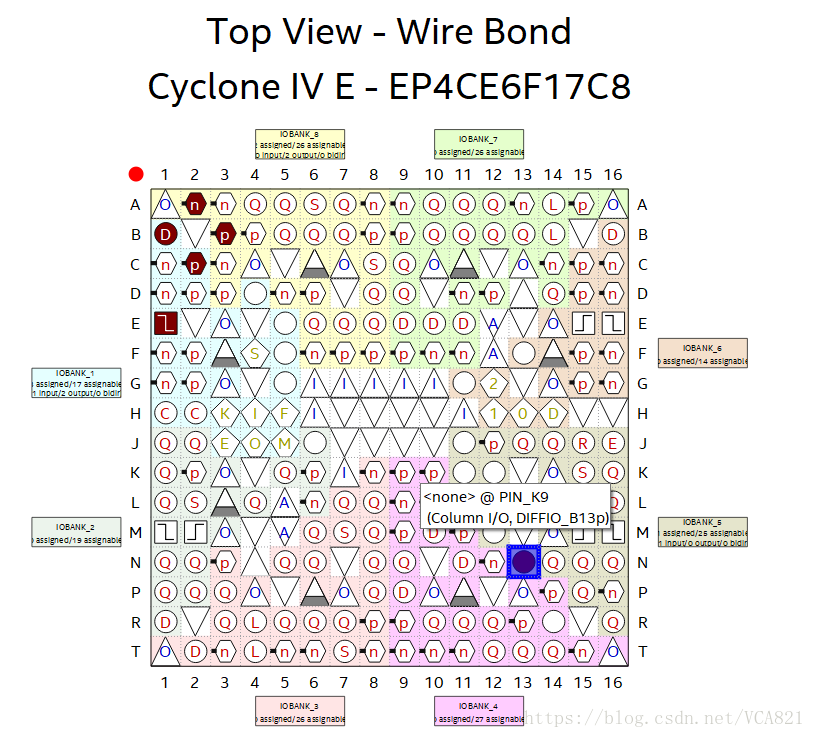

根据功能分为时钟,配置,普通IO,电源四种管脚。以下图为例(黑金AX301,EP4CE17C8)

不同颜色代表不同bank,三角形为电源管脚(正三角为VCC,倒三角为GND,三角中为O则是IO电源管脚,为I则为内核电源),圆形标记的管脚为普通IO管脚,可以随意使用,正方形且内部有时钟信号的为全局时钟管脚,五边形管脚为配置管脚。

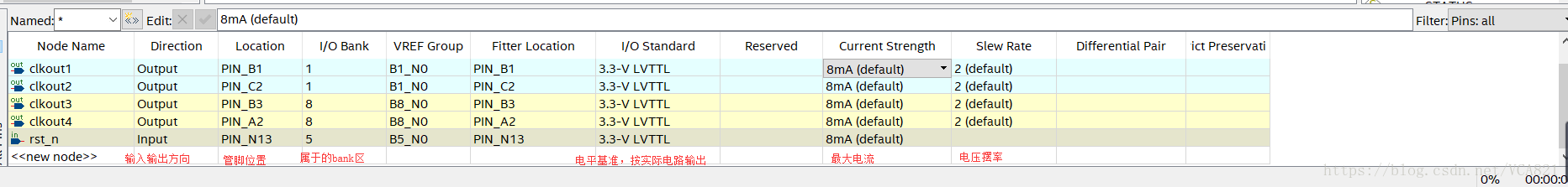

管脚设置

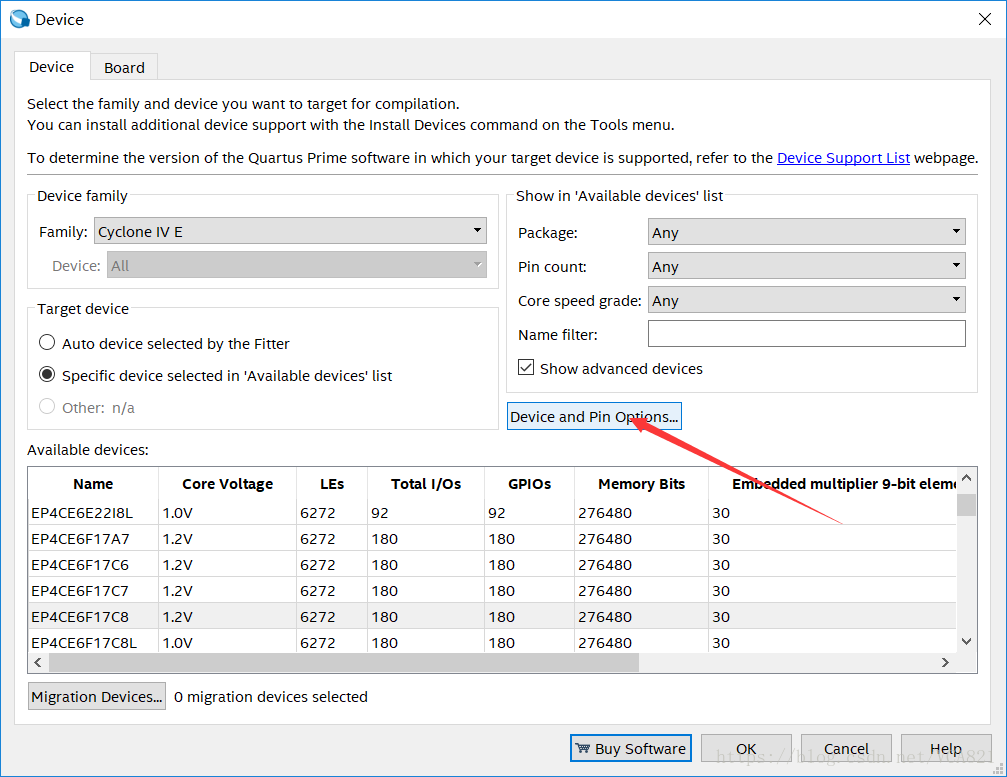

点进去后“Device and Pin Options”在“Unused Pins”选项中"Reserve unused pins",设置为“"As input tri-stated",这里是把没有使用的管脚做为三态输入。

在“Voltage”选项,将“Default I/O standard:”设置为“3.3-V LVTTL”,这个设置是和 FPGA 硬件设计的 bank 电压有关,大部分开发板的 IO BNAK 电压为 3.3V,所以设置为“3.3-V LVTTL”。输出电压和设置没有关系,如果 BANK 电压是 3.3V,你这里设置 2.5V,也不会改变 IO 输出的电压幅度。这里设置完成以后 IO 的默认电压为“3.3-V LVTTL”,我们也可以根据需要为每个 IO 分配不一样的 IO 电平标准。

多用途管脚设置。在选项“Dual-Purpose Pins”中设置多用途 IO,全部做为普通 IO。这些多用途管脚,在 FPGA 配置阶段有特殊用途,配置完成后可以做为普通 IO。

学习参考文献 《quartus ii中fpga管脚分配策略》 http://www.docin.com/p-1505838804.html

1831

1831

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?