要求:实现一个异步复位,同步释放电路。复位信号低有效。

零、分析

改电路的优点是复位信号不受时钟限制,并且又有效减少了亚稳态发生的概率(如果复位信号在时钟上升沿撤销,则有可能产生亚稳态)。核心思想:寄存器打一拍防止亚稳态。

一、Verilog代码

module Sys_rst (

input clk,

input rst_n,

output reg rst0,

output reg rst1,

output sys_rst

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

rst0 <= 1'b0;

rst1 <= 1'b0;

end

else begin

rst0 <= 1'b1;

rst1 <= rst0;

end

end

assign sys_rst = rst1;

endmodule

二、test bench

`timescale 1ns/1ps

module Sys_rst_tb;

parameter clock_cycle = 20;

reg clk;

reg rst_n;

wire rst1;

wire rst0;

wire sys_rst;

initial begin

clk = 0;

rst_n = 1;

#clock_cycle rst_n = 0;

#(clock_cycle/2);

#clock_cycle rst_n = 1;

end

always #(clock_cycle/2) clk = ~clk;

Sys_rst Sys_rst_1(

.clk (clk),

.rst_n (rst_n),

.rst0 (rst0),

.rst1 (rst1),

.sys_rst (sys_rst)

);

endmodule

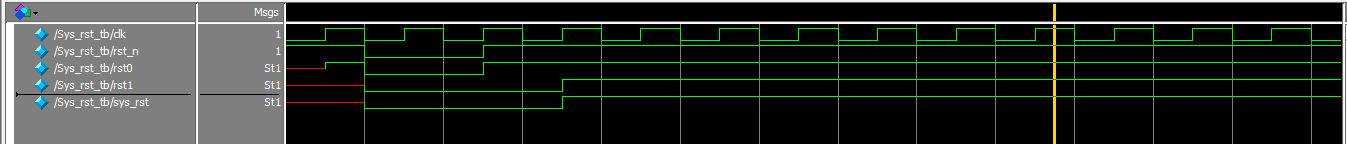

三、仿真波形

2283

2283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?