要求:设计一个50%占空比的3分频器

总结:设计奇数N分频的核心思想是,用计数器产生两个(N/2+1)/N占空比的时钟信号(分别在系统时钟的上升沿和下降沿产生)。在将这两个信号做组合逻辑运算(与运算)。

延伸:50%占空比的5分频。

计数器可以从0计数到2时翻转一次,到4时再翻转一次(也可以在1和3翻转)。这样就产生了一个3/5占空比的时钟。

以下为3分频器的实验代码,可以自己试试实现其他奇数倍分频器。

一、Verilog代码

module Frequency_divider3 (

input clk,

input rst_n,

output div3,

output reg clk1, //此处的clk2信号是为了在仿真中可见

output reg clk2 //此处的clk2信号是为了在仿真中可见

);

reg [1:0] count;

always@(posedge clk) begin

if (!rst_n)

count <= 2'b0;

else if(count == 2'd2)

count <= 2'd0;

else

count <= count + 1;

end

always@(posedge clk) begin

if (!rst_n)

clk1 <= 1'b1;

else if(count == 2'd1 | count == 2'd2)

clk1 <= ~clk1;

else

clk1 <= clk1;

end

always @(negedge clk ) begin

if (!rst_n)

clk2 <= 1'b1;

else if(count == 2'd1 | count == 2'd2)

clk2 <= ~clk2;

else

clk2 <= clk2;

end

assign div3 = clk1 & clk2;

endmodule

二、test bench

`timescale 1ns/1ps

module Frequency_divider3_tb;

parameter clock_cycle = 20;

reg clk;

reg rst_n;

wire div3;

initial begin

clk = 0;

rst_n = 1;

#clock_cycle rst_n = 0;

#clock_cycle rst_n = 1;

end

always #(clock_cycle/2) clk = ~clk;

Frequency_divider3 div3_half_duty(

.clk (clk),

.rst_n (rst_n),

.div3 (div3),

.clk1 (clk1),

.clk2 (clk2)

);

endmodule

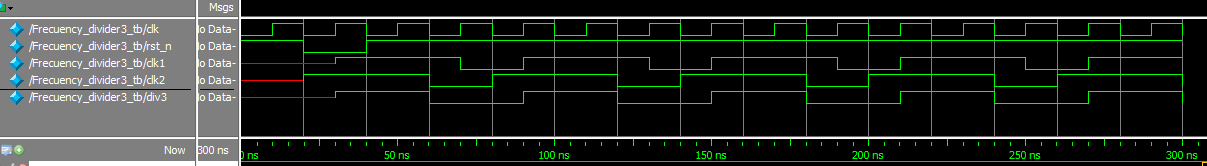

三、modulesim 仿真结果

789

789

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?