最近在用vivado实现DDR3存储的项目,正在学习MIG这个IP核的使用,发现配置好了在仿真过程中init_calib_complete这个信号一直没有拉高。一定要读懂xilinx的例程!不是生搬硬套网上的视频教程!看看自己的位宽到底要几片ddr3!

主要情况如下:

example_top 里面的init_calib_complete可以拉高,并且读写时序均可以正常跑起来,但是自己例化就不行了。

仔细对比一下才知道,网上的例程没有说清楚啊!

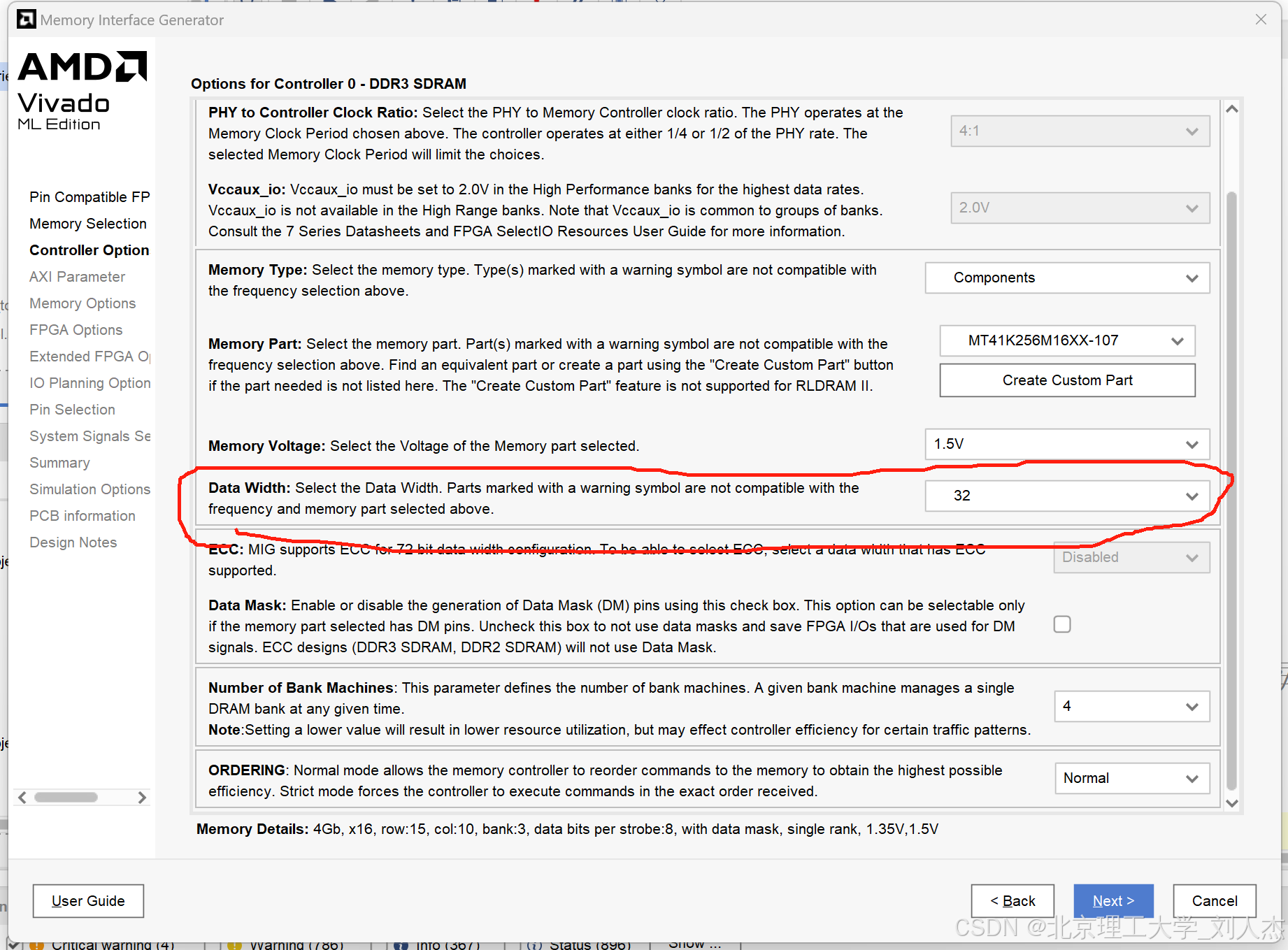

由于我是有实际电路板的,而电路板上有32位的数据位宽,我选择的ddr3是32位的数据位宽:

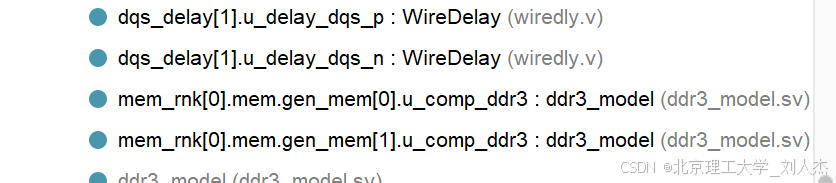

然后我就按照网上的例程,把ddr3_model 那两个文件复制过来,并且例化,最后init_calib_complete就一直无法拉高!

仔细对比才发现,xilinx的例程中对位宽是做了判断的!当不是16位的时候,ddr3_model不一定是例化一个!比如32位的时候例程就例化了两个!

所以自己在例化的时候应该按照Vivado中的例程来学习例化,切不可照搬网上的例化!

850

850

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?