存储器校准调试

Vivado

中的存储器接口

IP

支持校准调试。其中存储有实用的核配置、校准和数据窗口信息

,

可在

Vivado

硬件管理器

中访问这些信息。“存储器校准调试

(Memory Calibration Debug)

”可随时用于读取此信息

,

并从存储器接口

IP

中获

取宝贵的统计数据和反馈。通过

Vivado

硬件管理器中的“

Memory Calibration Debug

”

GUI

或者通过可用的存储器校

准调试

Tcl

命令即可查看这些信息。

存储器校准调试

GUI

使用方法

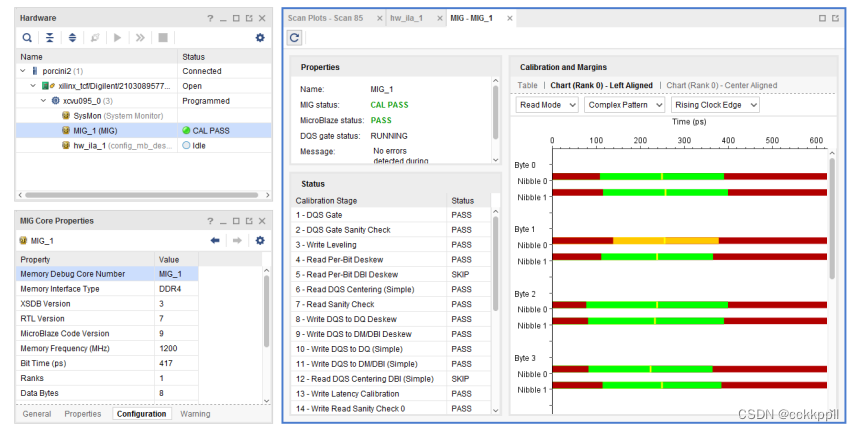

配置器件时

,

存储器接口会显示在

Vivado

硬件管理器中。

存储器校准内容显示在调试接口中

,

可用于快速识别校准状态和读写窗口裕度。此调试接口始终包含在生成的存储器接

口

(

UltraScale

和

UltraScale+

)

设计中。

存储器校准调试中的

Tcl

使用方法

连接到

Vivado

硬件管理器中的硬件时

,

在

Vivado Tcl

控制台中使用以下

Tcl

命令以输出

Vivado IDE

中显示的所有存储

器校准调试内容。

•

get_hw_migs

○

显示设计中存在的存储器接口。

•

refresh_hw_mig [lindex [get_hw_migs] 0]

○

仅刷新索引标明的存储器接口

(

索引从

0

开始

)

。

•

report_propery[lindex [get_hw_migs] 0]

○

报告可用于存储器接口的所有参数。

○

其中

,

0

是要报告的存储器接口的索引

(

索引从

0

开始

)

。

如需了解更多具体细节

,

请参阅以下文档中的

UltraScale

或

7

系列存储器校准调试命令

:

•

赛灵思答复记录

43879

:

7

系列

MIG DDR3/DDR2 -

硬件调试指南

.

• 《

UltraScale Architecture-Based FPGAs Memory IP LogiCORE IP

产品指南》

(

PG150

)

DDRMC

校准调试中的

GUI

使用方法

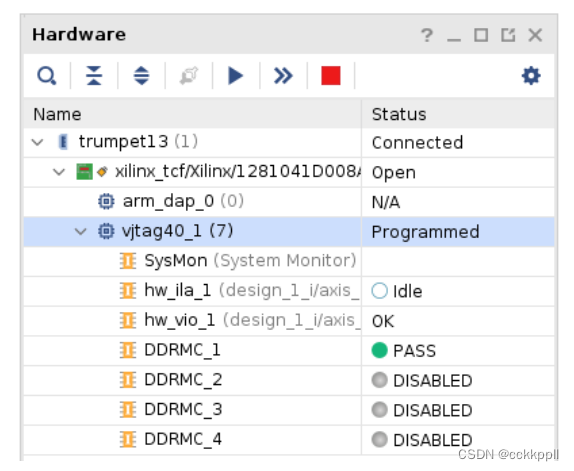

DDRMC

是

Versal

架构中包含的诸多集成块之一。配置

Versal

器件时

,

在

Vivado

硬件管理器中会同时显示已启用和已

禁用的存储器接口。

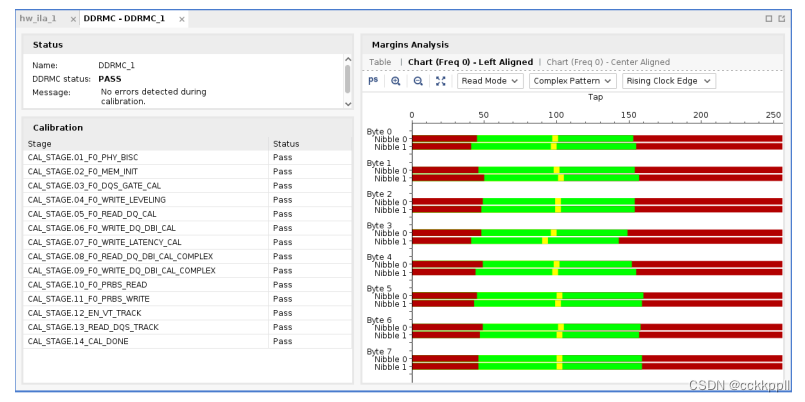

存储器校准内容显示在调试接口中

,

可用于快速识别校准状态和读写窗口裕度。在

DDRMC

集成块中始终启用此调试

接口。

DDRMC

校准调试中的

Tcl

使用方法

连接到

Vivado

硬件管理器中的硬件时

,

在

Vivado Tcl

控制台中使用以下

Tcl

命令以输出

Vivado IDE

中显示的

DDRMC

校准调试内容。

•

get_hw_ddrmcs

○

获取

Versal ACAP

集成的

DDRMC

软核列表。

•

refresh_hw_ddrmc [lindex [get_hw_ddrmcs] 0]

○

仅刷新索引标明的

DDRMC

(

索引从

0

开始

)

。

•

report_property [lindex [get_hw_ddrmcs] 0]

○

报告

DDRMC

可用的所有参数

,

其中

0

是要报告的

DDRMC

的索引

(

索引从

0

开始

)

。

在

Vivado

硬件管理器中调试

Dynamic Function

eXchange

设计

Vivado

®

硬件管理器支持对可部分重配置设计进行调试。为了成功对此类设计完成调试

,

需要先完成完整设计比特流编

程

,

然后才能对部分比特流进行编程以替换特定可重配置模块。

本文详细介绍了如何在Vivado工具中进行存储器校准调试,包括使用Vivado硬件管理器的MemoryCalibrationDebugGUI、Tcl命令以及针对UltraScale和DDRMC设计的特定调试方法。还提及了如何调试动态可交换设计的过程。

本文详细介绍了如何在Vivado工具中进行存储器校准调试,包括使用Vivado硬件管理器的MemoryCalibrationDebugGUI、Tcl命令以及针对UltraScale和DDRMC设计的特定调试方法。还提及了如何调试动态可交换设计的过程。

508

508

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?