0.引言

经过对疫情期间某天下午写的代码进行,多次调试后,终于输出了波形,下面我们逐步跟着思路,对22个寄存器不同长度的寄存器进行配置。另外,其实,我看晚上有别人写作AD9910的 verilog的代码,只有一个模块,并且让我觉得不知所云,只有3个寄存器的配置。代码风格可以说一片混乱,无法阅读,无法复用,感兴趣的可以去搜搜,我估计你搜到的也是那个版本。而我的代码风格一定是可以复用的,而且可以让初学者对verilog的写法有个全新的认识,掌握之后你可以任意时序的verilog,参考时序如图所示:

1、verilog思路

分为三个模块

对应的解释模块功能如下所示:

//module: AD9910_pro

//tips:以AD9910的串行模式,三线模式 3-wires 40MHZ的外部晶振倍频到1GHZ主频生成单频200MHz

//author: Lee Ruifeng

//程序设计思路:

//设计开始按键start脉冲,当脉冲为1时候开始配置。脉冲宽度高于FPGA一个系统时钟即可

//设计master_reset按键,先按下master_reset后,所有AD9910的寄存器均清零

//然后再按下启动start按钮,启动寄存器的数据写入

//总共写下23个通信周期,23个寄存器进行配置,FPGA晶振50MHz,三线模式,不用进行读操作

//module: 该模块控制的是控制数据sdio_sdo线的时序,在SCLK启动后的下降沿改变数据

// 同时,需要控制好并行数据的存储,启动后,存储第一个地址H00的寄存器值,之后如果收到sclk传输完毕的finish标志,收到

// 一个finish标志就开始计数,从而才知道寄存器对应的地址。更新寄存器值以及sdio通信周期的个数等

//module功能: sclk分频模块 ,用于控制SCLK时钟的时序,串行端口端口传输时钟速度,SCLK通信分为第一阶段的指令传输和第二阶段的数据传输

2、modelsim调试

1、首先,我们需要保证insruct_and_data在正确的变化。

下面查看验证了了地址的正确性

验证了数据的正确性传输后,我们需要确保地址为h17时候,sclk不启动。传输全部完成。

2、确保sclk、cs的正确性

sclk的准确,高电平两个时钟,低电平两个时钟。

此外,start_sclk正确,用于控制每一个通信周期的启动,最后一个通信周期完成后不启动。

经过测量:

parameter sclk_delay_start_time_I = 4,//用于控制第一阶段cs拉低后至sclk开始启动的那一段时间(指令传输) sclk先低后高 实际为5个时钟

parameter sclk_finish_delay_time_ID = 4,//用于控制第一阶段最后一个sclk后的那一段结束时间延迟(指令传输)和第二阶段开始的延迟 实际为4个时钟

parameter sclk_delay_finish_time_D = 4,//用于控制第二阶段sclk传输完成后的结束延时,结束后CS将拉高(数据传输) 实际为6个时钟

cs出现的高电平位置,均为一个周期的idle状态

在最后所有周期传输结束,可以看到传输全部结束,cs拉高

3、 下面确保sdio的正确性

其实在验证sdio的正确性时候,我们可以通过testbench里面来读数据,显示出来,或写到文本中。这个在以后补充。由于我明天要飞回北京,我这里暂时用最笨的方法,直接记录下数据,抽了部分,来验证。(if you want to get my verilog code to improve your coding skill,please add my QQ:1183699227,备注:ad9910 coding,30 rmb)

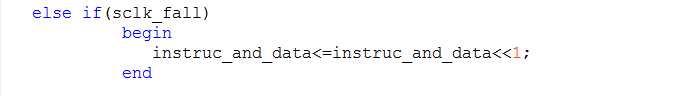

在检查sdio的正确性时候,我发现一件有趣的事情,当我的启动信号,设置时间比较长,假设一直为高电平,仿真我们按键,因为按键,按下的一瞬间,保持的时间其实是非常长的。此时,sclk都有,但是sdio却一直为低电平。但我当start时间只有1个时钟时候,是正常的,这是为什么呢,其实从,我们的程序中的这一部分可以看出端倪。在sdio_protocol_mod 模块中,如下图所示的代码,也就是说,else if里面的条件一直满足,然后每一个时钟,instruc_and_data一直保持着这个值。

注意看一下,下面代码,每次sclk的下降沿,instruct_and_data都会进行移位操作,但是如果一直保持start呢,及时到了sclk—fall也是赋值为原来寄存器的值,并没有进行移位操作。我们来看一下modelsim的图。

从如图可以看出,sdio始终为低电平,并且instruct_and_data 在一个sdio的周期结束后,才开始变,移位并没有发生。

所以我在顶层,增加了这一module,目的是将输入的start给寄存,输出一个高脉冲即可,这个高脉冲不能超过第一个sclk_fall的到来时间。

下面,再来看一下,增加了这一模块后的仿真。可以看到,这样在sclk的下降沿就能起作用了。

3、总结

如果在实际中,与功能仿真不符合,可以看看tb文件是否与真正的实际场景相符合,没准,代码有漏洞。

(if you want to get my verilog code to improve your coding skill,please add my QQ:1183699227 ps:ad9910 coding,50 rmb,知识无价)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?