背景

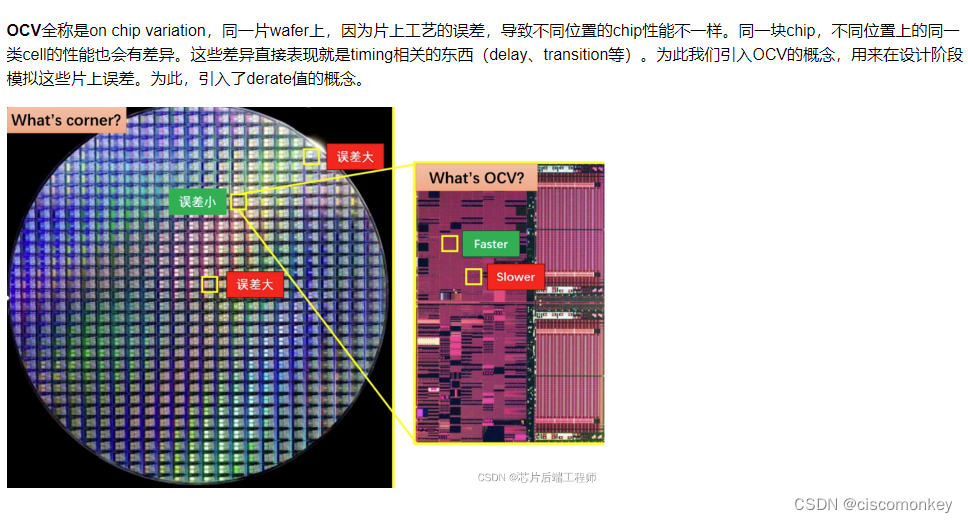

芯片制造过程中,MOS间差异必然存在。library中的cell delay是在某个固定的PVT(operating condition)下仿真得出的。而实际上在芯片内部由于工艺偏差、电压降、温度变化,cell的delay并不是一个固定值,而是一个随机值,遵循高斯分布或门特卡洛分布,在STA中用OCV来模拟这一特征。OCV全称on chip variation,用于描述不同管子间由于工艺偏差、电压降、温度变化引起的delay变化,也用于描述工艺偏差引起的net厚度宽度的变化从而导致net的RC变化。

————————————————

(on-chip variation) 是指在同一个芯片上,由于制造工艺和环境等原因导致芯片上各部分特征不能完全一样,从而造成偏差,对时序分析造成影响。这些偏差对互连线和cell的延时都是有影响的。 由于 OCV 对时钟和数据路径的影响可能不同,时序验证可以通过使发射和捕获路径的 PVT 条件略有不同来模拟 OCV 效应。 STA 可以通过 减免(derate) 特定路径的延迟来包含 OCV 效应,也就是说,通过使这些路径更快或更慢,然后使用这些变化来验证设计的行为。单元延迟或线延迟或两者都可以降额以模拟 OCV 的影响。

time derate(时序增减因子),在芯片生产过程中,由于刻蚀,不同点的温度,金属不均匀,串扰,晶体管沟道长度等影响因素,导致片上各个位置单元延迟不一样。因此我们需要一个缩放因子来让设计更加严格。

timing derate 是计算OCV的一种简单方法,在某单一条件(BC-WC)下,把指定path的delay放大或者缩小一些,这个比率就是derate。

best-case worse-case简称BC WC mode。

需要注意的是:考虑time derate需要在某个单一条件下,比如说BC或者WC条件下,把指定path的延迟再放大或者缩小一点,要么是BC,要么是WC,不要把BC和WC混在一起,再OCV,那样太过于悲观。

————————————————

例子

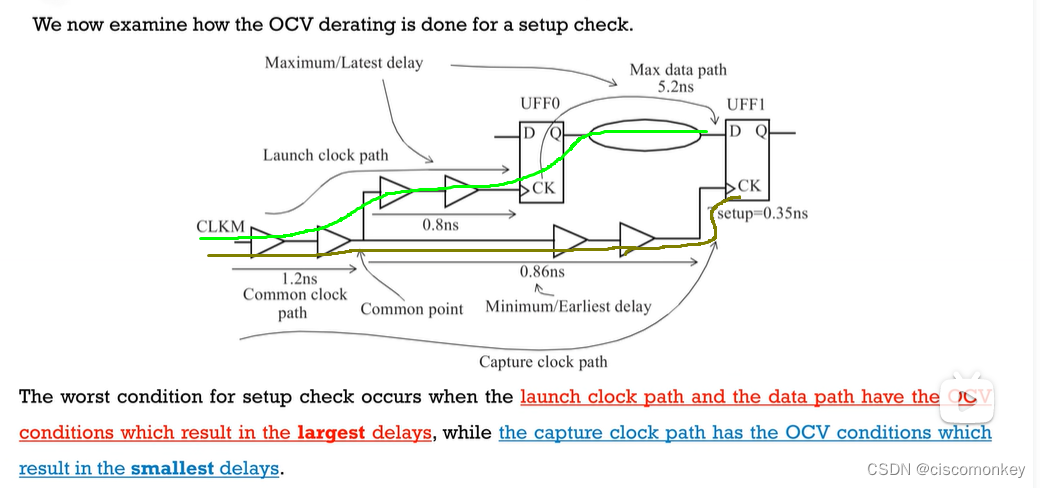

如上图所示,因为在芯片中,由于工艺制成,有可能绿色路径的buffer延时有一些不可控的变动因素,在棕色的路径中的延时也有一些不可控的变动因素,所以为了和实际吻合,我们在分析setup的时候,在同一个工艺库中,绿色的部分,用最大的延时,而在棕色部分,用最小的延时。这样对setup的check也是非常严苛的。

如何实现

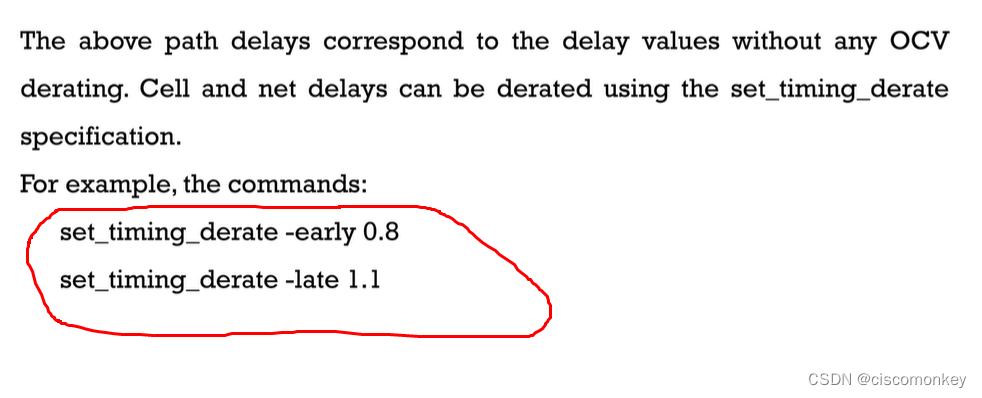

如上图所示,使用

set_timing_derate -early 0.8

set_timing_derate -late 1.1

也就是说,0.8代表缩小20%,late代表增加10%

什么是early?什么是late?

如何选取path?

对于setup Analysis:

- Launch clock : late path

- Data path : late path

- Capture clock : early path

因为launch clock+Data path 我们都希望为latest(越晚OCV越糟糕)

而capture clock越early越糟糕(越early OCV越糟糕)

对于hold Analysis:

- Launch clock : early path

- Data path : early path

- Capture clock : late path

————————————————

因为launch clock+data path 我们都希望越early(越早OCV越糟糕)

而capture clock 越latest越糟糕

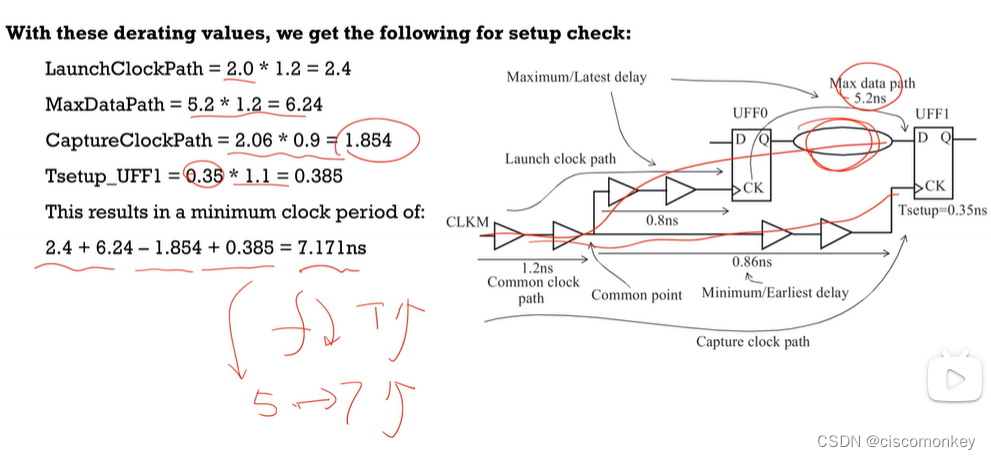

建立时间的OCV分析

derating因素可以应用到net delay上或者cell delay上

分别使用-cell_delay和-net_delay

另外-cell_check 指的是检查Tseup的时间(library setup的时间需要放大1.1倍)

set_timing_derate -cell_delay -early 0.9

set_timing_derate -cell_delay -late 1.2

set_timing_derate -late 1.1 -cell_check

如下图所示:

setup check一般工作在WC PVT条件下,因此不需要在late path 上,即lauch clock path以及data path上再加time derate, 因为在WC条件下,launch clock path 以及data path上的延迟已经是所有条件下最差的delay了,没有必要再加大延迟,但是WC条件下capture clock path 上的delay肯定不是最小的,因此需要加快。

所以上面的timing path做setup check,time derate只需要这样设置

set_timing_derate -early 0.9

set_timing_derate -late 1.0

————————————————

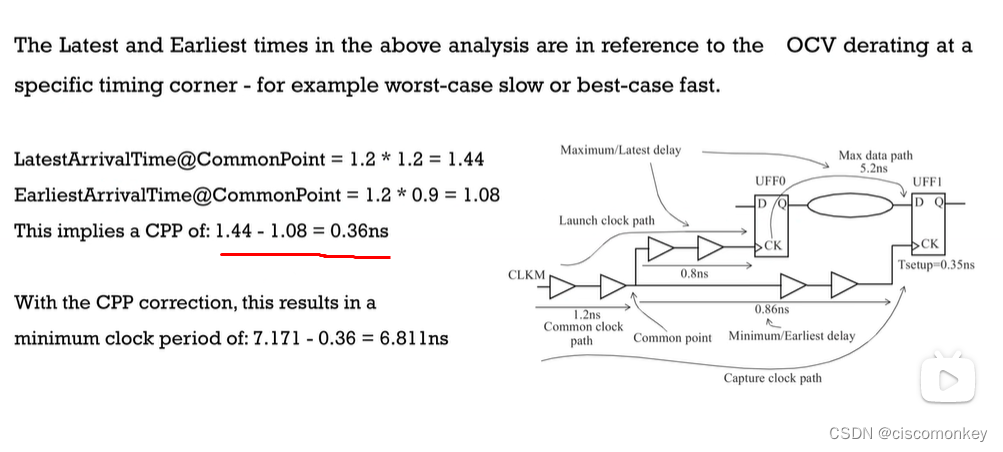

此外:

对于公共路径进行同时放大和缩小,这是不符合常理的。

为了让芯片不过于悲观,叫做CPP,common path pessimism,我们应该移除掉这种悲观。

如上图所示,为了不过于悲观,从上图可以看到,我们有0.36ns是多算进去的。

所以我们需要减去0.36ns,因此最小的周期可以到达6.811ns。

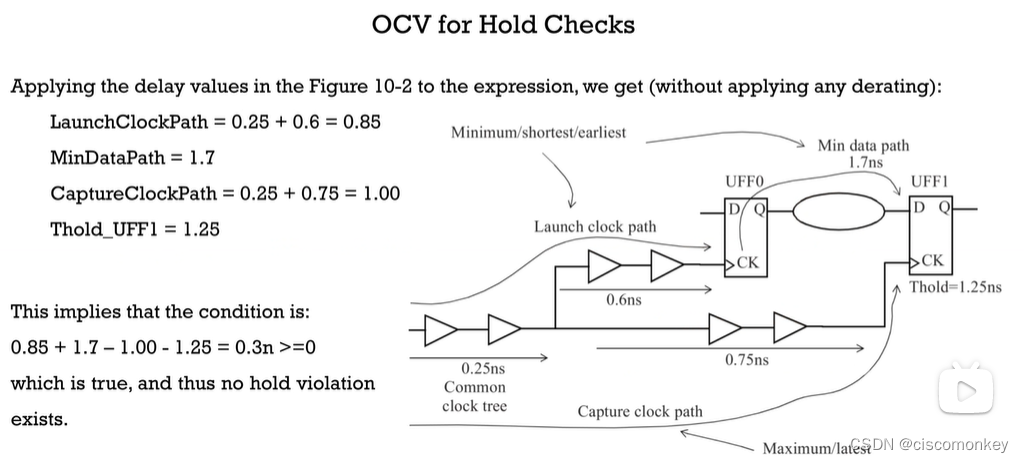

OCV for hold check

数据到达时间 即data path和launch clock path需要使用-early 选项,使得路径变快

数据要求时间 即capture clock path需要使用 -late选项,使得路径变慢

实际上Hold check一般在BC条件下,因此,launch clock path与data path不需要再进一步减小delay,因为已经是最小delay,但是BC条件下的capture clock path需要derate,可以使用如下设置

set_timing_derate -early 1.0

set_timing_derate -late 1.2

Launch clock path = 0.85 * 1.0 = 0.85

Min data path = 1.7 * 1.0 = 1.7

Capture clock path = 1.0 * 1.2 = 1.2

slack=0.85+1.7-1.2-1.25=0.1

参考文章

参考了以下文章

参考文章1

OCV/AOCV/SOCV介绍

CPPR详解

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?