0.ATPG

ATPG是一种自动化的测试模式生成技术,用于生成能够检测芯片中各种故障的测试向量。这些故障包括卡住故障(stuck-at faults)、转换故障(transition faults)、路径延迟故障(path delay faults)等。ATPG工具根据芯片的逻辑设计和故障模型,自动生成测试向量,以覆盖尽可能多的潜在故障。

ATPG是生成SCAN的测试pattern的一种技术

所以有时候说ATPG测试是不准确的,对应的是SCAN测试

1.scan结构图

扫描路径法的显著优点就是测试中把时序电路转化为组合电路,使得测试生成比时序电路容易,而且处于扫描路径上的触发器的状态是“透明的”:可以串行地移入所需要设置的状态,也可以把电路状态串行地移出去。

一般说来,基于扫描路径设计的电路,只要对组合电路部分和不在扫描路径上的触发器进行测试生成,而处于扫描路径上的触发器的测试方法和测试图形是固定形式的,就并不需要测试生成。

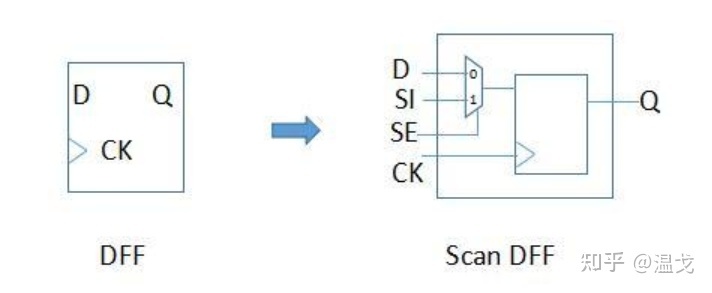

对于scan设计,需要使用专门的scanDFF,相比于普通的DFF,scan DFF多了三个端口:

扫描使能(Scan Enable, SE);

扫描输入(Scan In, SI);

扫描输出(Scan Out, SO)

但是一般情况下SO和Q复用一个pin,其结构如下图:

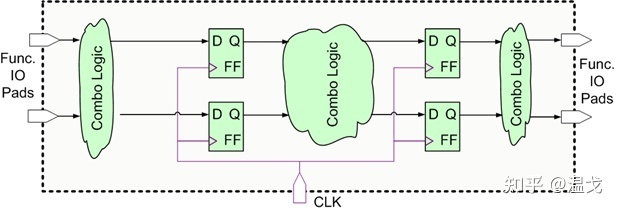

scan设计的结构如下图所示,将scan DFF的Q端和SI端连接,多个scan DFF就组成了一个scan chain。在实际的芯片设计中,将普通DFF替换成scan DFF并串成scan chain这两步操作都是由工具自动完成。

上图是没加组合逻辑的图。

下图给出带组合逻辑无scan功能之前的示意图:

下图是

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2129

2129

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?