目录

1. launch和capture的概念

launch和capture一定是对两个寄存器而言的,当前寄存器reg_cur,前一级寄存器reg_bf。对于reg_cur它的launch就是reg_bf的capture,这个概念在scan和sta中都是一样的。

以同步电路为例:

reg_bf 在@posedge clk_0 时刻D端capture bit ‘1’ 那么同一时钟沿经过之后launch bit ‘1’,(假设中间没有其他组合逻辑和线延时) next clk posedge reg_cur capture bit ‘1’

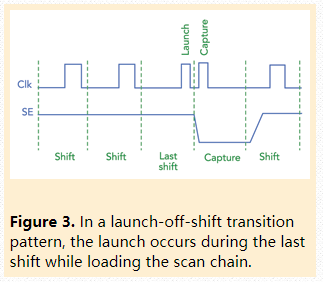

launch-off-shift & launch-from-capture

参考https://www.edn.com/launch-off-shift-at-speed-test/

a. launch-off-shift

Lunch off shift (LOS):

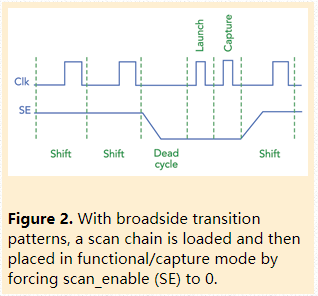

b. launch-from-capture

又被称为broadside pattern或Lunch off capture (LOC)

c .两者的区别

LOS和LOC的区别在launch的过程中scan_en的值不同,LOC在launch时scan_en=0,而LOS在launch时scan_en=1。

对capture的影响在于LOC情况下前一级flip-flop launch值要经过combination logic,所以ATPG需要计算测试向量经过combination logic的值,才能与capture的值比对。

因为在scan_enable=1时,寄存器的输出Q是直接连接下一级的SI,中间没有其他组合逻辑

参考文献 https://www.edn.com/launch-off-shift-at-speed-test/ 详细给出两者的区别和使用情况

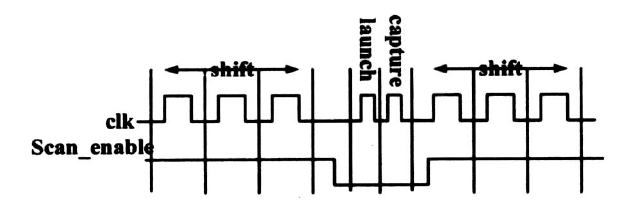

2.scan 过程

用一句话总结就是:在scan的shift mode(scan_enable=1)下,测试机台将test pattern load到寄存器chain上(slow clk),然后在fast clk下进行launch和capture(AC测试)或在ate_clk(slowClk)下进行launch和capture(DC测试)。最后在shift mode将寄存器上的状态值移除供观察和比对

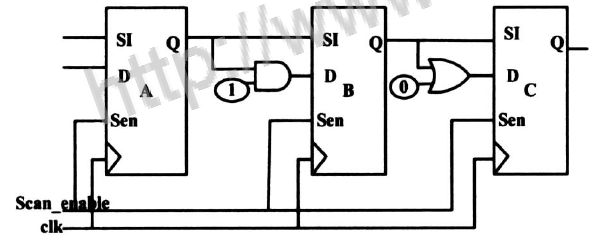

图1 SCAN测试原理

a.scan shift

在shift阶段( scan_enable = 1或者叫shift_enable)使用测试机提供的慢速时钟,A和B分别装载0和1。这个过程就是测试机将测试向量‘01’shift到对应的flip-flop。

scan_enable为1时:寄存器的输出Q是直接连接下一级的SI,中间没有其他组合逻辑

b.launch

首先set scan_enable = 0,这时发一个功能时钟( launch时钟) , B会在D端捕获0,一个1 - to - 0的翻转会传递到C。(为了简单认为两寄存器之间没有组合逻辑)

c.capture

保持scan_enable = 0,在第二个功能时钟脉冲( cap ture时钟) C会捕获这个变化。如果在第二个时钟C捕获到了0,意味着在一个周期内完成了所需的翻转。

图2 at-speed测试clk波形

图2中Clk信号在shift和launch、captuer阶段的切换,以及launch、capture 2个功能脉冲的产生需要有专门的电路支持。这要用到OCC电路。OCC电路参考如下:

https://blog.csdn.net/cy413026/article/details/84302717

https://blog.csdn.net/cy413026/article/details/84302717

830

830

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?