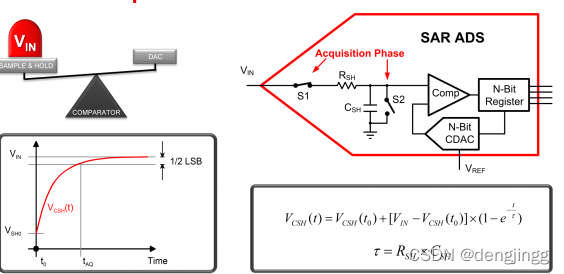

采样阶段由Vin对Csh电容进行充电,充电曲线左图所示。

电容电压的计算公式,和实际常数

充电阶段是RC充电,直到 1/2 LSB才认为充电完成。否则对ADC的精度是一种相对让费。

采样实际在ADC数据手册中会有说明

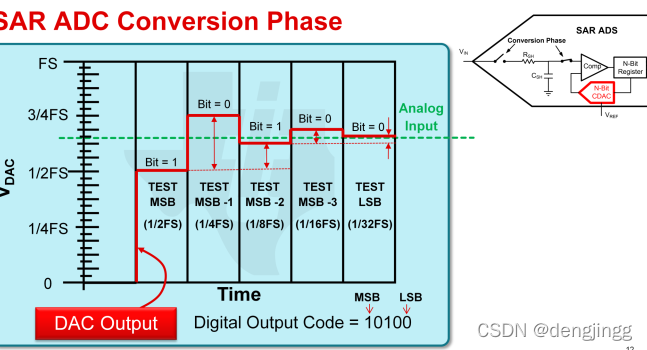

SAR ADC的实际转换过程,类似于天平称重。

FS值得是满量程。天平放砝码的一端不能重过被测物体。

使用1/2FS,1/4FS .1/8 FS依次比较。小于模拟输入记1 ,大于记 0这样结果无线接近模拟输入

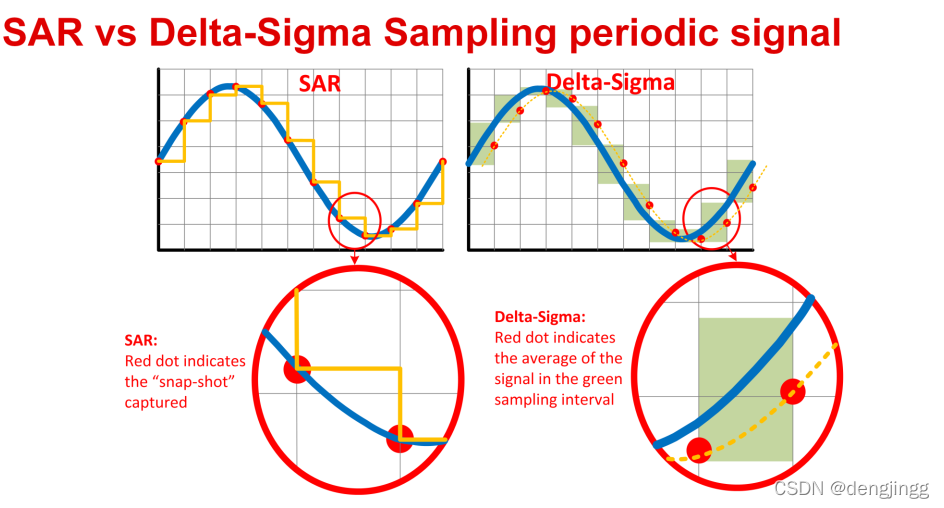

SAR ADC 使用了类似快照的机制,模拟输入的电压被复制到内部保持电容上。近似的采样为一个点

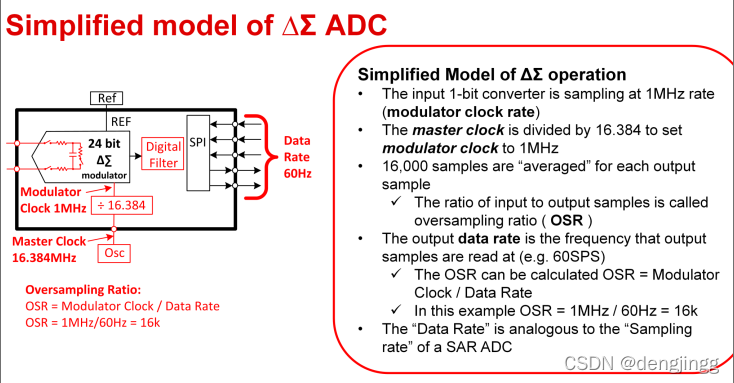

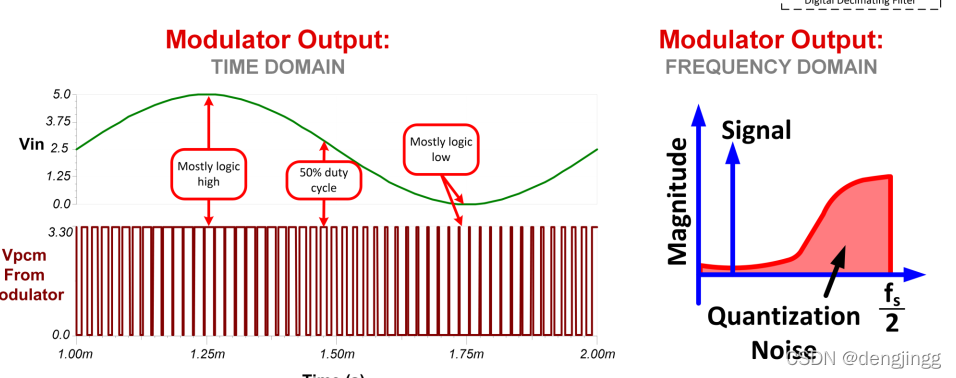

Delta Sigma ADC 简单的理解为采样段的平均值。

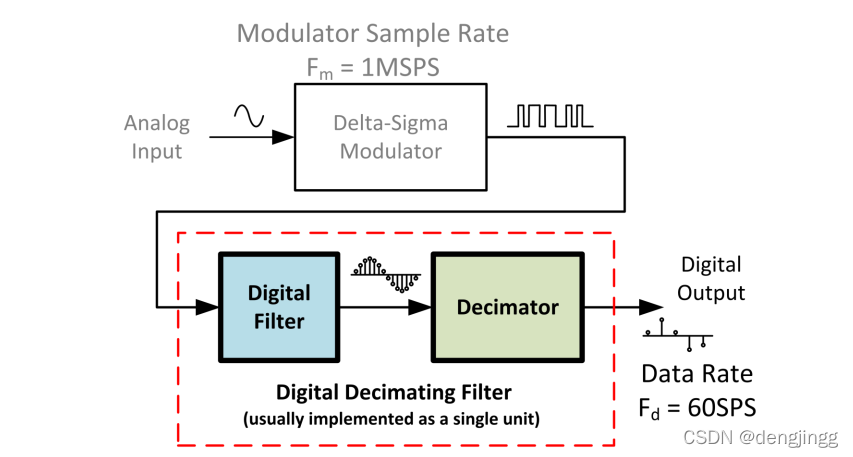

delta-sigma 的输入是调制器,它的采样速率远远比采样值输出的速率快。例如也就是说调制器的时钟为1Mhz,输出结果60Hz。所以一秒钟的过采样为 1M/60 =16000hz OSR。

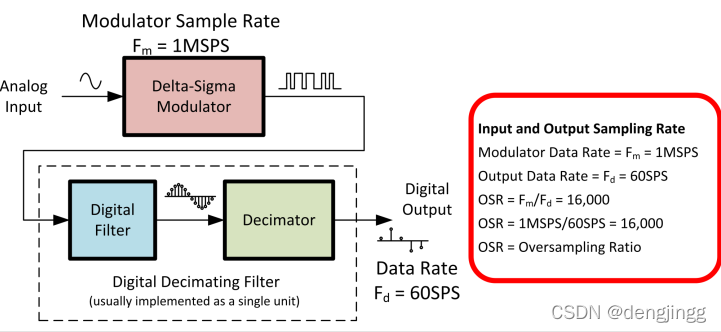

模拟模拟输入信号,结果调制器(1MSPS)后会产生1MSPS的输出信号到数字滤波器。数字滤波器每秒输出60个结果。

所以每1M/60 =16000 个采样才会输出一个转换结果。过大的过采样率表明对信号进行了大量的平均处理。过采样可以降低噪声,提高输出分辨率。

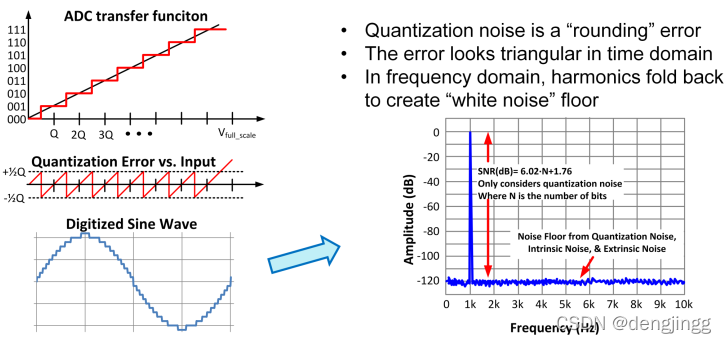

量化噪声,由量化下的分辨率产生。

一个理想的正弦波是平滑的,量化后的曲线是带锯齿状的。带有谐波成分,主要由量化产生。

其他部分是完全理想的状态下为SNR=6.02*N+1.76。

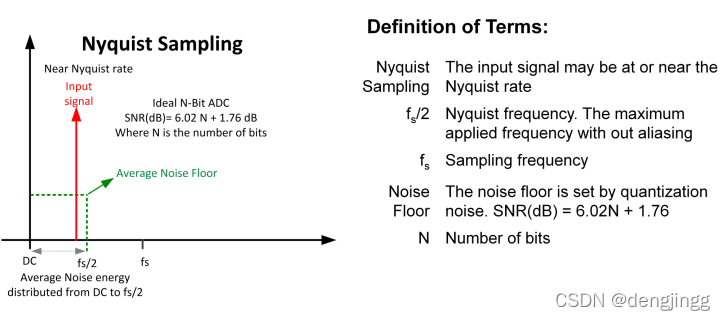

当对一个离散区间的信号进行采样时,奈奎斯特-香农采样定理指出,为了从采样后的信号重构出原始信号,采样频率(Fs)必须大于输入信号最高频率分量的两倍。我们可用的频率范围是从dc到采样频率除以2,即奈奎斯特频率。

对于具有n位分辨率的ADC,量化噪声均匀分布在DC和ADC之间的采样带宽上

奈奎斯特频率。理想ADC的信噪比(SNR)由公式SNR(以分贝表示)=给出6.02*N+1.76,其中N为位数

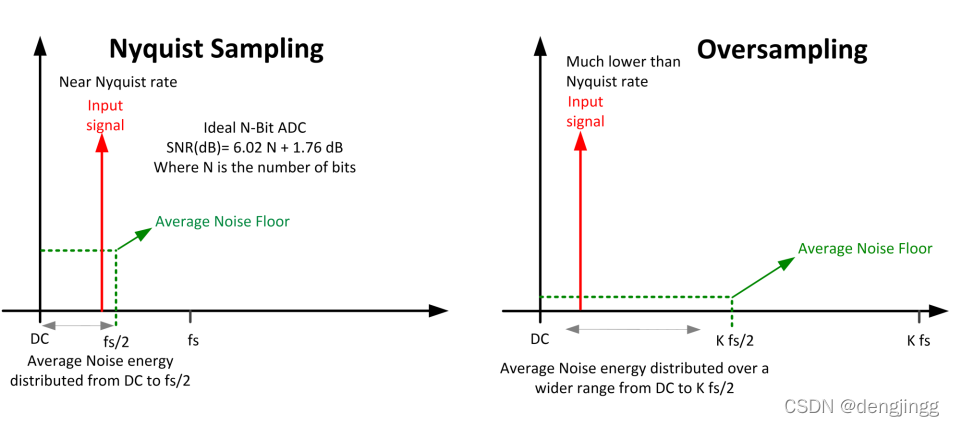

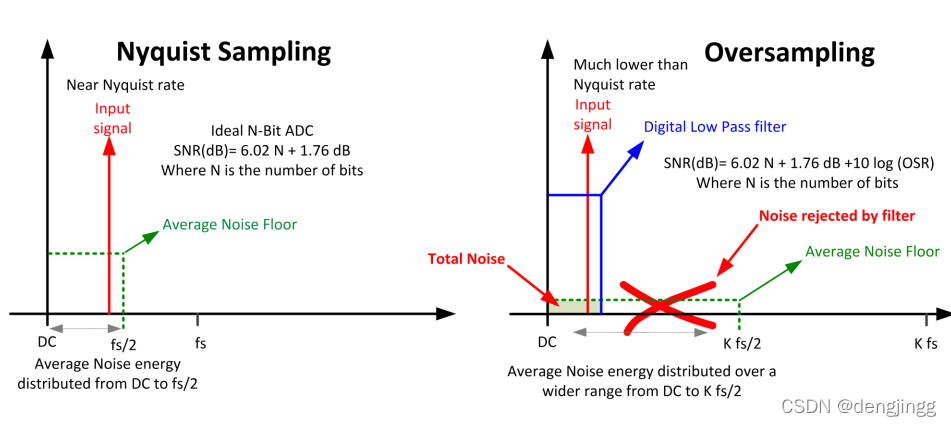

右图所示,当采样频率变快K倍,也就是过采样。频率值为 K* Fs/2

噪声功率的总量保持不变,但噪声已经扩散到更宽的频率范围,并且FFT中每个频率箱中的噪声水平已经降低。

这个时候使用低通,那么就可以提高SNR,为6.02*N +1.76+10logOSR OSR为过采样频率

原理是过采样使得噪声分布更宽,但是噪声的总功率不变,所以在原来区间内的噪声功率变小,所以提高了信噪比。

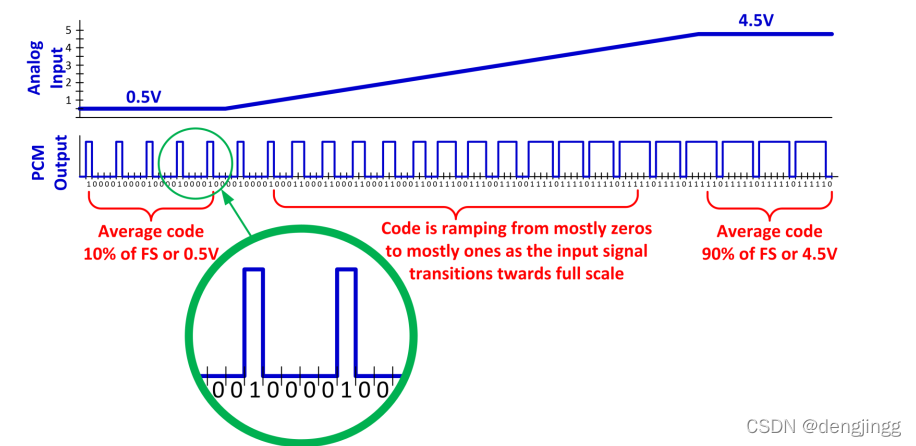

蓝色圆圈内部所示,0.5V恒定压下,会输出采样PCM编码。0.5V是FS的10%所以得到如图所示的尖脉冲。

当电压升高后PCM的脉宽在一定程度上变宽或者说编码中1的个数变多。

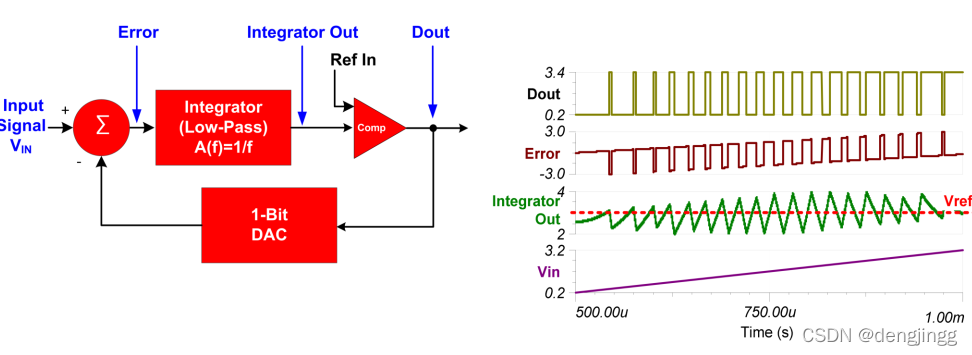

显示了调制器内部的框图。这是一个控制系统样式图。这个控制回路的目标是保持模拟输入和数字输出之间的误差尽可能小。

为了比较模拟输入和数字输出,输出用1位数模转换器转换后返回到输入端。这显示在反馈回路和输入误差求和。当积分器的输出变大时,比较器会将数字输出切换到逻辑输出 也就是和参看Ref in作比较。当比Ref In大时,输出负,这一操作将导致误差变为负的,积分器将向相反的方向倾斜。这个时候输入信号和返回信号的和会是负数那么积分其输减小。下一个采样时刻,积分器的输入(Vin+Dout)会继续增加。

ERROR 就会出现右图所示的情况。(Vin+Dout)当Vin越来越大的时候,需要更多周期的Dout才能把ERROR拉为负数。所以ERROR会变宽。

越来越难了!写的可能不对,是我的理解。

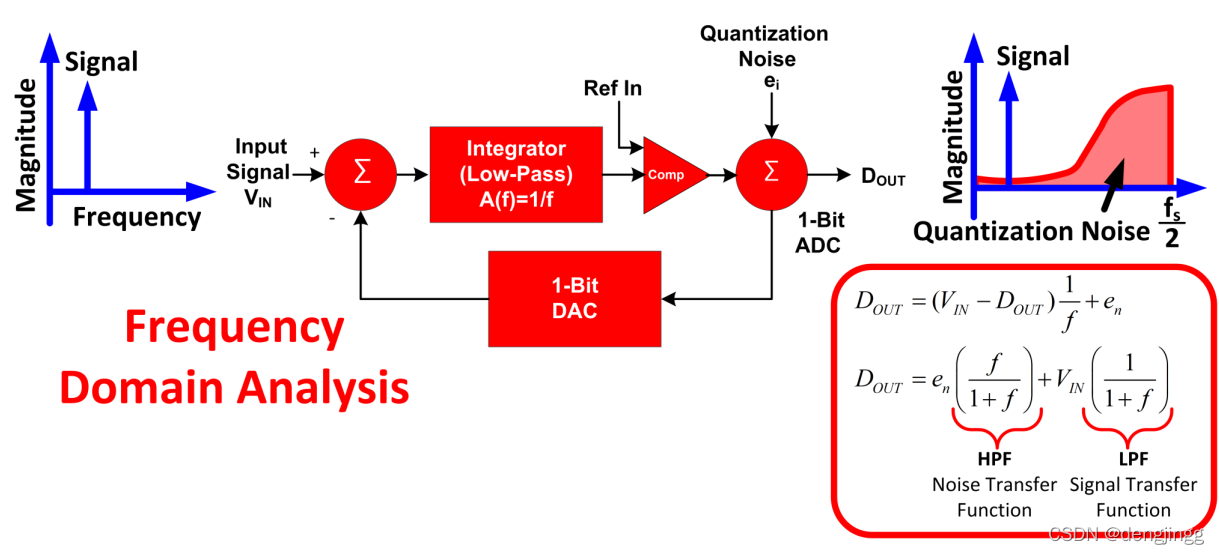

框图显示了输入信号和噪声在频域的传递函数。分析传递函数,可以看到输出被反馈并从输入信号中减去。假设1位DAC本质上是1的增益。因此,求和块的输出是Vin - Dout。然后乘以积分器,其增益为1/f。最后,在输出求和块中加入量化噪声项。这就是我们得到的第一个方程,Dout = (Vin - Dout)*1/f +e_n。

求解后得到第二个方程。 分为高通部分和低通部分。en噪声是高通因子。Vin 是低通因子。

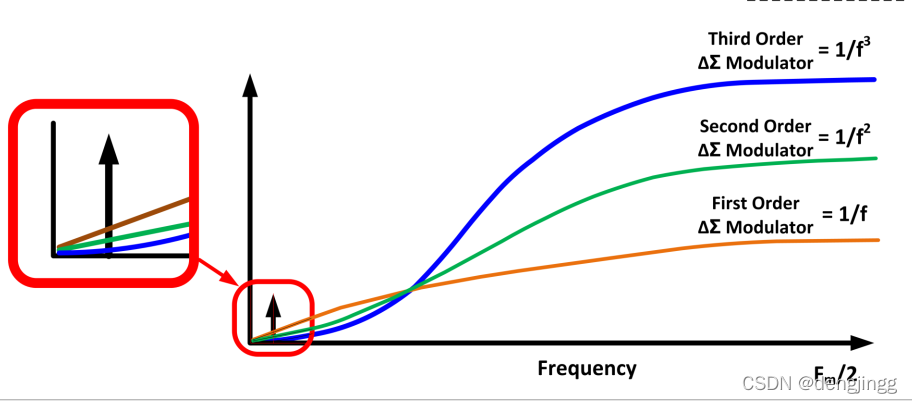

显然频率越高噪声越大。噪声大部分都被集中到了高频上,因为噪声功率不变。

时域图

数字Filter 消除高频部分的噪声。然后在重建信号输出。

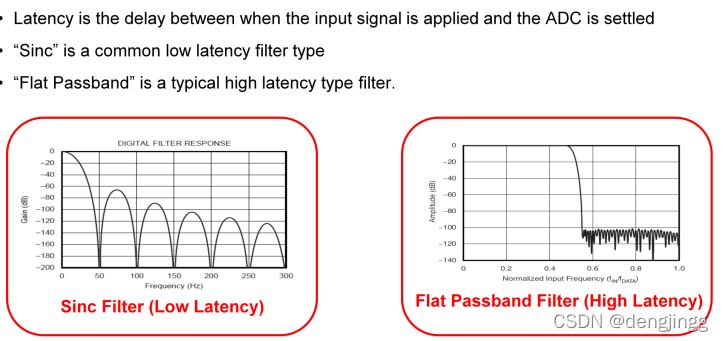

这里讨论数字滤波器并不是要称为数字滤波器的专家。从特定的维度分析SAR ADC 和Delta-Sigma ADC的共同和他们各自的特点

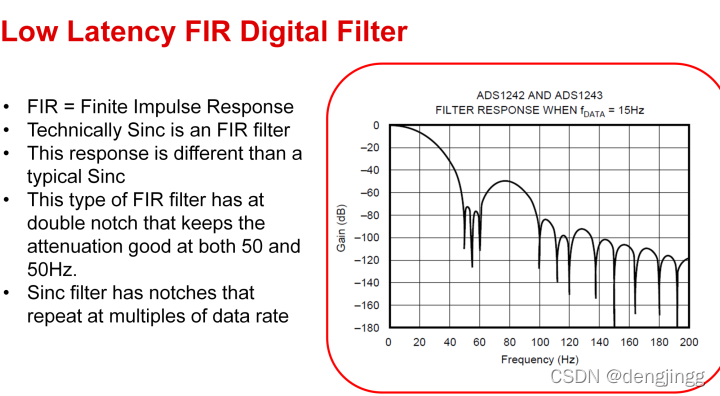

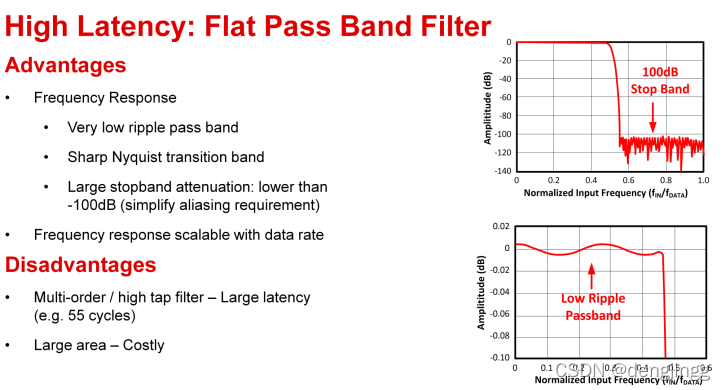

上图是两种低通滤波器,Sinc 滤波器的相应和高延时Flat Passband Filter

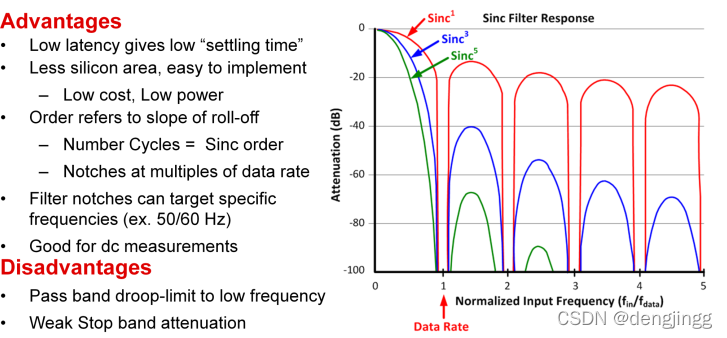

Sinc 滤波器的特点是有着低延时。

相应曲线并不是很好,有着特别的应用场合。红色的Sinc在1~2上甚至只能衰减20db。

Sinc 滤波器 也是 FIR滤波器。

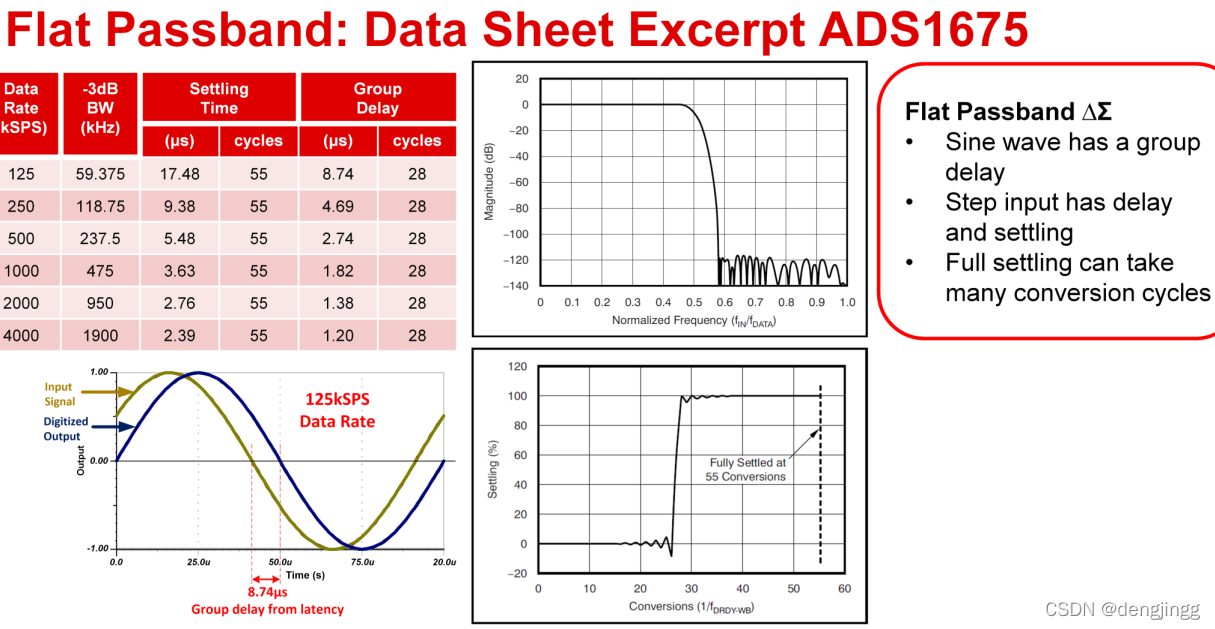

FPB滤波器在截至频率处有很好的抑制作用-100db,并且很陡峭。

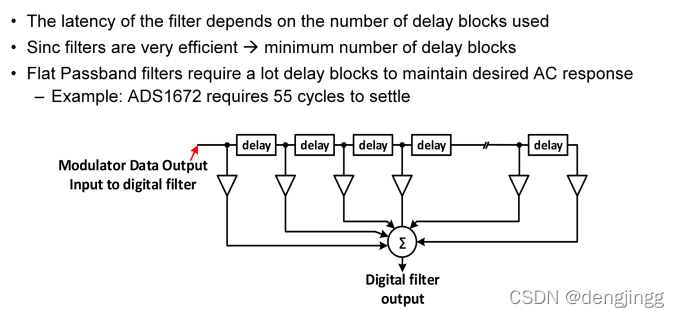

但是这样滤波器的实现需要很多延时,ADS1672为例需要delay 55 cycles。成本也比较高。

这里的延时不是值采样的电容充电,而是值内部滤波器需要的延时。

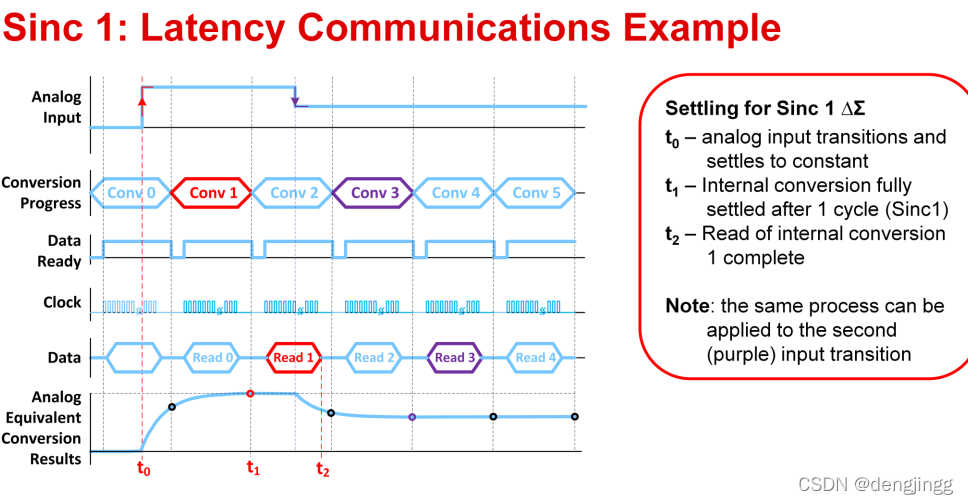

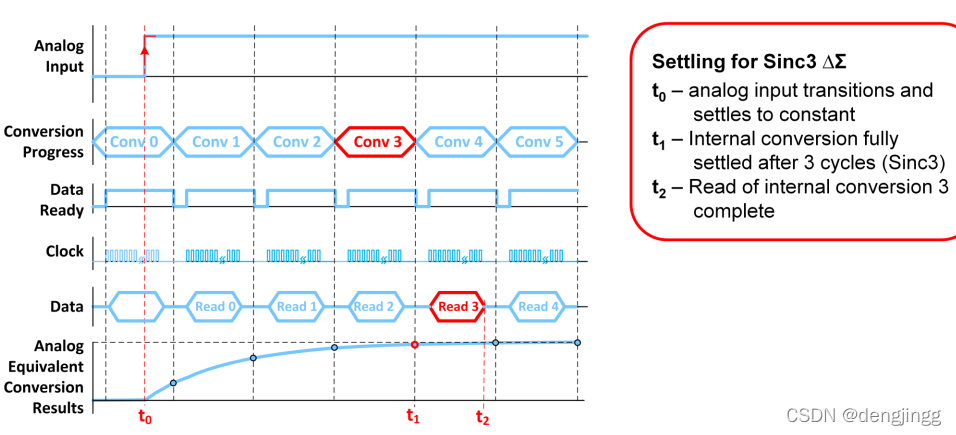

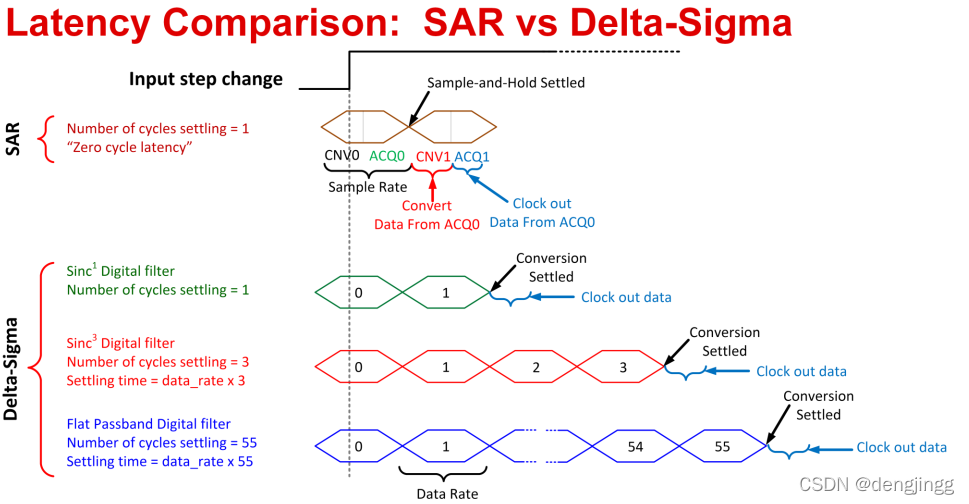

Conv_0值得是一个转换周期,可以理解为一端固定的时间间隔。

Sinc1 需要一个完整的转换周期,数据需要Read周期才能读取完毕。

Sinc3 需要3个转换周期,在T2时刻MCU 才能读取数据。

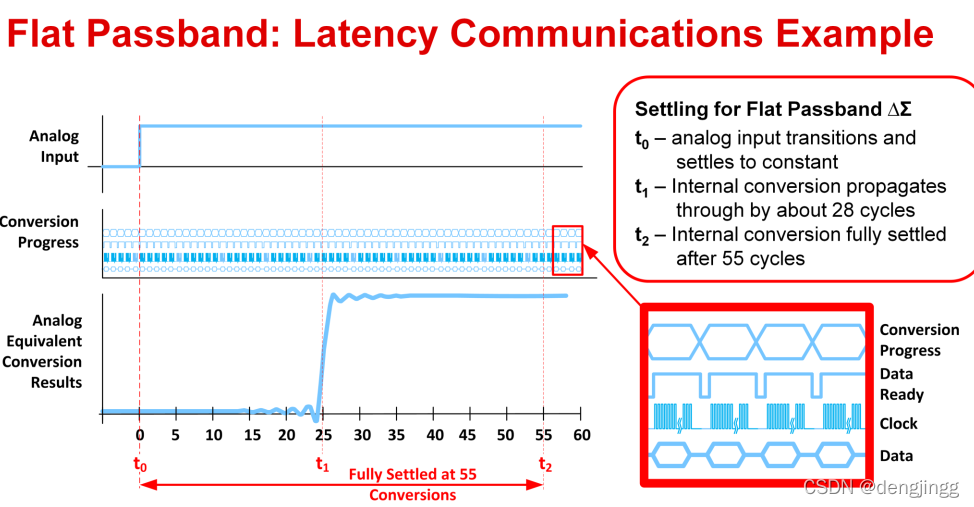

T0~T2需要55个转换周期。

频率响应曲线显示在大约1 / 2的数据速率下,从通带到阻带有一个非常尖锐的转变。另外,注意阻带中的衰减相当好;在本例中低于120dB。该表显示了该设备的-3dB带宽、设置时间和组延迟。再次注意,-3dB点大约是数据速率的一半。setting时间与滤波器的设计有关,其他转换器的setting时间可能不同。阶跃响应表明,完全沉降需要55个周期。前27个周期基本上没有变化,大约在55个周期后才能完全稳定下来。

最后,群体延迟大约是稳定时间的一半。群延迟是应用正弦输入和等效数字化输出之间的时间偏移

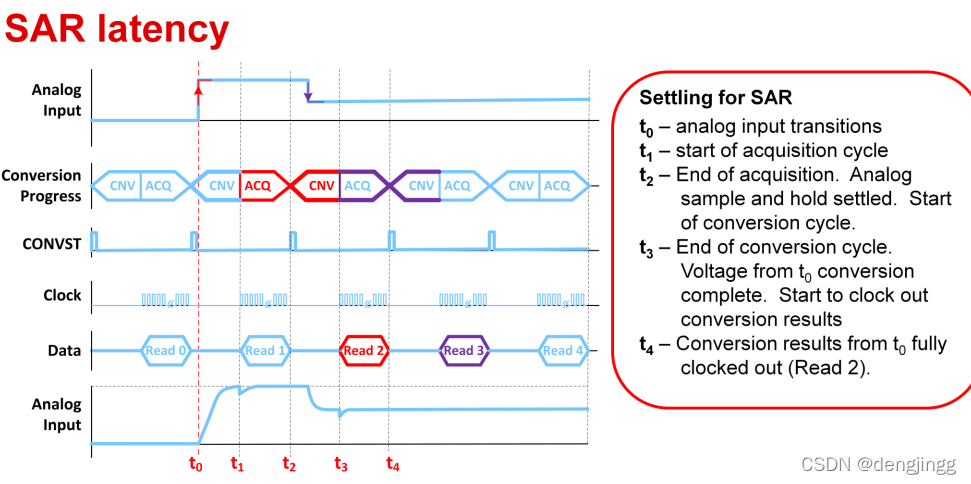

SAR ADC的延时非常短。

to模拟输入开始变化

t1 采样阶段开始

t2 采样保持阶段结束,开始转换

t3 转换完成。

t4 转换数据读出

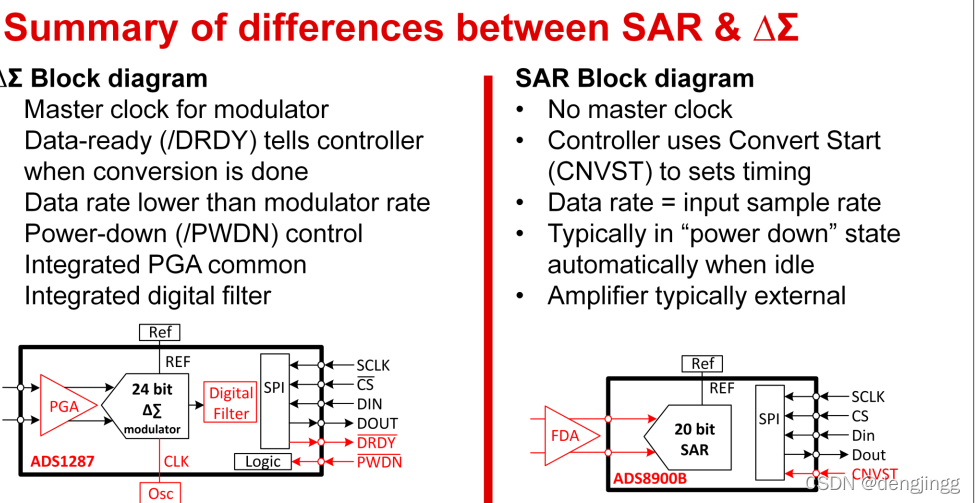

delta-sigma可以有一个内部PGA, SAR通常有一个外部差分放大器。并非总是如此,但是PGA集成到delta-sigma转换器中比SAR集成要常见得多。注意到delta-sigma有一个主时钟输入。这个时钟用来运行调制器。在许多情况下,内部时钟分频器将用于主时钟信号。对于一些delta-sigma转换器,这个时钟源是内部的。同时,SAR没有主时钟输入。一些SAR转换器将有一个集成振荡器,用于在转换周期中定时,但SAR通常不需要外部振荡器。所有的delta-sigma转换器都有一个集成的数字滤波器,但SAR转换器很少提供这个功能。SAR ADC在不转换时通常消耗很少的能量,所以它们通常不需要断电控制。另一方面,delta-sigma转换器通常连续转换,因此,当不需要转换时,通常使用掉电控制将设备置于空闲状态,以最小化功耗。最后,delta-sigma ADC有一个数据就绪的中断引脚,告诉微控制器何时转换完成。通常微控制器将使用中断或轮询方法来知道何时可以读取数据。另一方面,SAR转换器由使用转换启动引脚的微控制器显式控制。。

本文深入解析了SARADC和Delta-Sigma ADC的工作原理,包括采样过程、RC充电特性、量化噪声、奈奎斯特采样定理,以及两种ADC在低通滤波器、过采样效果和功耗方面的区别。重点讨论了SARADC的快速响应、Delta-Sigma ADC的连续转换和内部组件,如PGA和数字滤波器。

本文深入解析了SARADC和Delta-Sigma ADC的工作原理,包括采样过程、RC充电特性、量化噪声、奈奎斯特采样定理,以及两种ADC在低通滤波器、过采样效果和功耗方面的区别。重点讨论了SARADC的快速响应、Delta-Sigma ADC的连续转换和内部组件,如PGA和数字滤波器。

1409

1409

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?