名称:两种不同方式分频器设计Verilog代码ISE仿真(文末获取)

软件:ISE

语言:Verilog

代码功能:

两种不同方式分频器设计

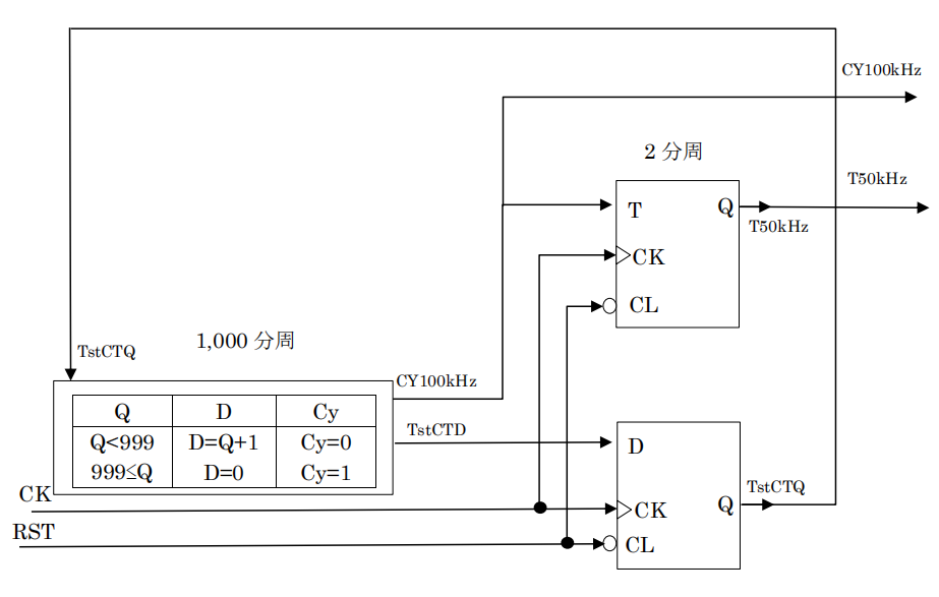

1. 输入为100MHz,要求输出为50kHz

需要将上述程序在不改变回路图的情况下用两种方式改写

换一种语法来写一个

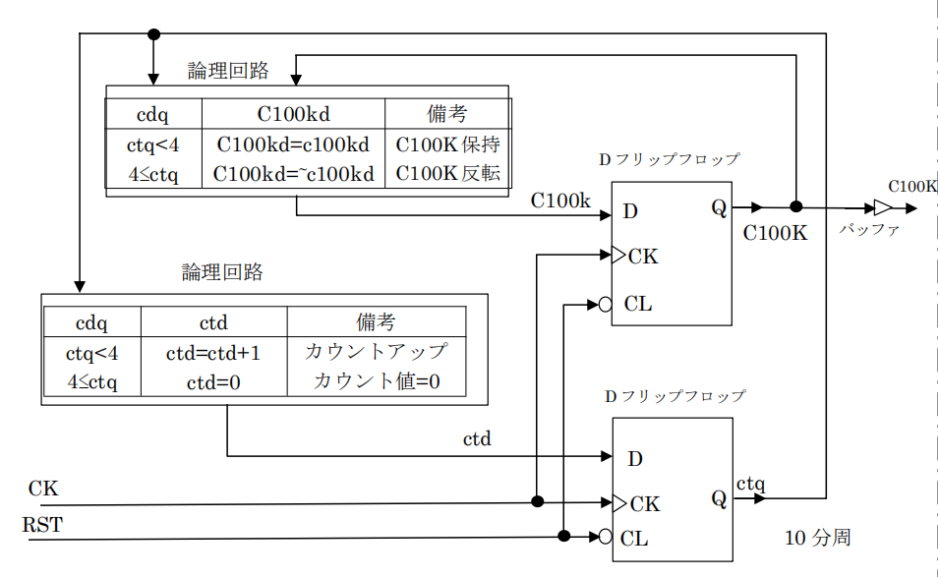

然后是输入1MHz输出100kHz 用10分周而不是上面的5×2的形式

1. 输入为100MHz,要求输出为50kHz

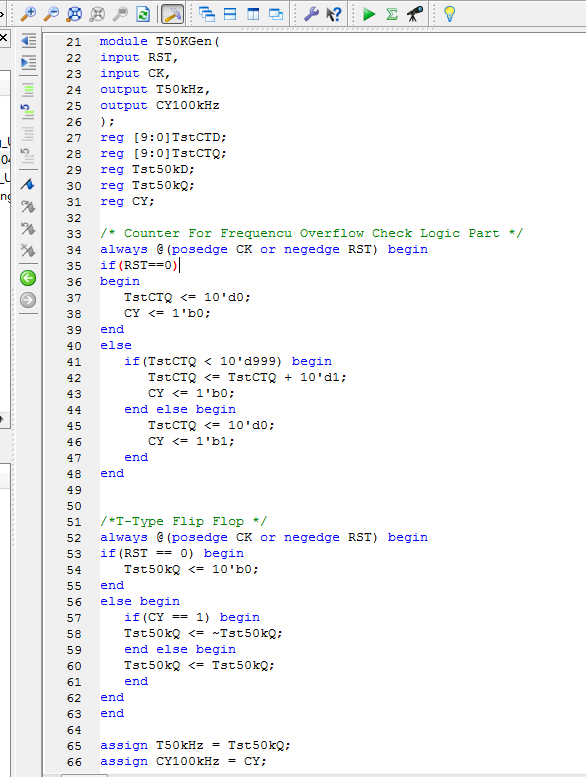

写法1代码

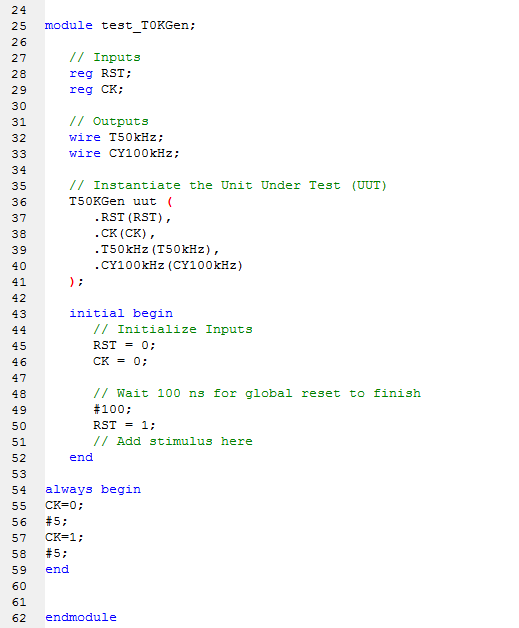

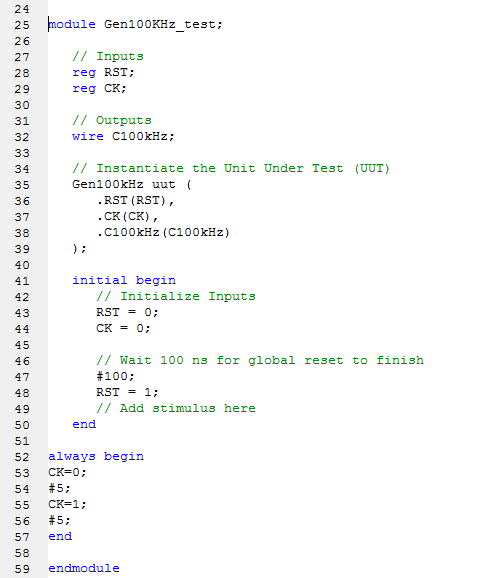

Testbench

仿真图

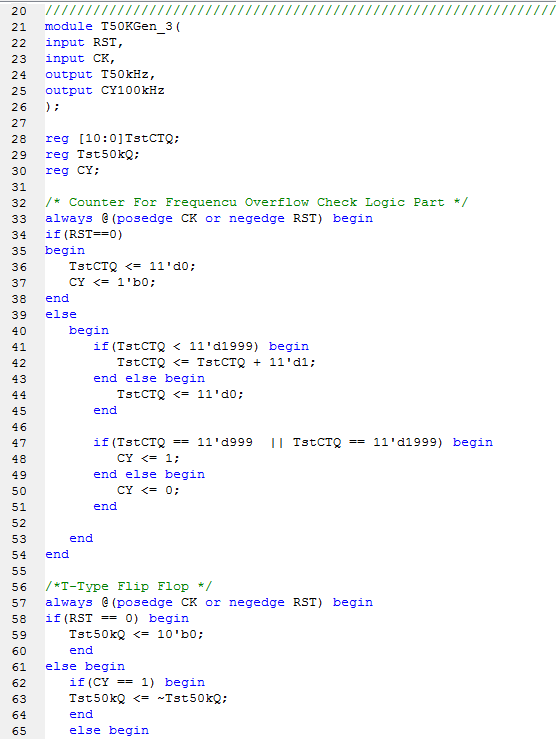

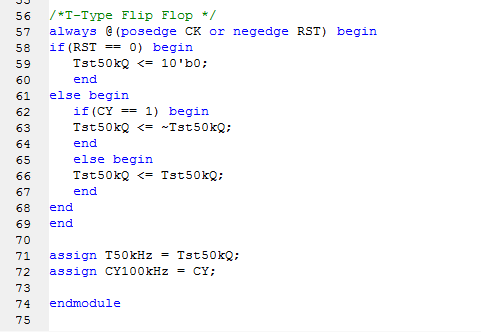

写法2代码

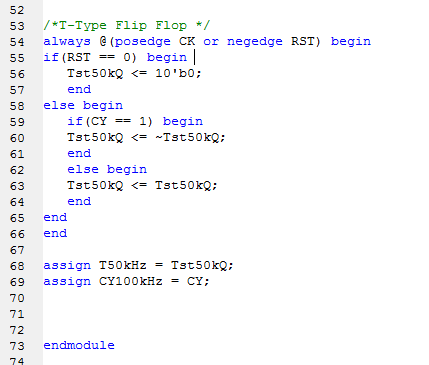

写法3代码

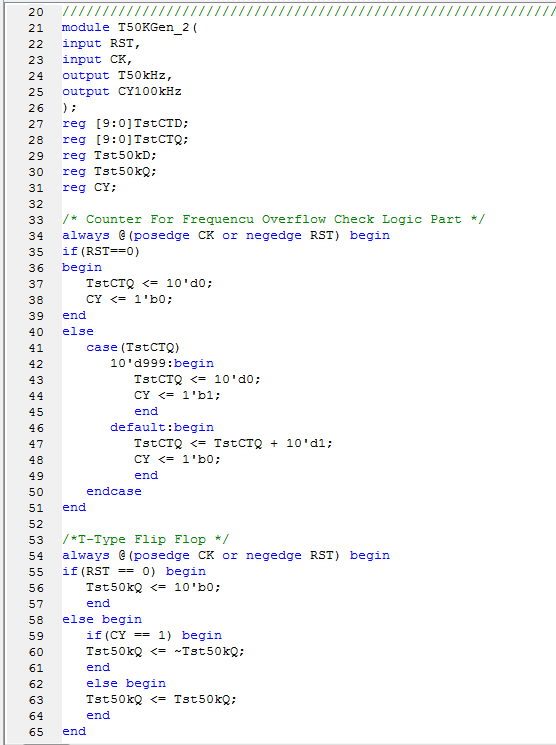

2. 输入1MHz输出100kHz 用10分周

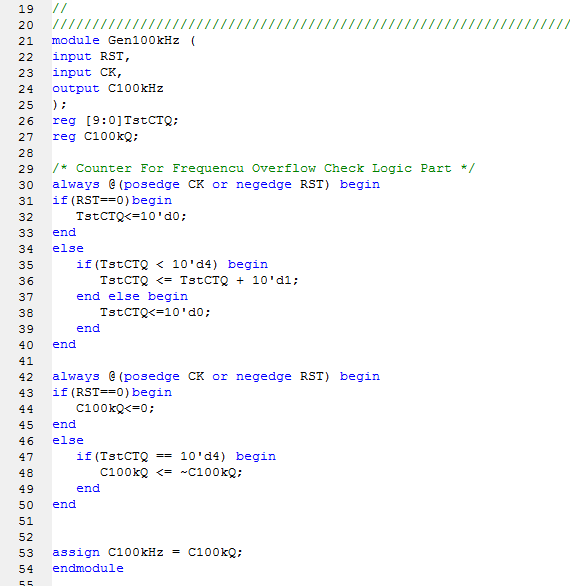

代码

Testbech

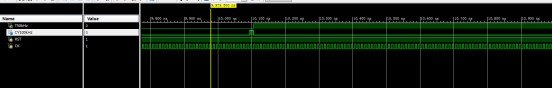

仿真图

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 22:38:13 07/16/2020 // Design Name: // Module Name: Gen100KHz // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module Gen100kHz ( input RST, input CK, output C100kHz ); reg [9:0]TstCTQ; reg C100kQ; /* Counter For Frequencu Overflow Check Logic Part */ always @(posedge CK or negedge RST) begin if(RST==0)begin TstCTQ<=10'd0; end else if(TstCTQ < 10'd4) begin TstCTQ <= TstCTQ + 10'd1; end else begin TstCTQ<=10'd0; end end

源代码

点击下方的公众号卡片获取

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?