名称:直接测频法6位频率计设计Verilog代码ISE AX309开发板(文末获取)

软件:ISE

语言:Verilog

代码功能:

直接测频法6位频率计

1、使用直接测频法

2、频率显示在6位数码管

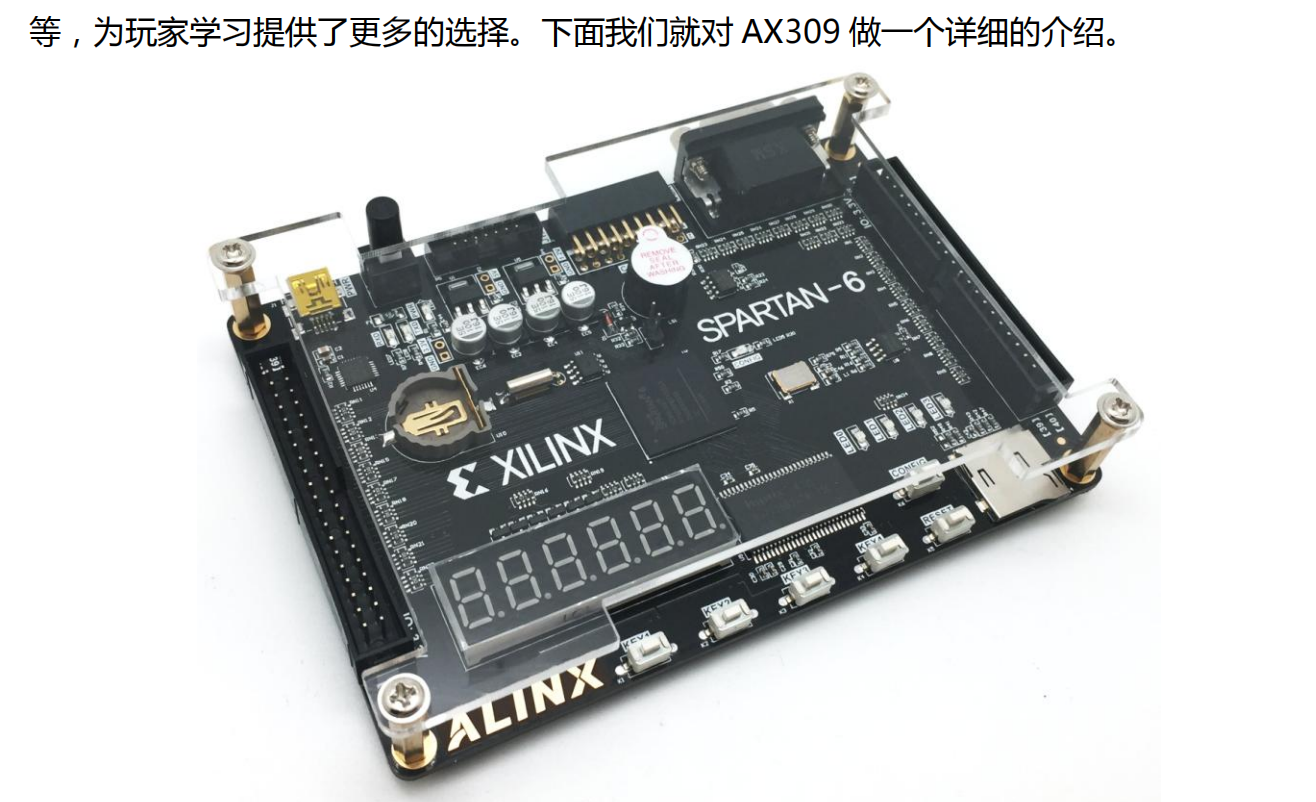

本代码已在AX309开发板验证,AX309开发板如下,其他开发板可以修改管脚适配:

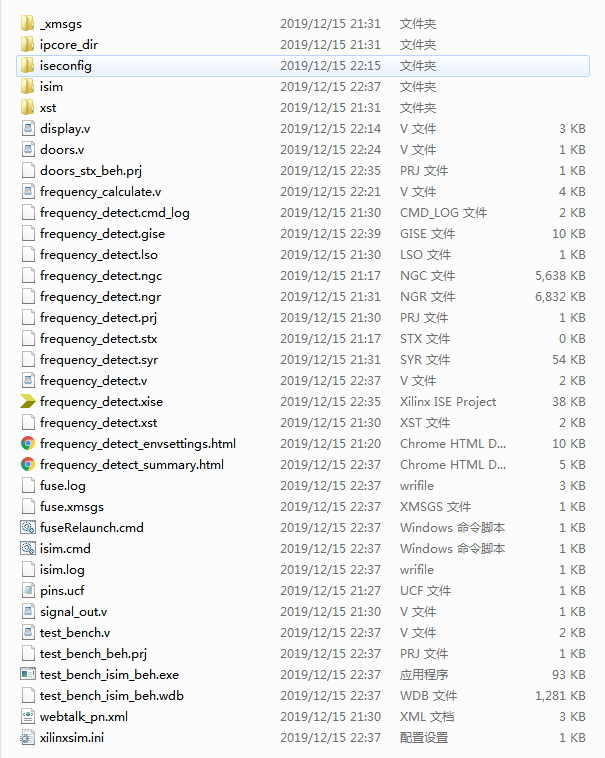

1. 工程文件

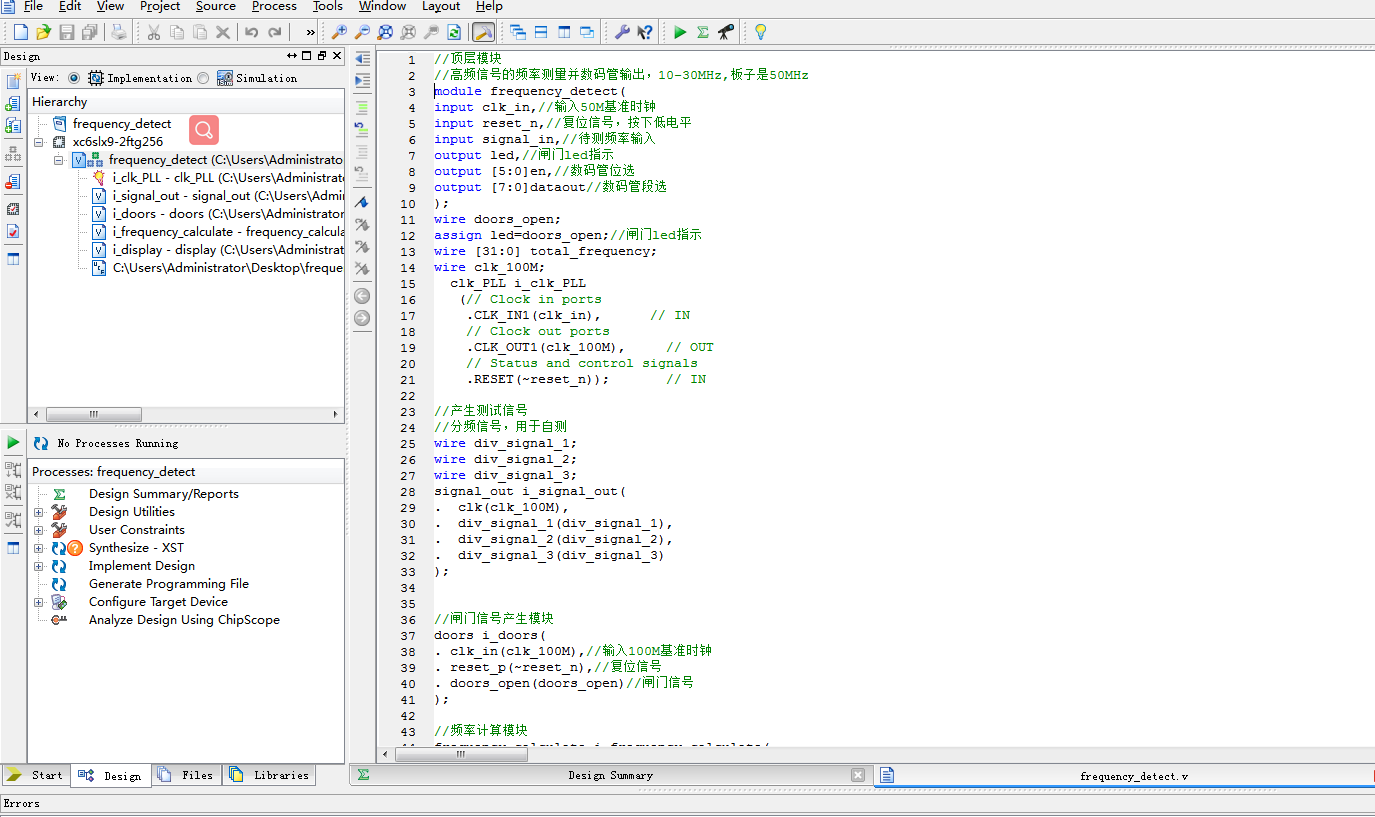

2. 程序文件

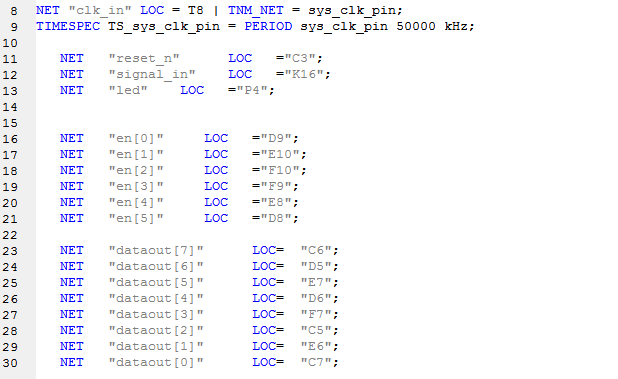

3. 管脚约束

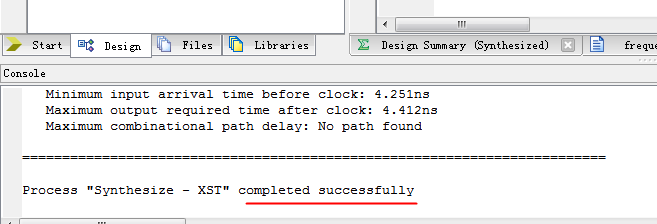

4. 程序编译

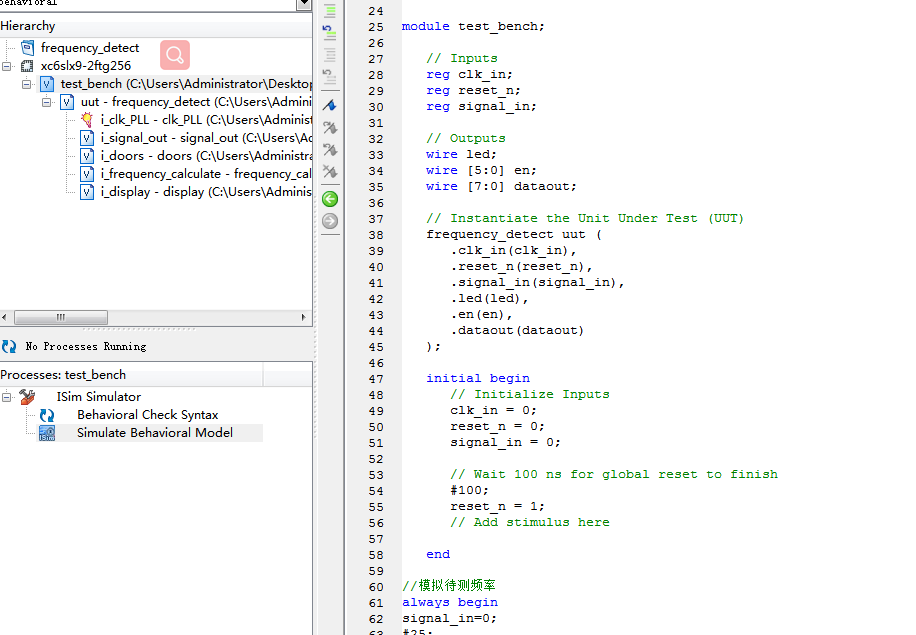

5. Testbench

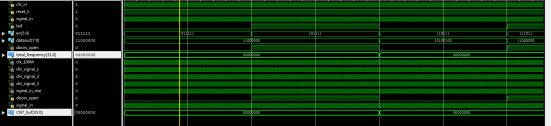

6. 仿真图

为了便于仿真,将闸门信号减小为1ms,testbench产生频率为20M,仿真结果如下:频率值为200,将其乘以1000,即为200000,单位100Hz,即20M

部分代码展示:

//频率计算模块

module frequency_calculate(

input clk_in,//输入100M基准时钟

input reset_p,//复位信号

input signal_in,//待测频率输入

input doors_open,//闸门信号

output [31:0]total_frequency//输出频率

);

reg signal_in_buf0=0;

reg signal_in_buf1=0;

wire signal_in_rise;

always@(posedge clk_in)

signal_in_buf0<=signal_in;//D触发器打拍

always@(posedge clk_in)

signal_in_buf1<=signal_in_buf0;//D触发器打拍

assign signal_in_rise=signal_in_buf0 & ~signal_in_buf1;//输入待测频率信号上升沿

wire [31:0] CNT;

//定义8位数

reg [3:0] bit0=4'd0;

reg [3:0] bit1=4'd0;

reg [3:0] bit2=4'd0;

reg [3:0] bit3=4'd0;

reg [3:0] bit4=4'd0;

reg [3:0] bit5=4'd0;

reg [3:0] bit6=4'd0;

reg [3:0] bit7=4'd0;

assign CNT={bit7,bit6,bit5,bit4,bit3,bit2,bit1,bit0};

always@(posedge clk_in)

begin

if(doors_open)//闸门开启

if(signal_in_rise)

if(bit7==4'd9 && bit6==4'd9 && bit5==4'd9 && bit4==4'd9 && bit3==4'd9 && bit2==4'd9 && bit1==4'd9 && bit0==4'd9)begin

bit7<=4'd9;

bit6<=4'd9;

bit5<=4'd9;

bit4<=4'd9;

bit3<=4'd9;

bit2<=4'd9;

bit1<=4'd9;

bit0<=4'd9;

end

else if(bit6==4'd9 && bit5==4'd9 && bit4==4'd9 && bit3==4'd9 && bit2==4'd9 && bit1==4'd9 && bit0==4'd9)begin

bit7<=bit7+4'd1;

bit6<=4'd0;

bit5<=4'd0;

bit4<=4'd0;

bit3<=4'd0;

bit2<=4'd0;

bit1<=4'd0;

bit0<=4'd0;

end

源代码

点击下方的公众号卡片获取

838

838

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?