本文转载自:数字后端物理设计(一):Floorplan - 知乎 (zhihu.com) https://zhuanlan.zhihu.com/p/264899580

https://zhuanlan.zhihu.com/p/264899580

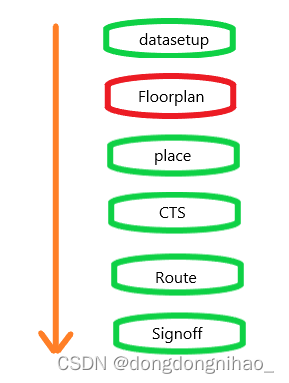

Floorplan,中文翻译:布局规划,位于数字后端的最前部。

Floorplan一般分为Full Chip level FP和Block Level FP

FCFP一般都是对一些大的芯片。BLFP主要对小芯片,或者大芯片的一个Block。

FP的重要性主要体现在对后续place/routing/drc/power的影响。一个良好的FP,或者说有经验的engineer做出来的FP。会对之后的流程特别有帮助,Floorplan就像是在建房子的时候打地基,地基打的不好不稳,后面的房子也有风险,严重情况甚至会推倒重来。

Block level Floorplan:

先说相对简单的BLFP,BLFP主要有一下几个部分组成

A:Block size/ pin location defination

顾名思义,harden block的大小,一般会以cell count的数量来限制harden的大小,比如 有的公司会限制harden的cell数量不能大于300w。pin脚的摆放位置。

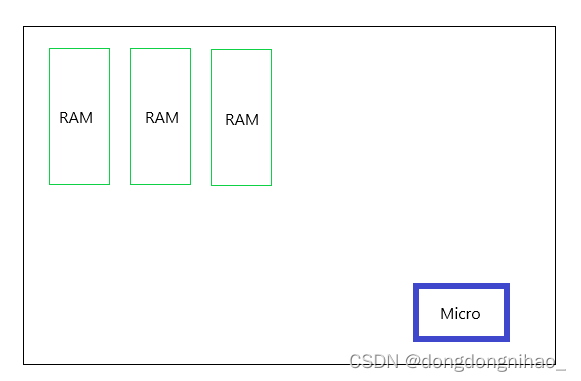

B:ram & macro placement

C:physical cell insertion

物理单元的插入

D:Build PG network

注意事项:

1:关于A,大部分block owner不需要懂这个,了解即可,会有其他人帮你定义好

2:关于B,按照优先级,先放那些macro,后放那些macro,每个公司(甚至每个工程师),都有自己的一套摆放ram/macro的规则,但是需要严格的遵守摆放规则。

3:关于 C,物理单元一般指ENDCAP和TAPCELL这两种,EDA工具可以处理这一步,偶尔需要人工参与,关于这些物理单元的功能,有兴趣的可以查一查。

4:关于D,芯片供电的规划,绝大部分在这一步完成了。

5:一般需要注意的是,ram之间不一定需要等间距,这些值需要根据pin/port/feedthrough/pg template等的情况具体分析而定。

6:最新版的innovrus mixplacement,已经支持tool直接布局了。

FullChip Floorplan:

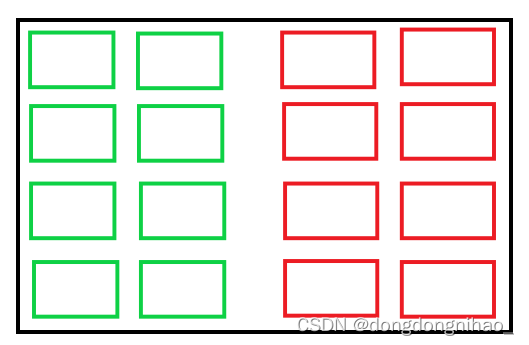

FCFP一般大型的芯片才会使用FCFP,由于大型芯片逻辑复杂,不能实现扁平化的后端设计,必须要通过分层设计(Hierachical Design)来实现,原则上FCFP中没有复杂的逻辑存在,把工作内容聚焦到FCFP上,其余绝大部分的芯片逻辑都划分到各block内部。

FCFP一般包含:

A:Block划分(split)

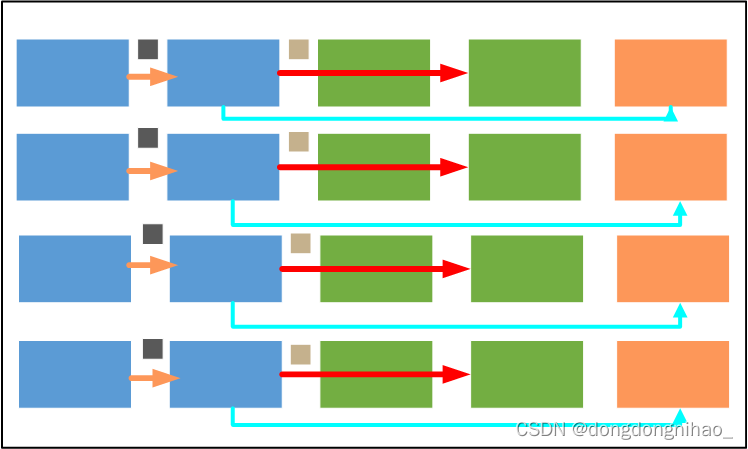

B:Block之间走线以及pin位置定义

C:Timing Budgeting and flops insertion(时间预算和触发器插入)

D:Other analog macro placement

注意事项:

1:以上只是简单示例,真实情况要复杂=很多很多。

2:如果存在Multi powerdomain,每个block只能放置在各自power domain内

3:flop insertion要按照Budgeting去做(触发器插入要有预算)

4:block划分完,还需要block owner feedback是否可行,一般会进行很多轮的迭代才能确定合适的block size和pin location。

5:keep an eye on reuse block(关注重用block)

好的,到这里简单介绍了Floorplan,FP是一个需要多次迭代才能做好的步骤,多多尝试,总能调出一个不错的FP。

实际工作中所遇到的问题远远比博客所涉及到的复杂。

我的工作是前端设计,学习一些后端知识,欢迎从事后端工作的前辈评论区点评。

4058

4058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?