确定芯片尺寸 形状

本文暂时只讨论模块级的设计。数字后端工程师会根据前端综合release的含有standard cell,Macro,IP的面积信息的report来进行模块面积的估算,需要注意的是,建议将standard cell和memory的利用率分开统计,按照经验值memory的利用率一般按80%来计算。

芯片面积的估算

IO neck和core neck一般称为IO limited和core limited

IO limited :即这个芯片的面积是由IO的个数限制,也就是因为IO过多的情况导致的芯片面积增大。这时就是通过对每个边IO个数的计算来估算面积。

core limited:即芯片面积主要有core部分决定。

芯片面积 = core面积 + power ring面积 + PAD ring面积

core面积 = standard cell面积 + RAM面积 + Macro面积

RAM面积 = RAM自身面积 + RAM power ring面积 + keepout面积 + mbist面积 (mibist内存自检)

以上就是基本估算方式(下次再详细补充)

芯片大小

IO单元,Pad Filler和Corner Pad的位置

建立physical only cells 添加IO Corner 、Filler 、Corner Pad

IO :我们要对IO编写约束文件,以此指定IO放置位置以及排列顺序。如下图1-1其中IO corner并不是必须的,当芯片只有一边或对边有IO时,为了节省面积不使用IO corner,但是对于出现相邻边有IO时一般会差人IO corner (IO corner 又称Corner Pad)。

图1-1

Pad Filler : 插入Pad Filler的目的是为了链接两个 相邻的IO,以此实现从衬底到各个金属层的链接,为IO内部电路形成电源地线环路。因此只有当IO之间存在缝隙时才需要插入,否则会出现DRC和LVS问题,Corner Pad的目的也是相同的。具体如下图1-2。

图1-2 IO Pad

Macro的放置和Blockage的规划

对于FloorPlan阶段,Macro的摆放是十分重要的

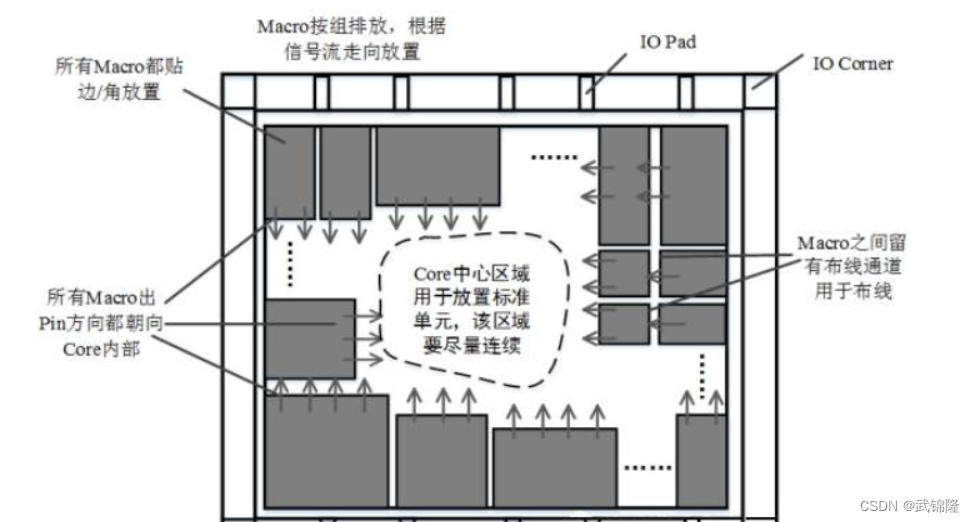

FloorPlan的摆放需要考虑到面积,互连线的长度,Place阶段standard cell的摆放。一般我们采用edgeplace(边缘摆放法。具体摆放原则参考下图1-3。

图1-3 Maacro摆放规则

-

大的Macro尽量贴边摆放这样有利于空间的利用,可以再core留出一块完整连续的接近方形或圆形的区域来放置standard cells,一定要注意不要出现突起或细小的凹陷容易出现泳池效应。

-

Macro尽量摆放在有talk的IO pad附近因为并不是Macro只与standard cell或者其他Macro有信息交换,可能还需要通过IO Pad与外界进行交互,而摆放在对应的IO Pad附近有利于减小互连线长度,减少线延迟,节省绕线资源。

-

Macro之间要保持一定的距离这样是为了给予布线资源,特别是相邻的Pin很多的情况需要空出更大的位置,可以根据pin的多寡来控制Macro之间的间距,可以通过给Macro加Keepout margin的方式来控制间距。

-

合理设置Macro摆放的角度Macro只能镜像翻转,所以我们尽量将pin口朝向talk多的方向。

接下来需要进行Blockage的设置了

在Macro摆放完成后,我们可以通过EDA工具的虚拟布局,来检查是否有utilization和congestion的出现,并对出现这样问题的地方通过各种blockage来进行密度规划,以预防Place阶段出现congestion的问题。此外还需要在Macro周边设置Keepout margin来更方便的在Macro周边放置PG ring,而且可以避免Macro周围的布线DRC问题。

电源地线网络的分布

电源规划的目标:

- 给所有Macro供电

- 给所有standard cell供电

- 产生一个可以满足IR/EM的供电网络

- 做到Base DRC clean

电源网络规划的第一步,一定是先把电流引入到block中,那么就需要通过power ring从供电IO引入电流,而为了均匀供电并且缩短电流回路,在有效降低IR的同时防止电流分布不均导致的hot spot和EM问题。power ring的设计主要有三个需要特别注意的地方,分别是power ring宽度,间距,数量。其中宽度根据电流密度以及电源环对数决定。间距则根据厂家给出的设计规则中的最小间距决定。一般情况下为最小间距的两倍。

接下来通过power stripes把电流输送到芯片内部的各个Macro上。其中需要注意power stripes的垂直走线的宽度、水平走线的宽度、垂直走线间的间距、水平走线间的间距。一般情况下根据芯片的利用率来选择走线的宽度与间距,在利用率低的情况下当然选择更大的宽度,反之在采用细密的电源网络。注意受到不通过工艺的影响区别会非常大。

接下来通过power rail来为standard cell进行供电,其间距要是site的高度。只要将其与power ring或power stripes相连。

然后使用PNA对power plan进行分析检查IR drop是否合格。(PNA 数字式端口网络分析仪)

最后通过DRC检查Macro、standard cell、powerplan是否存在physical DRC。

文章讲述了芯片设计中的一些关键步骤,包括根据模块面积估算确定芯片尺寸,IO单元如PadFiller和CornerPad的定位,Macro的放置策略以避免Blockage问题,以及电源地线网络的分布以确保IR/EM的满足。同时强调了Macro与IOpad的关系,以及功率环设计的注意事项。

文章讲述了芯片设计中的一些关键步骤,包括根据模块面积估算确定芯片尺寸,IO单元如PadFiller和CornerPad的定位,Macro的放置策略以避免Blockage问题,以及电源地线网络的分布以确保IR/EM的满足。同时强调了Macro与IOpad的关系,以及功率环设计的注意事项。

4112

4112

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?