目录

前言:

今天发现了一个宝藏文档(这也反映出了我有多菜,这么晚才发现)synopsys官方的timing约束手册。通过官方文档中的描述来一起学习一下这个path group约束。

定义:

设计的时序路径被组织成group的形式,默认情况下,设计中每个时钟域有一个path group。

作用:

设计path group中的所有path都会经过优化,从violation最大的path(即critical path)开始优化,在violation 最大path被优化完以后,开始优化第二差的path,直到group中所有的path violation被优化到0,或者直到一个更好的优化方案被发现。举个例子,一个设计中有两个CLK,那么两个CLK域就被分为两个path group,dc会依次进行优化,你可以选择性的切分group中的path用来控制优化的聚焦点。比如,假如你不清楚input delay该约束多少,那你可以把input - to -register path设定为一个separate path,这样的话input - to -register path就会与group中的其他path分开优化。

命令:

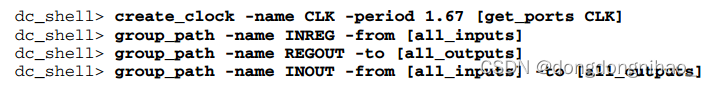

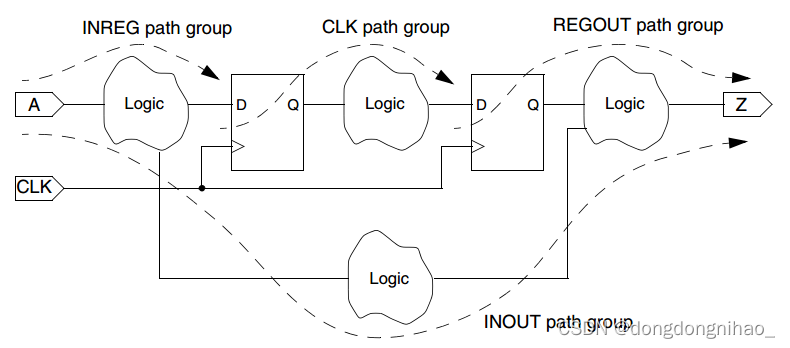

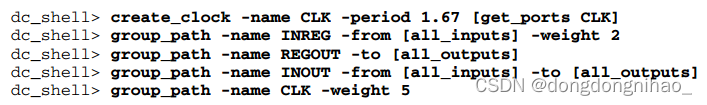

上面这三个命令将input to register register to output 和 input to output 从path group中分隔开。【register to register 的path还是保留在默认的CLK path group中】

通过这种路径分组,在优化输入相关或输出相关定时路径时遇到的任何问题都不会影响寄存器到寄存器路径的优化。

此外,report_timing命令分别报告每个路径组中的最差路径,因此你可以分别从输入相关路径和输出相关路径中找出最差的寄存器到寄存器路径。

举例:

如上述命令所示:

你也可以设置每条约束的权重,这样综合工具就会在优化目标时进行对应的 “努力”, -weight的默认值是1(即你不加-weight就是1),higher the weighting, higher the effort。上面例子中就是设置register to register 5,input to register 2,其他的没有设置就是1。

类似的,开发人员还可以通过命令- critical_range 设置critical path的slake 范围。综合工具就会“想办法”将critical path的timing 优化到设定的范围内。

2669

2669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?