目录

一、序言

在Vivado的时序约束窗口中,存在一类特殊的约束,划分在others目录下,可用于设置忽略或修改默认的时序路径分析,以Vivado2022.1版本为例,主要包括以下4类,本文将介绍其中的Group Path,示例的为Vivado2022.1

二、Group Path

2.1 基本概念

Group path约束可以让用户改变一组路径的成本功能计算,可通俗理解基于时序驱动的布局布线过程中设置的路径有优先权。正常情况下,为了一些特殊情况的处理,Vivado 工具会自动地定义时钟信号的路径组。也可以通过用户定义起点,终点或起点,中间路径,终点的来设定路径组。一旦创建了路径组,执行report_timing时,时序分析将会作用于路径组。

用户可以在已存在的时钟路径组中指定一个权重,让布局,布线,以及优化流程优先处理这些路径,主要可以优化时序。

优点:通过设置路径组可以减少false path的数量,以及由于对于所有路径使用全局约束带来的时序违例,并且因每个组中路径的关联性从而提高时序分析的准确性和效率,简化时序报告。最后,也可以将和特定模块,功能的路径约束到相同的组,生成单独的报告进行分析。

缺点:设置Group path对于时序分析工具处理更复杂,比如增加了定义和管理路径组的复杂度,因为这个对每个组都需要创建和更新多个约束文件和脚本,保证在设计改变时相互间的兼容性和一致性。另外,在路径组中存在丢失或错误路径的风险,这将导致不准确或不完全的时序分析

2.2 设置界面

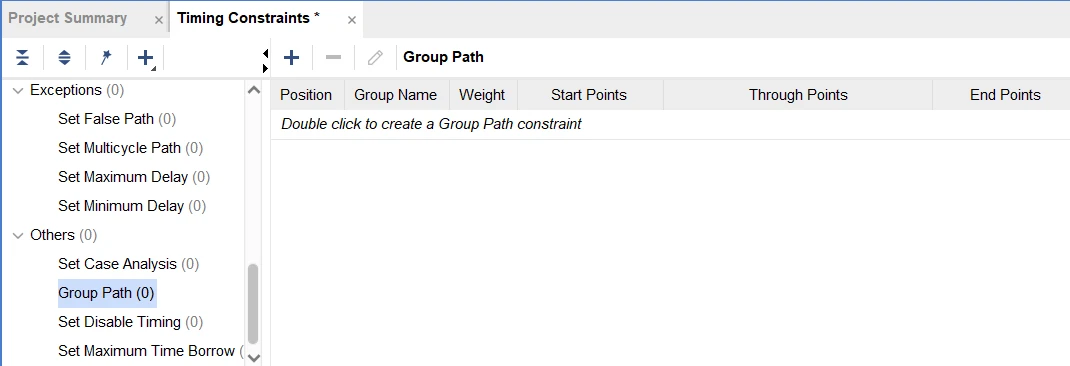

进入Timing Constraints界面,在左侧Others栏中选中Group Path,右侧即显示Group Path界面,双击空白位置

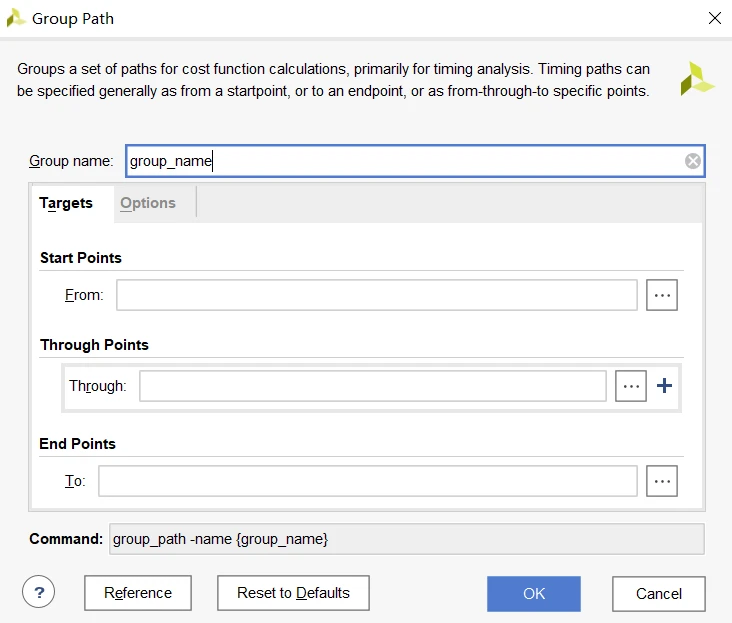

Group Path页面有两个子页面Targets和Options,Targets中Group name设置路径组的名称,再依次设置起点,中间节点,终点。

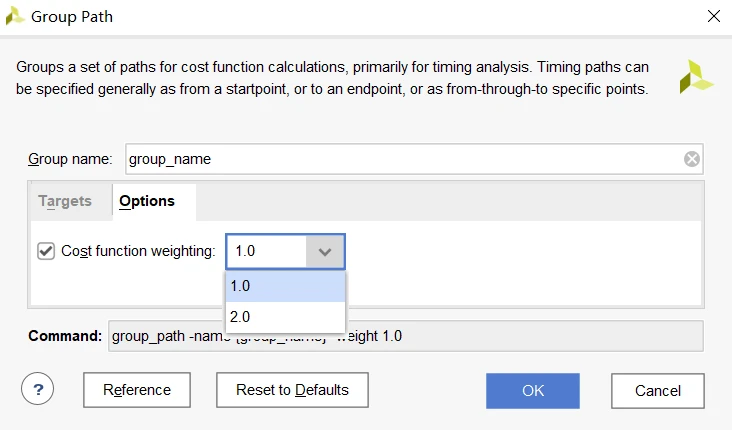

Options界面设置权重值,可以1或2,默认为1。

2.3 命令语法

命令格式如下

group_path [‑name <args>] [‑weight <arg>] [‑default] [‑from <args>] [‑to <args>] [‑through <args>] [‑quiet] [‑verbose]参数含义列表如下

2.4 命令示例

1)设置一个路径组名称为signal_grp,路径的终点为指定的信号或寄存器的D口

group_path -to [get_pins *signal*reg/D -hierarchical] -name signal_grp2)使用get_path_groups可以获取路径组信息

get_path_groups signal_grp3)通过参数default可以移除设置的路径组,使路径恢复到默认的路径组

group_path -to [get_pins *signal*reg/D -hierarchical] -default三、工程示例

工程代码:

module timing_analysis(d1,d2,clk1,clk2,clk3,clk4,rst,out1,out2); input d1,d2,clk1,clk2,clk3,clk4,rst; output out1,out2; reg ff1,ff2,ff3,ff4,ff5; always @(posedge clk1) if(!rst) ff1<=0; else ff1<=d1; always @(posedge clk2) if(!rst) ff2<=0; else ff2<=ff1; always @(posedge clk3) if(!rst) ff3<=0; else ff3<=ff2; assign out1=ff3&ff2; always @(posedge clk4) if(!rst) ff4<=0; else ff4<=d2; always @(posedge clk4) if(!rst) ff5<=0; else ff5<=ff4; assign out2=ff5; endmodule 综合后网表连接图

约束内容如下,设置clk1和clk2的路径组

create_clock -period 10.000 -name clk1 -waveform {0.000 5.000} [get_ports clk1]

create_clock -period 7.000 -name clk2 -waveform {0.000 3.500} [get_ports clk2]

create_clock -period 8.000 -name clk3 -waveform {0.000 5.000} [get_ports clk3]

create_clock -period 5.000 -name clk4 -waveform {0.000 3.500} [get_ports clk4]

set_input_jitter [get_clocks clk1] 1.660

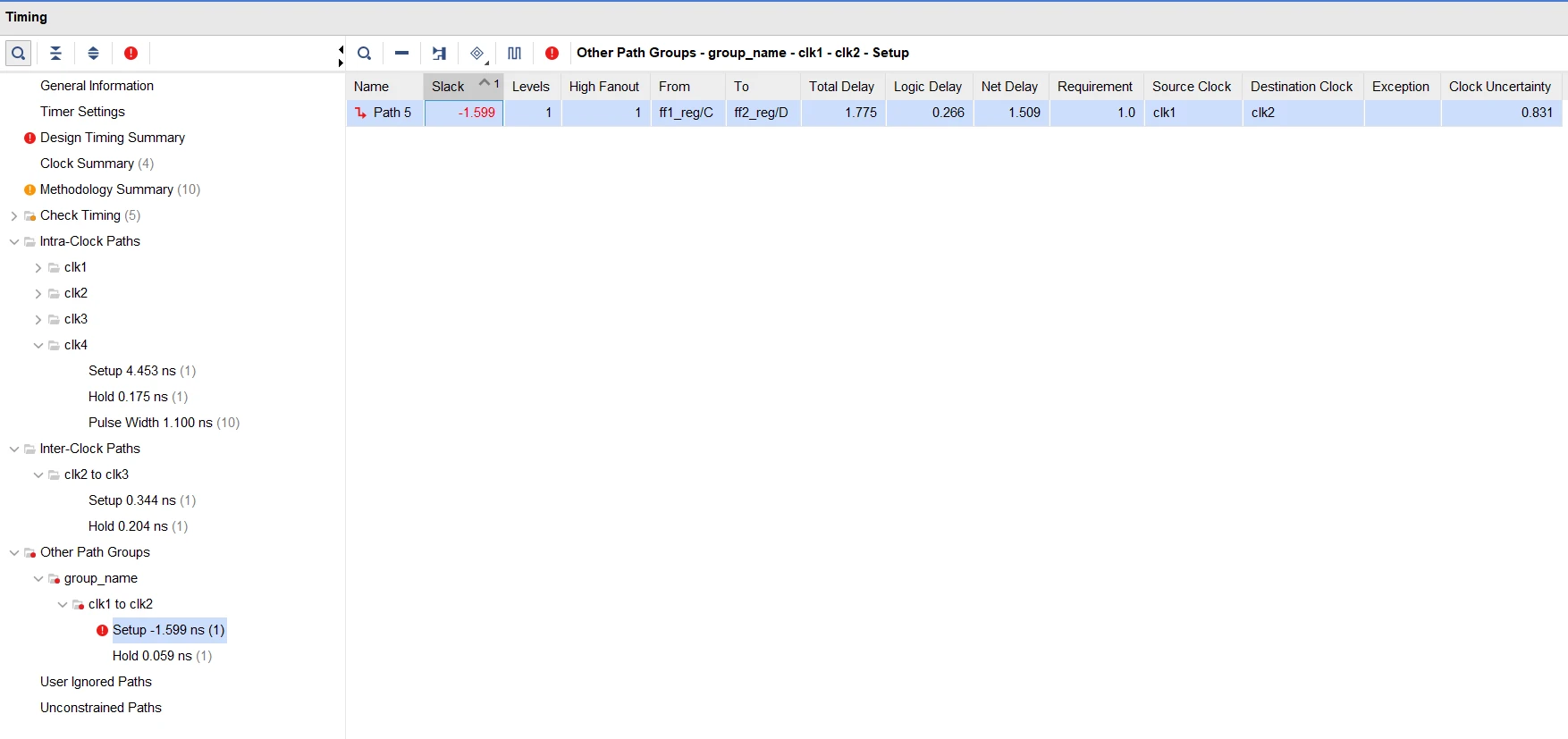

group_path -name {group_name} -weight 2.000 -from [get_clocks clk1] -to [get_clocks clk2]时序结果,设置了group_path的路径展示在报告的Other Path Groups中

四、参考文件

1、用户手册《ug835-vivado-tcl-commands-en-us-2023.1.pdf》

文档链接:https://pan.baidu.com/s/1Su_w9CDHR7R9_tt_in_arQ?pwd=7w4f

提取码:7w4f

2、Vivado的command reference

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?