我们一直有这样的说法,startpoint的fanout大会导致path的delay增大,但是为什么会增大呢?

在后端进行CTS阶段,首先要进行的就是drc(design rules check)要满足drc需要面临的问题有2个,一个是input transition(slew),另一个是fanout,transition又分为signal transition和clock transition ,而且clock trasition要求会更加严格一点。

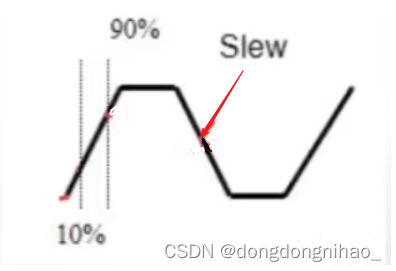

这里要搞清楚一个知识点,信号的slew 和transition的区别是什么?

slew rate:信号改变的速率

transition time:信号改变的持续时间

在STA中,一个上升或者下降的波形通常用slew rate来表征其跳变的快慢,如下图所示:

transition time就是用来记录这个信号在两个电平之间的转换时间,它两的关系互为倒数,transition time 如果越大 slew rate就会越慢,反之同理。

startpoint的fanout越大,下一级net的电容就越大,rc乘积变大,input_transition time就会越大,而std cell的delay和input_transition和output_load有关,input_transition time越大会严重增大这个单元的延迟,而对于fanout大的情况,后端就会插入buffer,这条path的delay就会变大,从而导致violation发生。这也就是我们常说的负载越大,驱动能力越弱。

因此设计人员一般可以采用在violation path插入DFF的形式来解这些fanout过大导致的timing问题。

也可以通过约束的方法设定某个驱动的最大负载,可以看一下这位博主的讲解,我没看懂他在说什么?

关于set_max_fanout的准确理解和说明 - 微波EDA网 (mweda.com)

本文探讨了在集成电路设计中,startpoint的fanout增加如何导致路径延时增大的原理。详细解释了信号的slewrate与transitiontime的概念及其相互关系,并介绍了如何通过插入DFF或设置最大负载来解决由fanout过大引起的timing问题。

本文探讨了在集成电路设计中,startpoint的fanout增加如何导致路径延时增大的原理。详细解释了信号的slewrate与transitiontime的概念及其相互关系,并介绍了如何通过插入DFF或设置最大负载来解决由fanout过大引起的timing问题。

1377

1377

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?