简介

本文可让开发者们看懂 AMD Vivado™ Design Tool 2023.2 中的“AMD Versal™ Adaptive SoC CPM PCIE PIO EP 设计”CED 示例。

“AMD Versal Adaptive SoC CPM PCIE PIO EP 设计”支持您使用可以正常工作的既定设计来初始化您的系统开发板,以验证此开发板的连接与功能。

PCI Express 系统主机 CPU 通常使用编程输入/输出 (PIO) 传输事务来访问 PCI Express 逻辑中的存储映射输入/输出 (MMIO) 位置和配置映射输入/输出 (CMIO) 位置。

Endpoints for PCI Express 可接受“Memory and I/O Write”传输事务,并以“Completion with Data”传输事务来响应“Memory and I/O Read”传输事务。

功能特性

AMD Versal™ Adaptive SoC PIO 设计的 CED 示例按“DWORD Aligned Mode”来配置。以下提供了您可利用设计示例来实践的部分功能特性:

-

此设计在 AMD Versal Adaptive SoC 器件块 RAM 内实现一个目标空间。

-

此目标空间可通过存储器写 32 TLP 和存储器读 32 TLP 来访问。

-

对于来自核的有效的存储器读 32 TLP 请求,PIO 会生成完成包(大小即有效载荷的大小)以作为响应。

-

PIO 设计会通过将有效载荷更新到 AMD Versal Adaptive SoC 器件中的块 RAM 空间的目标地址内来处理 1DW/2DW 存储器写或 I/O 写 TLP。

如需了解 PIO 设计示例工作原理背后的架构与机制的更多详情,请参阅:

https://docs.xilinx.com/r/en-US/pg343-pcie-versal/PIO-Hardware

虽然此链接指向 PL PCIE IP 核设计示例,但 AMD Versal Adaptive SoC PIO 设计的 CED 示例同样基于此设计示例,因此该链接中提供的详细信息同样适用于 CPM PIO 设计。

设计生成

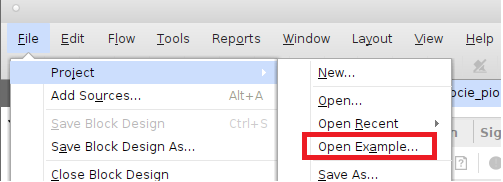

在 AMD Vivado™ Design Tool 中,转至“File -> Project -> Open Example”。

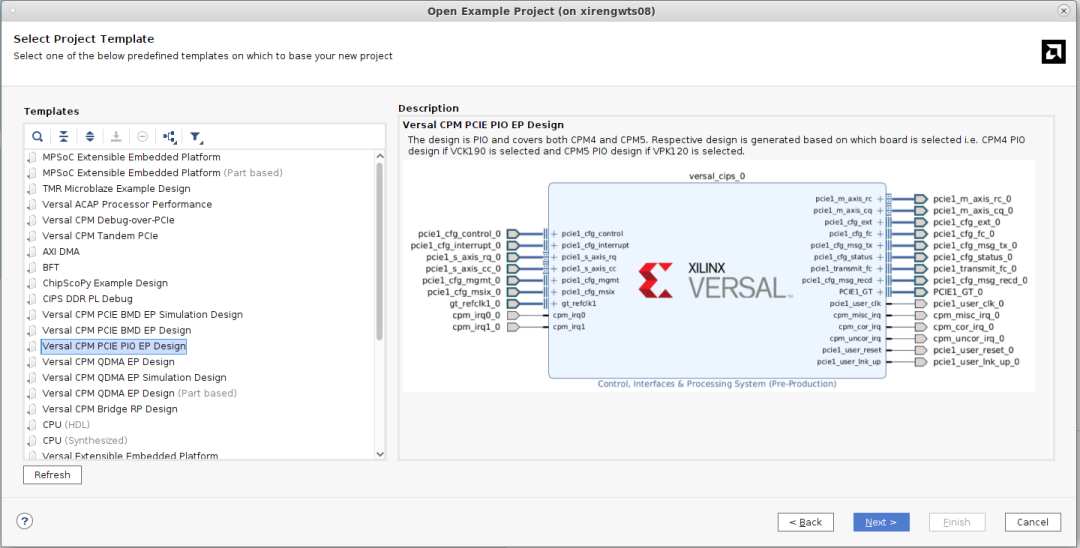

这样即可看到如下可用示例列表。选中“AMD Versal™ Adaptive SoC CPM PCIE PIO EP Design”,然后单击“Next”。

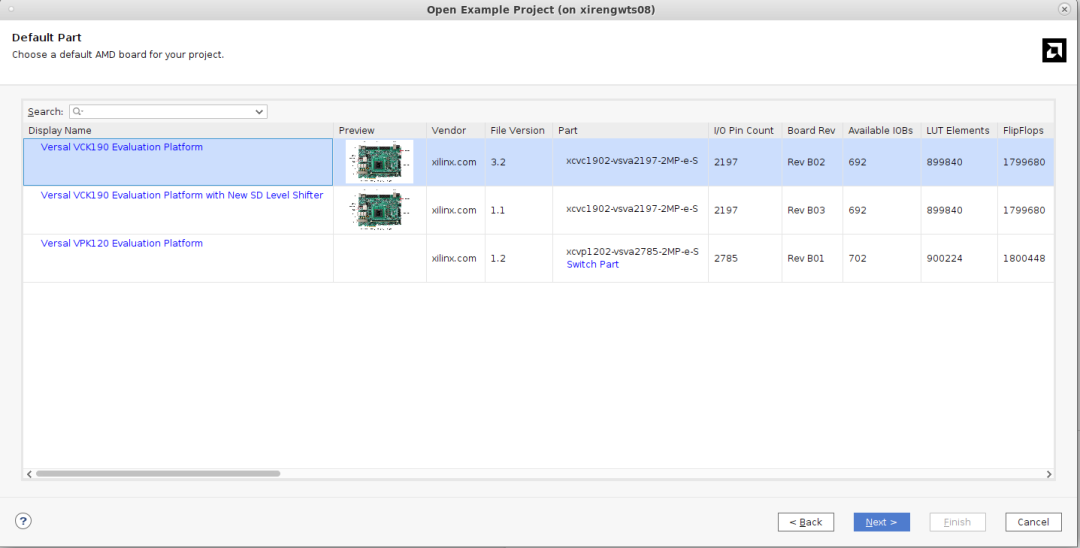

所提供的设计示例支持 VCK190 评估板和 VCK120 评估板。对于其他开发板,为其中任一开发板生成的设计示例均可作为参考用于为所需开发板进行设计转换。

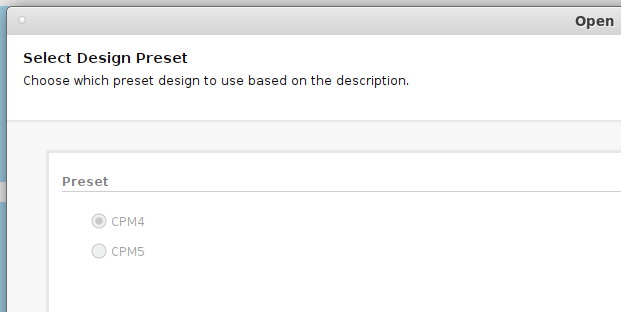

根据所选开发板,将自动选择“Preset”,针对 VCK190 将选中 CPM4,针对 VPK120 则选中 CPM5。

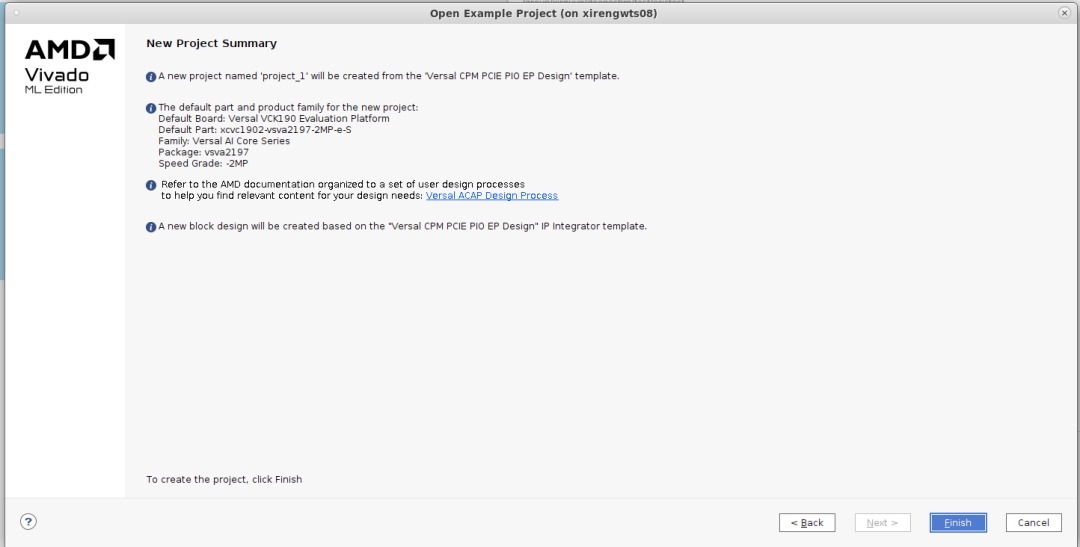

复查工程汇总信息,确认所选部件和产品系列正确。

CPM 配置

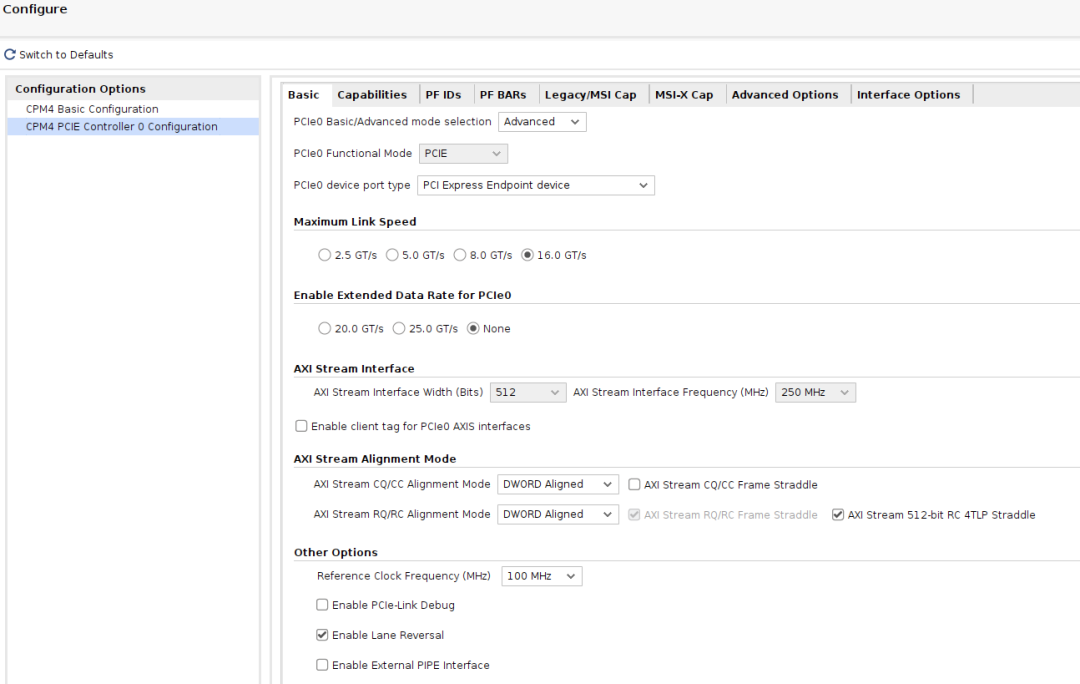

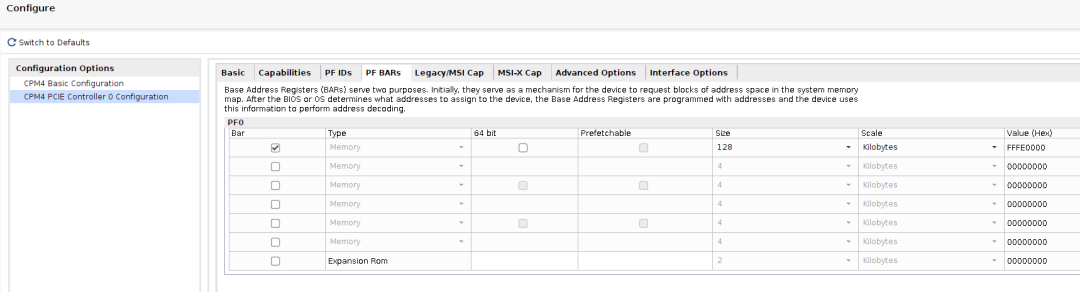

生成的默认 AMD Versal™ Adaptive SoC CPM PCIE PIO EP 设计配置如下:

-

Gen4x8。

-

DWORD 对齐。

-

启用 AXI Stream 512 位 RC 4TLP 跨接。

-

禁用 AXI Stream CQ/CC 跨帧。

-

启用通道翻转。

-

使用 PCIE 控制器 0。

-

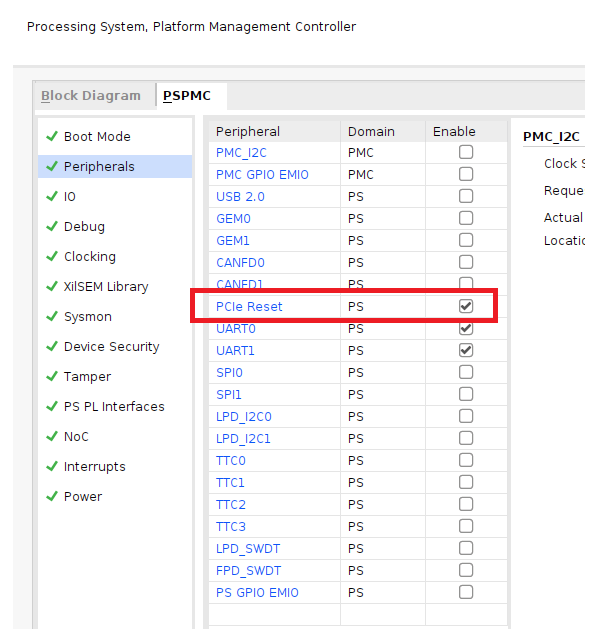

针对所选开发板和控制器将复位配置到 PMC_MIO 38。

PS PMC 配置

设计示例模块框图

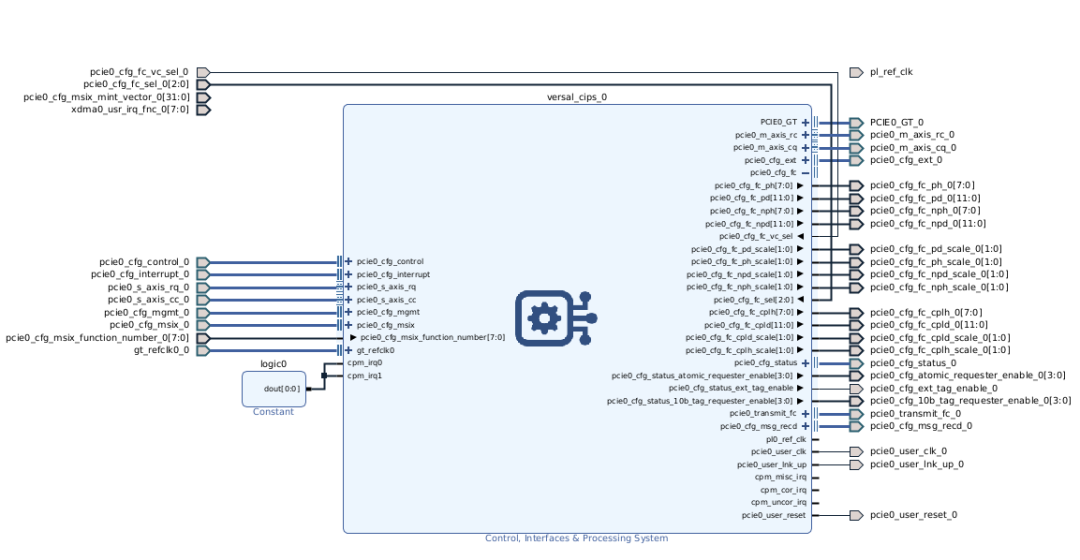

以下是生成的 CIPS 的最终模块框图。I/O 和复位约束均由设计示例基于所选开发板来进行分配。

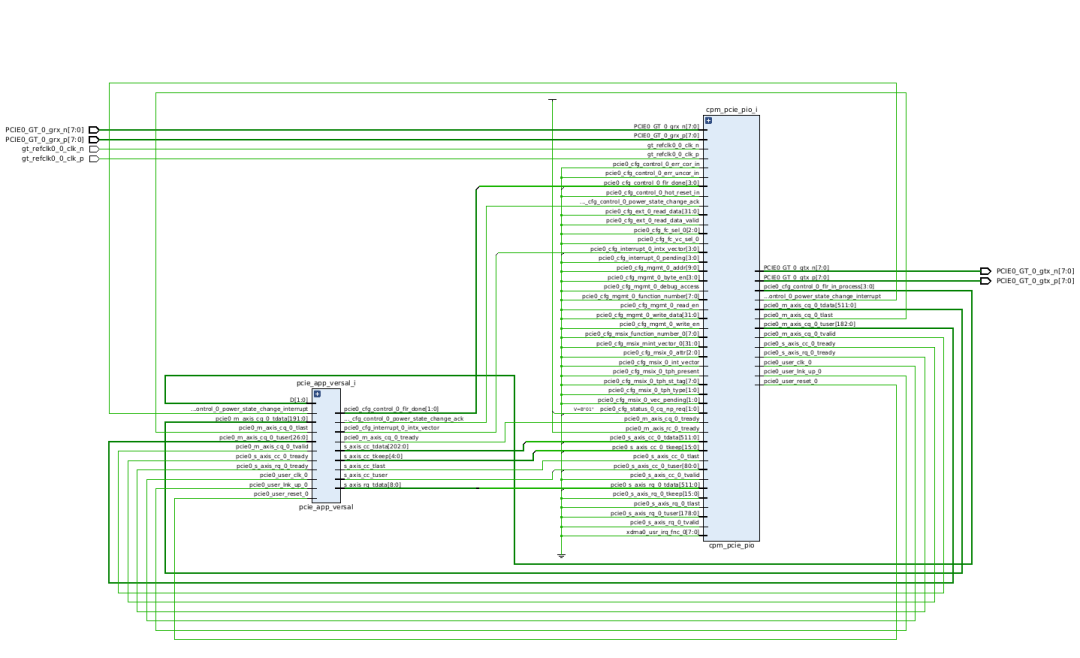

以下板级原理图设计显示了由 CPM 与 PIO 应用在后端组成的整体设计示例。

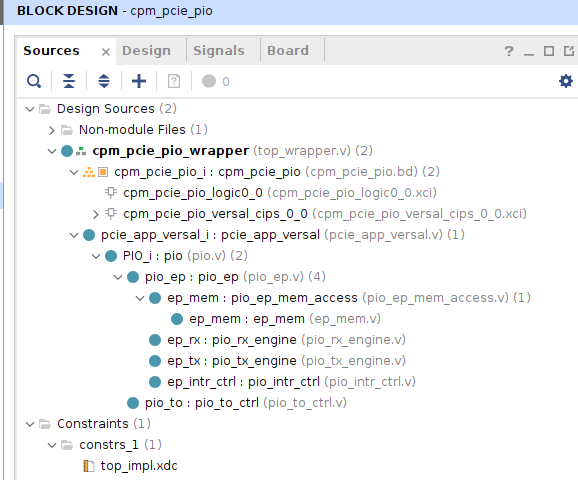

设计示例源文件

pcie_app_versal_i 是设计示例模块,负责处理传入的“Memory Read”和“Memory Write”,并以“Completion”包来响应。

下表显示了 PIO 示例设计的文件结构。

| 文件 | 描述 |

| PIO.v | 顶层设计封装 |

| PIO_INTR_CTRL.v | PIO 中断控制器 |

| PIO_EP.v | PIO 应用模块 |

| PIO_TO_CTRL.v | PIO 关闭控制器模块 |

| PIO_RX_ENGINE.v | 32 位接收引擎 |

| PIO_TX_ENGINE.v | 32 位发射引擎 |

| PIO_EP_MEM_ACCESS.v | 端点存储器访问模块 |

| PIO_EP_MEM.v | 端点存储器 |

| PIO_EP_XPM_SDRAM_WRAP.v | 采用 Dword 对齐模式的端点存储器 |

如需了解更多详细信息,请访问:

https://docs.xilinx.com/r/en-US/pg343-pcie-versal/PIO-File-Structure

设计运行

请参阅以下链接,了解有关在“Memory Read”传输事务与“Memory Write”传输事务期间,设计示例中的内部信号的翻转方式的详细信息。

-

https://docs.xilinx.com/r/en-US/pg343-pcie-versal/PIO-Read-Transaction

-

https://docs.xilinx.com/r/en-US/pg343-pcie-versal/PIO-Write-Transaction

设计测试

您可从主机系统使用“Devmem”之类的应用发起“Memory Read”传输事务与“Memory Write”传输事务,如验证 AMD Versal™ Adaptive SoC PCIe 存储器写/存储器读/完成传输事务中所述。

https://support.xilinx.com/s/article/000034419?language=zh_CN

255

255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?