ZYNQ 导出 package delay

在ZYNQ 7000系列SOC 的PCB设计中,赛灵思明确要求DDR的走线需要包含器件的package delays.如下图所示:

下面我们就开始介绍如何导出ZYNQ系列SOC的器件package delay

一、打开Vivado开发软件,找到TCL 控制台输入接口

二、在下方输入框中,输入如下命令:

link_design -part xc7z020clg484-2

命令中 -part 后为需要导出管脚延迟的SOC的具体芯片型号和封装,然后回车,开始执行该TCL命令。执行完成后,如下图所示:

三、再次输入如下命令

write_csv xc7z020clg484-2

此命令将以excel表格的形式输出管脚延迟信息。同时给出了该excel表格的路径和文件名。

四、预览延迟信息

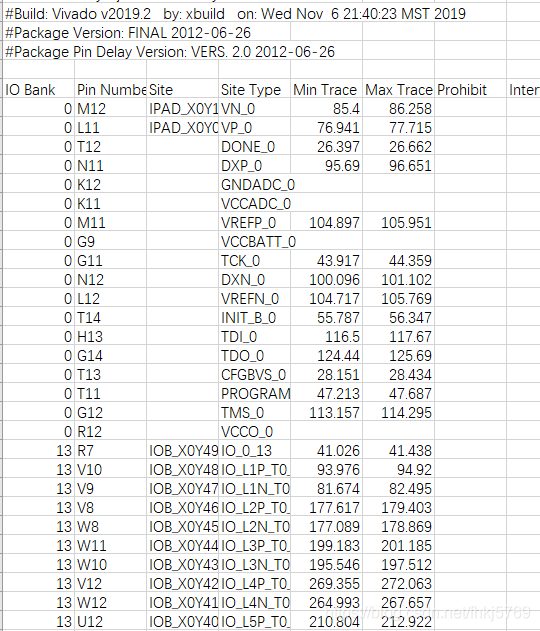

打开文档后,如下图所示:

其中所有的管脚延时分为最大和最新延时两类,单位为ps。我们在进行PCB设计时,可以将最大最小值做平均,并使用1ps约等于6mil的关系将其转换为长度即可。

715

715

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?