8B/10B编码、扰码对数字信号的比特级进行随机处理,减少连0和连1的出现,从而减少码间干扰和抖动,方便接收端的时钟提取。

8B/10B编码

8B/10B编码不打算说太多,因为网上的解释很多,在我的工作内容中,涉及到K码的只有JESD204B接口的时候,在JESD204B代码组同步(code group sync)中,当发送端检测到SYNC 信号为低电平时启动发送8B10B中的K28.5码,本数据段不进行扰码和字节替换操作,接收端检测到最少4个K28.5后可释放SYNC信号。

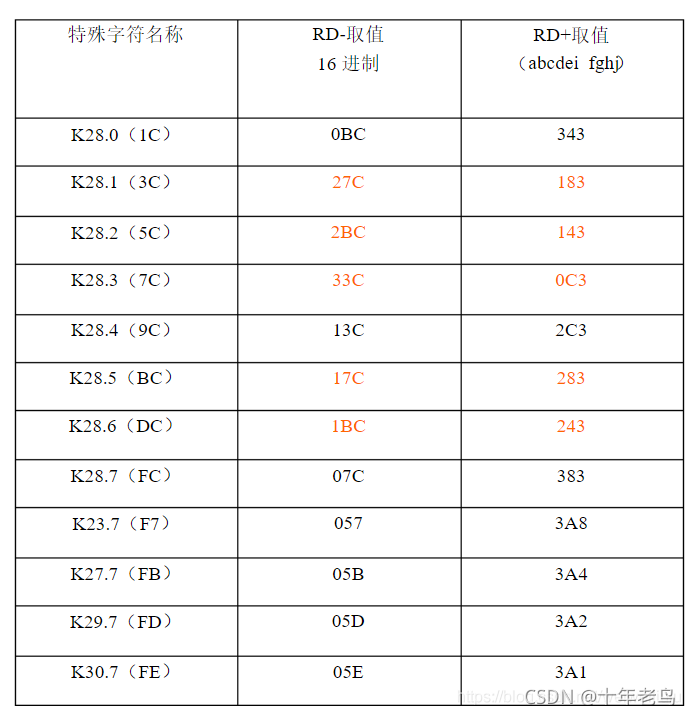

K码

扩展:特殊字符 16 进制表示。K28.5 = 16’hBC

66B/64B编码

64B/66B编码将64bit数据或控制信息编码成66bit块传输,66bit块的前两位表示同步头,主要由于接收端的数据对齐和接收数据位流的同步。同步头有“01”和“10”两种,“01“表示后面的64bit都是数据,“10”表示后面的64bit是数据信息。

数据信息0和1

本文总结了8B/10B编码、66B/64B编码以及扰码在数字信号处理中的作用,旨在减少码间干扰和抖动,便于时钟提取。8B/10B编码在JESD204B接口中利用K28.5码进行同步;66B/66B编码通过前两位同步头实现数据对齐和同步;扰码则通过特定多项式电路实现数据的随机化,防止连续0或1的出现。文中还提供了扰码与解扰的Verilog代码实例,并提到了工程中需要注意的高低位调换和初始相位匹配问题。

本文总结了8B/10B编码、66B/64B编码以及扰码在数字信号处理中的作用,旨在减少码间干扰和抖动,便于时钟提取。8B/10B编码在JESD204B接口中利用K28.5码进行同步;66B/66B编码通过前两位同步头实现数据对齐和同步;扰码则通过特定多项式电路实现数据的随机化,防止连续0或1的出现。文中还提供了扰码与解扰的Verilog代码实例,并提到了工程中需要注意的高低位调换和初始相位匹配问题。

订阅专栏 解锁全文

订阅专栏 解锁全文

5924

5924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?