学习资料

🔗百度网盘 密码:csdn

Synopsys Verification Continuum的静态验证平台VC static platform包含了VC LP,VC formal,VC Spyglass三种静态检查工具。Spyglass原是Atrenta旗下的静态检查工具,占据CDC/RDC sign-off工具的大部分市场份额。后来Synopsys收购了Atrenta,整合Spyglass推出了VC Spyglass。VC Spyglass作为Synopsys推出的期望继承Spyglass的新一代产品,兼容原有Spyglass的Use Mode,提供更高性能和更多功能,和PT/DC工具的命令兼容,采用Verdi的debug界面,加入Machine Learning,低误报,对Netlist/低功耗的支持等优势。

本专题将介绍VC Spyglass CDC的相关应用。

CDC与亚稳态

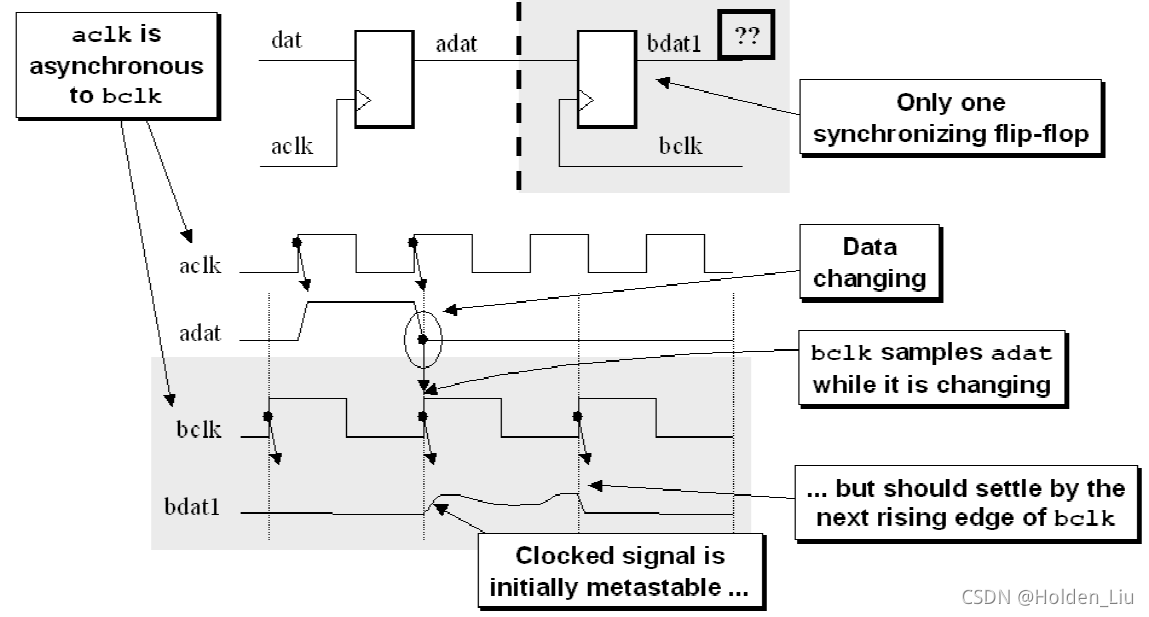

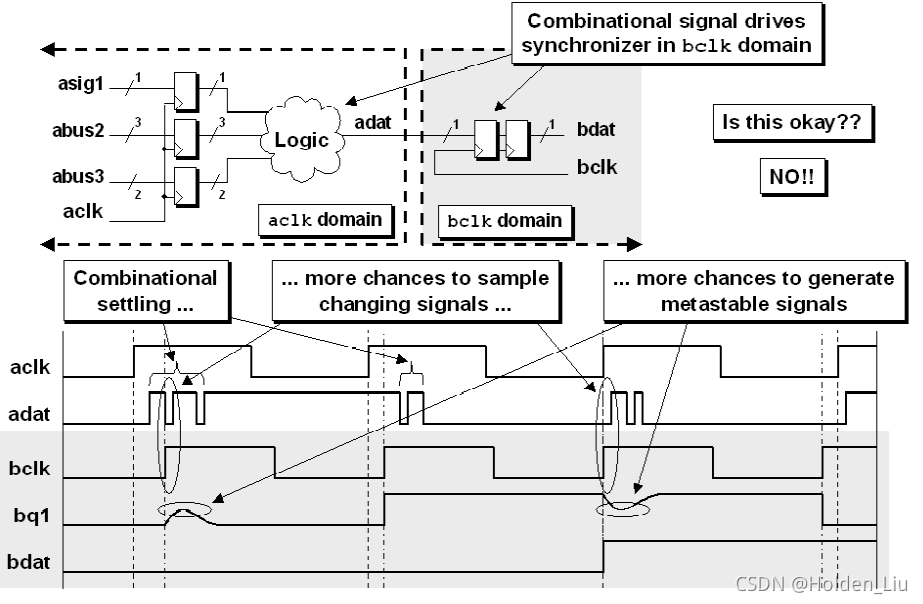

Clock Domain Crossing (CDC) : 跨时钟域设计中,信号adat从aclk domain传播到bclk domain;aclk与bclk之间的频率,相位没有固定关系,为asynchronous异步关系的时钟。

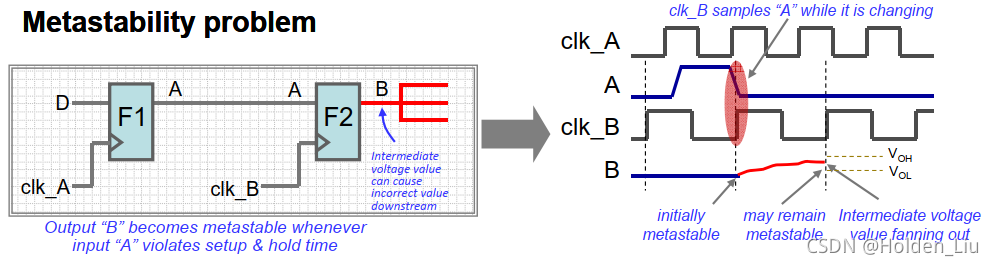

Metastability: 当adat在bclk采样点附近变化时,不满足后级flip-flop的setup/hold time,D端无法完成正确的锁存,Q端的输出在较长一段时间内处于不确定的振荡值,出现亚稳态的现象。

亚稳态传播给后级组合逻辑时,后仿中的不确定的X态会传播出去,影响电路功能。

Note:

Synchronous clock domains在时钟约束和时钟树正确的情况下,不属于CDC这类情况,不会产生亚稳态;qasi synchronous: 时钟同源,由同一个分频器产生,频率为整数倍关系,相位差固定,为准同步时钟关系。时钟的抖动和偏移的不确定性存在一定关系。此时也可以当作同步电路处理。- 相比于

sequential logic,combinatorial logic的特性导致其更容易传播亚稳态和产生glitch。

Synchronizer

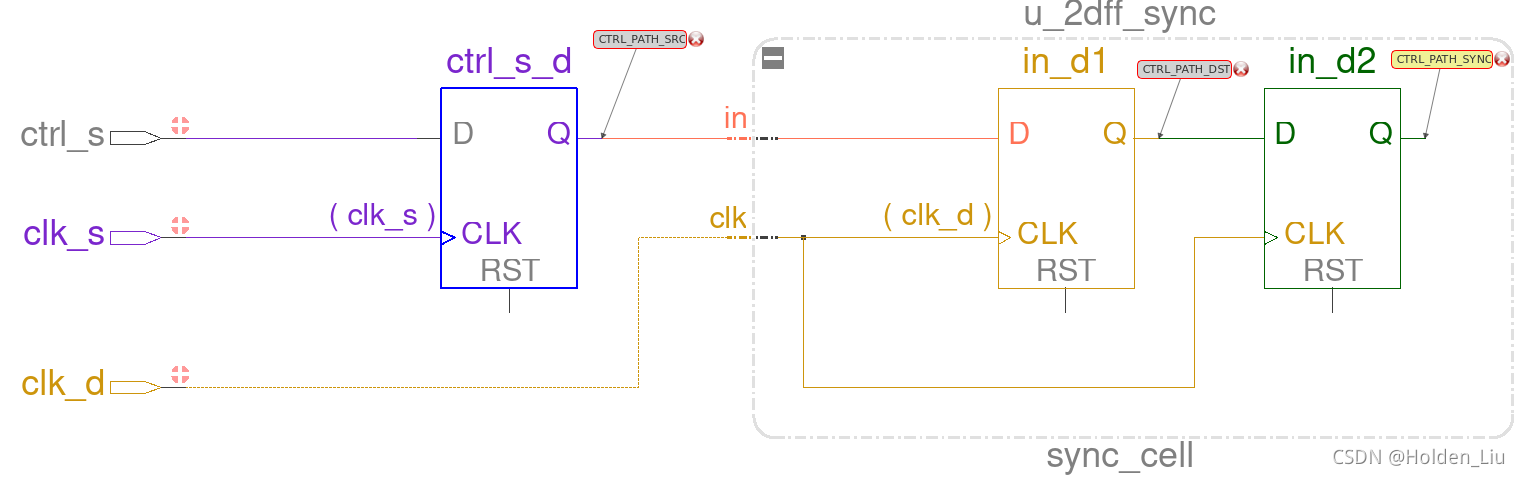

常见的CDC处理方式为使用two-flip-flop作为同步器,第一级dff的Q端出现亚稳态,第二级相同clock的dff采样时,Q端一般为稳定的电平强度。

Note:

-

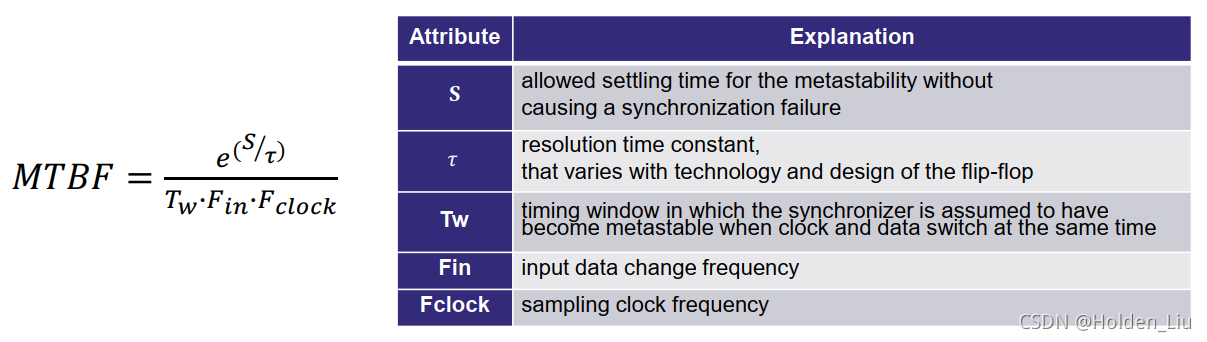

MTBF-mean time before failure 公式评估亚稳态发生的概率(发生两次失效的时间间隔)。时钟频率越高,数据变化频率越高,越容易出现亚稳态。

-

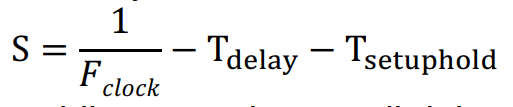

满足

setup/hold time,Q端的输出需要在clock-to-qdelay时间内稳定。在两级同步的策略中,参数S为第2级dff处理亚稳态的时间,Tdelay为第1级dff的clock-to-qdelay + wire delay,Tsetuphold为第2级dff的setuphold time。 对于超高速设计,参数S不够充裕,则可以采用3级dff进行同步处理。

-

跨时钟域的信号,应该在

source domain寄存一拍,再经过destination domain的2级同步处理。因为如果是source domain的组合逻辑直接输出,容易出现glitch,增加亚稳态发生的概率。而同步电路由于时钟约束,若是single cycle path,上级dff的q端经过组合逻辑到达下级dff的d端预期为1个cycle,在这1个cycle中,出现的glitch一般不会影响下级dff的d端采样锁存信号。

-

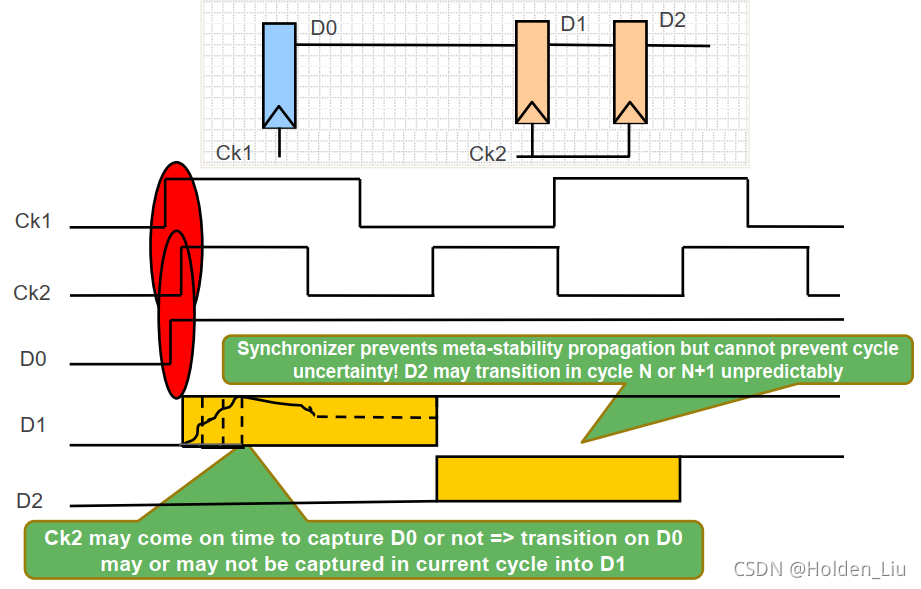

2级dff同步存在

cycle uncertainty的问题;当第2级dff采样第1级dff Q端输出的亚稳态,若采样到1,则latency为1个cycle;采样到0,则latency为2个cycle。至于是N还是N+1,并不确定。

-

CDC中传播的信号一般分为event类型和level类型。event如pulse类型信号,level如static类型信号。这两种类型的处理方式不同,下文具体讲解。

-

VC Spyglass CDC将CDC path分为ctrl path和data path两种。这两种类型的处理方式不同,下文具体讲解。 -

VC Spyglass CDC分为structural verification和 functional verification 两种。下文具体讲解。

Type of CDC Problems

<1> Metastability due to Missing Synchronizer

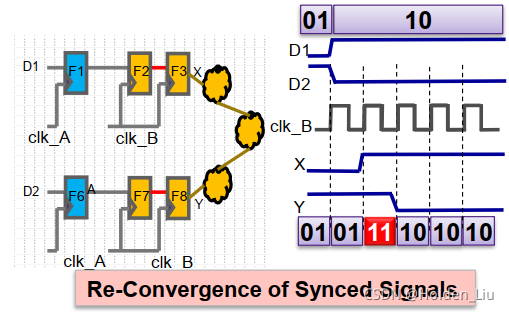

<2> Re-Convergence of Synced Signals

Multi-bit signals 分别经过2-dff同步,然后重聚为一个有效信号,驱动后级组合逻辑。重聚的信号可能会出现一个cycle的非预期值被误采样,影响功能逻辑。

原因可总结为两点:

F1到F2的path delay和F6到F7的 path delay不同,skew的存在导致clk_B采样存在先后顺序。- 就算布线保证skew几乎不存在,

Multi-bit signals在同一时刻发生变化。但是因为2-dff同步存在cycle uncertainty的问题,也会出现一个cycle的不确定值。

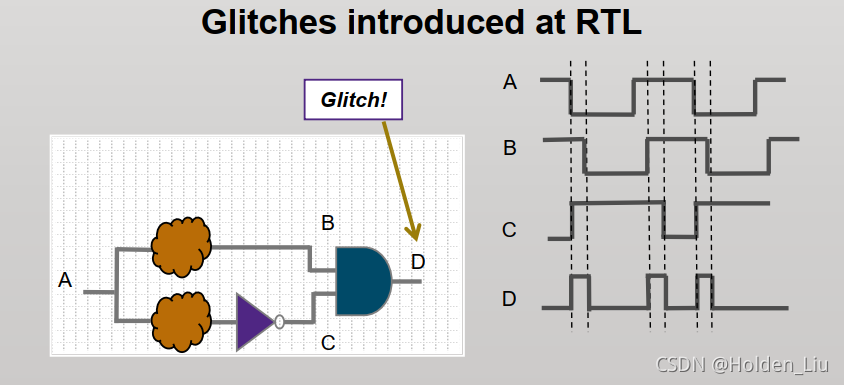

<3> Glitch introduced at RTL

上述source domain的组合逻辑输出 ,容易出现glitch,导致亚稳态的发生。

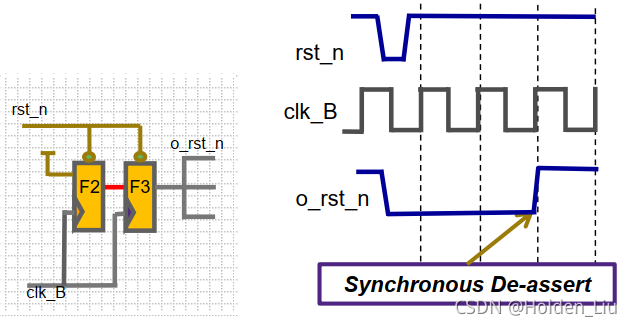

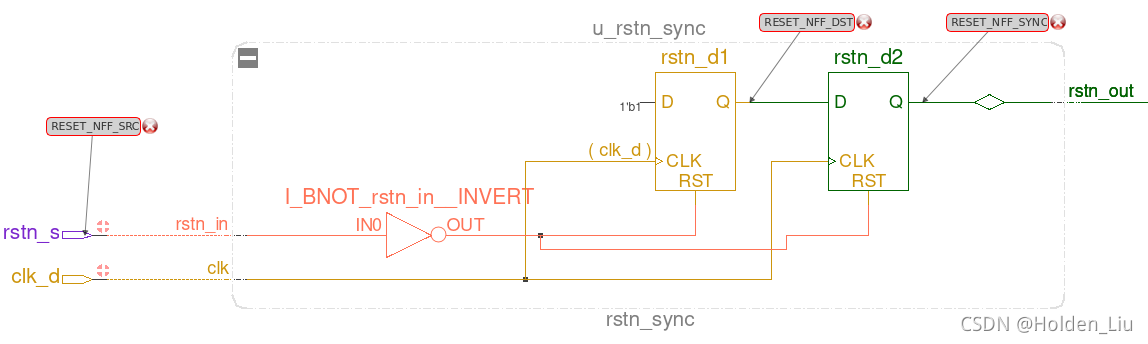

<4> Reset Synchronization

ASIC中一般采用异步复位,同步释放的策略。同步处理的reset信号,后端工具会自动识别,调整路径上的buffer,保证reset信号满足dff的removal time recovery time。未作同步处理的reset信号,在后仿时若removal/recovery违例,出现X态。

reset synchronizer的结构如下:

低电平有效的复位,rstn_d1的D端一直为高电平1。

reset release流程如下:

rstn_sassert时,rstn_d2维持为0,保持后级电路的复位状态。rstn_srelease时,若rstn_d1的removal/recovery违例,Q端出现亚稳态。rstn_d2在1~2个cycle latency后输出为1。rstn_srelease时,若rstn_d1的removal/recovery没有违例,rstn_d2在1个cycle latency后输出为1。

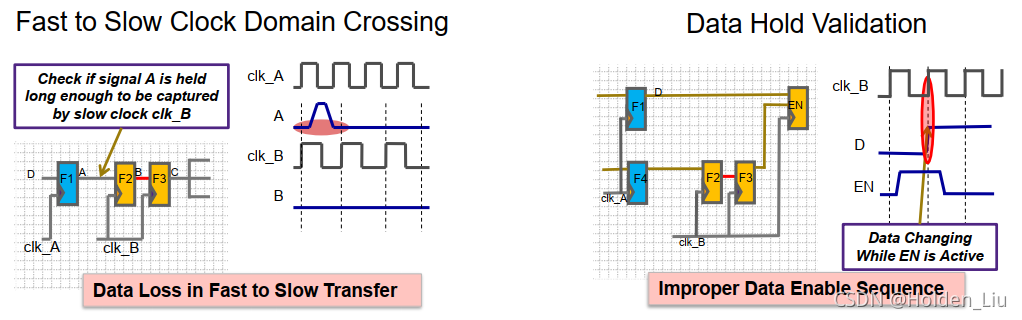

<5> Functional problems

CDC设计的功能部分仅仅使用VC Spyglass CDC的structural verification无法完全覆盖到,还需要functional verification来保证,比如Formal Verification和SVA-Base Verification with simulation。

-

从快时钟域到慢时钟域,信号保持时间过短,慢时钟域采样不到,data loss.

-

EN使能时,data hold而不是data change。

-

Mulit-bit re-convergence时,data coherency问题。(结构上存在re-convergence的问题,但是采用了格雷编码或者下级电路对data coherency有一定容忍度,不会影响逻辑功能)

-

Glitch问题。(结构上会产生glitch的电路,但是组合逻辑的fan-in不是同时变化或者是static的,fan-out就不会产生glitch)

上述四类问题都可以通过VC Spyglass 生成和当前约束条件相对应的SV-assertion,用于simulation。 -

handshak 的流程是否正确

-

第三方CDC标准组件的使用是否满足要求

885

885

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?