CDC check中,在使用blackbox或者abstarct model时需要做抽象模型处理。

VC Spyglass使用一系列attribute命令,可读性更好。

Spyglass使用abstract_port和assume_path。

Description

Note: This document is not writing a SAM (Static Abstract Model). A SAM is an auto-generated, reduced representation of the design that comprises portions of the design, itself, relevant to the type of analysis to be performed at higher levels. This Constraint Abstract Model approach is about writing a model for analysis where the interface is understood but a functional description is not available or does not exist.

You must create two constraint files which describe the boundary information of the model as below. Name of the files must follow given format to read by the tool.

-

translated_validate_.tcl

All input side constraints should be specified in this file. -

translated_verif_.tcl

All output side constraints should be specified in this file.

Then to read the constraint abstract model in user top level setup, following command and application variables should be used before design read commands.

> App_vars:

set_app_var cdc_read_constr_abs_model true

set_app_var cdc_enable_parameterized_abs_models true

Command to read translated abstract modules:

set_constr_abstract_model

Usage:

-module <module_name> - Specifies a module for constraint based abstract model.

[-instances <instance_name>]- Specifies a list of instances for constraint based abstract model.

-path <path_name>- Specifies abstract model directory path which contain the abstraction tcl files.

Example:

> set_app_var cdc_read_constr_abs_model true set_app_var

> cdc_enable_parameterized_abs_models true

> set_constr_abstract_model -path abstraction -module Block

The following are the basic steps to model a port using attribute commands. Detailed examples are mentioned as follows:

Step 1)

Define the scope of the attribute commands using the set_constraints_scope command.

Step 2)

Use the define_attribute command to create a new attribute element with the given name.

Step 3)

Attach the clock/reset/connectivity/sync attributes to the defined attribute name using set_clock_attribute, set_reset_attribute, set_connectivity_attribute or set_sync_attribute commands.

Steps 4)

Use the apply_attribute command to specify the pins to the given attributes.

Step 5)

Use end_constraints_scope command defines the end of the current scope of the attribute commands.

Note: If you are modeling set of ports, no need to use set_constraints_scope and end_constraints_scope for each set_*_attribute. See example 2.

Important: Do not use get_* command to provide design objects to set_*_attribute commands.

Example : set_clock_attribute path1 -clock_objects [get_pins clk1]

EXamples 1)

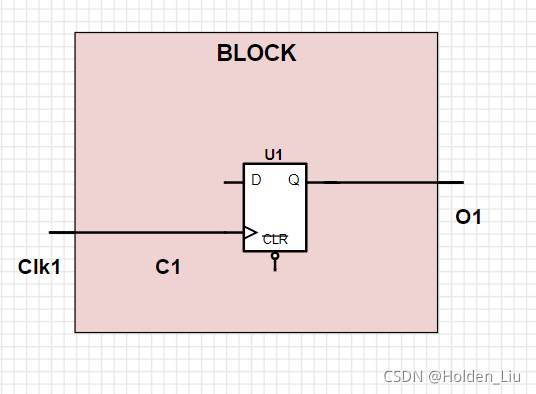

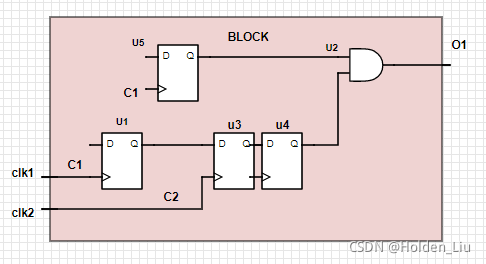

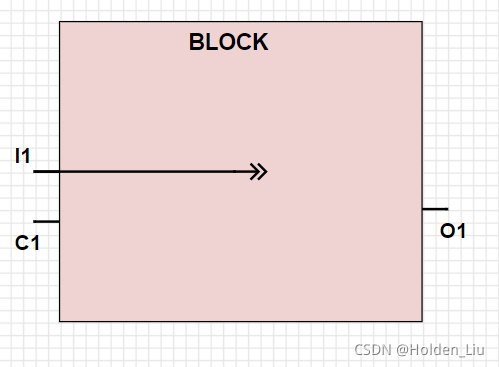

The above example implies that the O1 output port of the BLOCK module is driven by a flip-flop clocked by the clock which comes to Clk1 port. This can be modeled using the following command.

Commands

set_constraints_scope -module BLOCK

define_attribute -name path1

set_clock_attribute path1 -clock_objects Clk1

apply_attribute path1 -objects {O1}

end_constraints_scope

Note: The -direction switch of apply_attribute is not mandatory here. Tool will automatically identify a port’s direction. But if you are modeling an INOUT port, you should add -direction.

Also you must specify a clock objects instead of port/pin objects use -clocks switch in the set_clock_attribute command instead of -clock_objects switch. For example, if virtual clock must be used with the set_clock_attribute.

SpyGlass Command:

abstract_port -module BLOCK -ports O1 -clock C1 -scope cdc

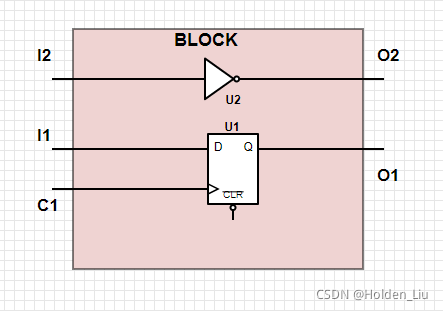

Examples 2)

The above example implies that the O1 output port of the BLOCK module is driven by a flip-flop clocked by the clocks reaching C1 port and driven by the data reaching I1 port. (As example, consider a qualifier which is propagating through an abstract module within the sequential depth ) It also includes an inverter path from I2 to O2. This can be modeled using the following commands.

Commands:

set_constraints_scope -module {BLOCK}

define_attribute -name path1 -objects {O1}

set_clock_attribute path1 -clock_objects {C1}

set_connectivity_attribute path1 -path_type seq -related_ports {I1}

define_attribute -name path2

set_connectivity_attribute path2 -path_type inv -related_ports {I2}

apply_attribute path2 -add -objects {O2}

end_constraints_scope

SpyGlass Command:

abstract_port -module BLOCK -ports O1 -clock C1 -related_ports I1 -scope cdc

abstract_port -module BLOCK -path_logic inv -ports O2 -related_ports I2 -scope cdc

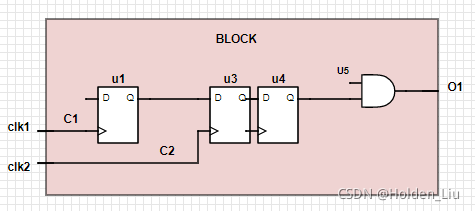

Example 3)

The above example implies that the O1 port of the BLOCK module is an output of a control synchronizer (from the source clock C1 which is reaching through clk1 pin to the destination clock C2 which is reaching through clk2 pin ) and there is combinational logic present between the synchronizer and the port. This can be modeled using the following commands.

Commands:

set_constraints_scope -module {BLOCK}

define_attribute -name path1

set_sync_attribute path1 -sync active -from {clk1} -to {clk2} -sync_names {u4/Q} -combo yes

apply_attribute path1 -objects {O1}

end_constraints_scope

Note: For the -from/to switches you can use both clock objects and port/pin objects as well. For example, If virtual clock need to be specified, it can be directly use virtual clock names.

Also, see the example 4 which describe the usage of -sync_names switch of set_sync_attribute.

SpyGlass Command:

abstract_port -module BLOCK -ports O1 -clock clk2 -combo yes -sync active -from clk1 -to clk2 -sync_names BLOCK.u4.Q -scope cdc

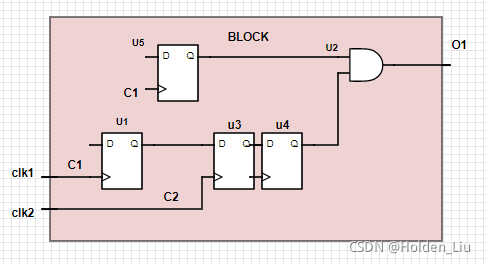

Example 4)

The above example implies that the O1 and O2 ports of the BLOCK module are an connected to the same control synchronizer (from the source clock C1 which is reaching through clk1 pin to the destination clock C2 which is reaching through clk2 pin). O1 and O2 ports converge at the top level U5 AND gate. To specify same control synchronizer is coming out from O1 and O2 -sync_names can be used. Then no coherency issue will be reported.

Commands:

set_constraints_scope -module {BLOCK}

define_attribute -name path1

set_sync_attribute path1 -sync active -from {clk1} -to {clk2} -sync_names {u4/Q} -combo yes

apply_attribute path1 -objects {O1}

define_attribute -name path2

set_sync_attribute path2 -sync active -from {clk1} -to {clk2} -sync_names {u4/Q} -combo no

apply_attribute path2 -objects {O2}

end_constraints_scope

Note: You can use any string with -sync_names to name a control synchronizer which is inside an abstraction.

SpyGlass Command:

abstract_port -module BLOCK -ports O1 -clock clk2 -combo yes -sync active -from clk1 -to clk2 -sync_names BLOCK.u4.Q -scope cdc

abstract_port -module BLOCK -ports O2 -clock clk2 -combo no -sync active -from clk1 -to clk2 -sync_names BLOCK.u4.Q -scope cdc

Example 5)

This is an example of a data crossing from C1 domain that is synchronized in C2 domain by a qualifier and gating logic. Note that output port O1 must ultimately reach a flop in C2 domain or synchronization of this modeled data crossing will fail and O1 cannot use to synchronize other data crossings.

Command:

set_constraints_scope -module {BLOCK}

define_attribute -name path1

set_sync_attribute path1 -sync inactive -from {clk1} -to {clk2} -combo no -sync_names {u4/Q}

apply_attribute path1 -objects {O1}

end_constraints_scope

SpyGlass Command:

abstract_port -module BLOCK -ports O1 -clock clk2 -combo no -sync inactive -from clk1 -to clk2 -scope cdc -sync_names BLOCK.u4.Q

Example 6)

The above example implies that all the fan-out of the I1 input port are hanging. This can be modeled using the following command.

Command:

set_constraints_scope -module {BLOCK}

define_attribute -name path1

set_ignore_attribute path1

apply_attribute path1 -add -objects {I1}

end_constraints_scope

SpyGlass Command:

abstract_port -module BLOCK -ports I1 -ignore

Example 7)

The above example implies that the I1 input port of the BLOCK module drives a flip-flop clocked by the clock receiving to C1 pin and the reset receiving to RST pin. This can be modeled using below command.

Commands:

set_constraints_scope -module BLOCK

define_attribute -name path1

set_clock_attribute path1 -clock_objects C1

set_reset_attribute path1 -reset_objects RST

apply_attribute path1 -objects {I1}

end_constraints_scope

SpyGlass Command:

abstract_port -module BLOCK -ports I1 -clock C1 -reset RST -scope cdc

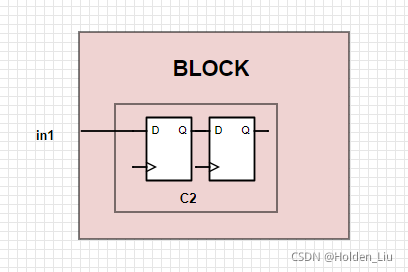

Example 8)

The above example implies that the in1 input port of the BLOCK module drives a drives a synchronizer clocked by the clock C2.

Commands

create_clock -name {SG_VCLK1} -period 10

set_constraints_scope -module BLOCK

define_attribute -name path1

set_clock_attribute path1 -clocks {SG_VCLK1} -combo no -combo_ifn {C2}

apply_attribute vc_path1 -objects {in1}

end_constraints_scope

set_clock_group -asynchronous -group { SG_VCLK1 }

SpyGlass Command:

abstract_port -module BLOCK -clock SG_VCLK1 -combo no -ports "in1" -combo_ifn c2

本文详细介绍了在CDCcheck中使用blackbox或abstarctmodel进行抽象模型处理的步骤,以及VCSpyglass如何通过attribute命令进行可读性更好的约束分析。具体操作涉及translated_validate_.tcl和translated_verif_.tcl两个文件,用于定义输入和输出侧约束。同时,文章列举了多个实例,展示了如何使用set_clock_attribute、set_reset_attribute、set_connectivity_attribute和set_sync_attribute等命令来创建和应用属性,以及如何使用abstract_port命令进行SpyGlass建模。这些方法对于理解和实现设计的高级别分析至关重要。

本文详细介绍了在CDCcheck中使用blackbox或abstarctmodel进行抽象模型处理的步骤,以及VCSpyglass如何通过attribute命令进行可读性更好的约束分析。具体操作涉及translated_validate_.tcl和translated_verif_.tcl两个文件,用于定义输入和输出侧约束。同时,文章列举了多个实例,展示了如何使用set_clock_attribute、set_reset_attribute、set_connectivity_attribute和set_sync_attribute等命令来创建和应用属性,以及如何使用abstract_port命令进行SpyGlass建模。这些方法对于理解和实现设计的高级别分析至关重要。

2235

2235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?