PCI/PCIe配置空间(Configuration Space)

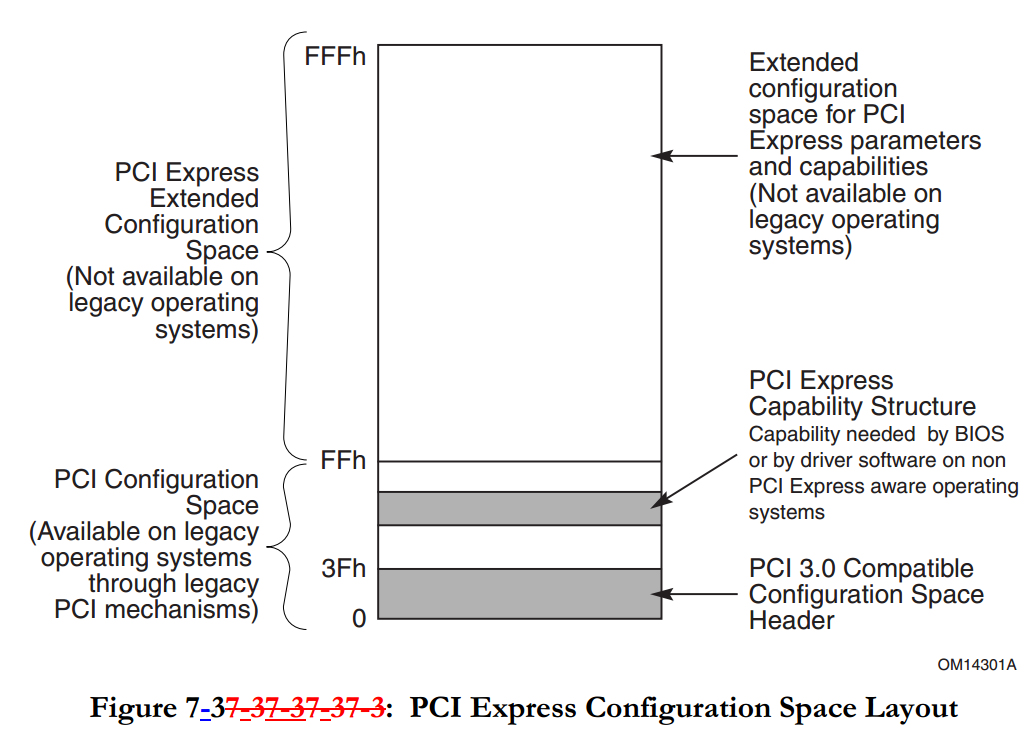

PCI/PCIe的配置空间Configuration Space是一个与Memory空间和IO空间并列的独立的空间。

- 对Legacy PCI来讲,

Configuration Space有256 Bytes - 对于PCIe,

Configuration Space有4096 Bytes

访问方式

对于x86架构的CPU而言,有定义Memory和IO的指令,但没有配置空间相关的指令。所以需要有一个译码器把配置命令翻译一下,这个译码器一般是在北桥里面,现在Intel的CPU已经自动集成北桥,从而CPU可以直接完成翻译工作。具本而言,有以下两种方式可以完成对配置空间的访问。

- IO方式(CF8h/CFCh)

- Memory方式(ECAM)

IO方式

CPU提供了两组I/O寄存器用于访问配置空间:

- 配置空间控制寄存器 CF8h-CFBh

- 配置空间数据寄存器 CFCh-CFFh

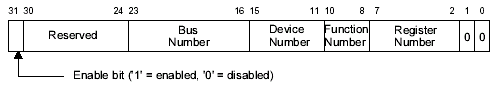

控制寄存器是一个32 bit的寄存器,其定义如下:

所以用I/O方式访问PCI/PCIe的寄存器代码如下:

// for PCI

address = BIT31 | ((Bus & 0xFF) << 16) | ((Dev & 0x1F) << 11) | ((Fun & 0x7) << 8) | (Reg & 0xfffffffc);

// write cfg register

IoWrite8(0xcf8, address);

// read data register

data8 = IoRead8(0xcfc);

data16 = IoRead16(0xcfc);

data32 = IoRead32(0xcfc);- 以上的代码适用于PCI和PCIe寄存器的访问,对于PCIe而言,I/O方式只能访问前256个寄存器。

- Bit31代表enable bit。一定要置起来,否则不起作用。

Memory方式(ECAM)

Memory方式访问PCI/PCIe配置空间需要知道MMCFG的基本地址。这个地址是由BIOS program到mmcfg_base寄存器中的。从ECAM中获取PCI/PCIe的寄存器同直接访问内存没有太大的区别,对于c语言,用指针很容易访问。

#define pcie_addr(m, b, d, f, o) (m + ((b & 0xff) << 20) + ((d & 0x1f) << 15) + ((f & 0x7) << 12) + (o & 0xfffffffc)

#define mmio_read8(addr) (*(volatile uint8 *)addr)

#define mmio_write8(addr, data8) *(volatile uint8 *)addr = data8

#define mmio_read16(addr) (*(volatile uint16 *)addr)

#define mmio_write16(addr, data16) *(volatile uint16 *)addr = data16

#define mmio_read32(addr) (*(volatile uint32 *)addr)

#define mmio_write32(addr, data32) *(volatile uint32 *)addr = data32

1405

1405

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?