针对micron spi flash

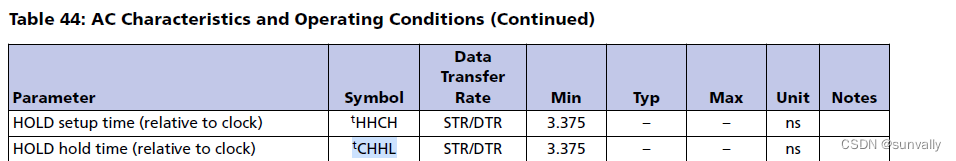

HOLD时序参数

在svt_spi_flash_base_virtual_sequence中存在

/** It specifies sclk edge to hold deassert delay */

rand int flash_sclk_to_hold_deassert = 1'b1;

/** It specifies SCLK edge (specified by #flash_assert_hold_after_sclk_count) to hold assert delay (tCHHL) */

rand int flash_sclk_to_hold_assert = 1'b1;

对应美光spi flash的HOLD时序图如下:

其中的tCHHL和tHHCH的时序参数说明如下:

svt_spi_transaction

address_frame_size

address_frame_size是类svt_spi_transaction中成员变量,用来指示address phase时的地址bit数。

/**

* @groupname spi_trans_std, spi_trans_flash, spi_trans_xSPI

* This field specifies the number of bits in Address phase. <br/>

* This is valid only when either frame_format is set to SPI_MULTILANE/SPI_FLASH or <br/>

* frame_format is set to SPI_STD with transfer_mode is set to EEPROM_READ or <br/>

* frame_format is set to SPI_STD with enable_mem_core set.

*/

rand int address_frame_size = 24;

xip_confirmation_n

/**

* @groupname spi_trans_flash, spi_trans_xSPI

* This field specifies XIP confirmation bit/continuous read mode value to be used during wait phase <br/>

* for FAST Read commands when XIP mode is enabled. <br/>

* For Vendor Micron,only LSB of this bitvector is valid. <br/>

* For Vendor Winbond, MSB[7:4] of the bitvector specifies the upper 4 bits of continuous read mode.

*/

rand bit[7:0] xip_confirmation_n = 8'b1;

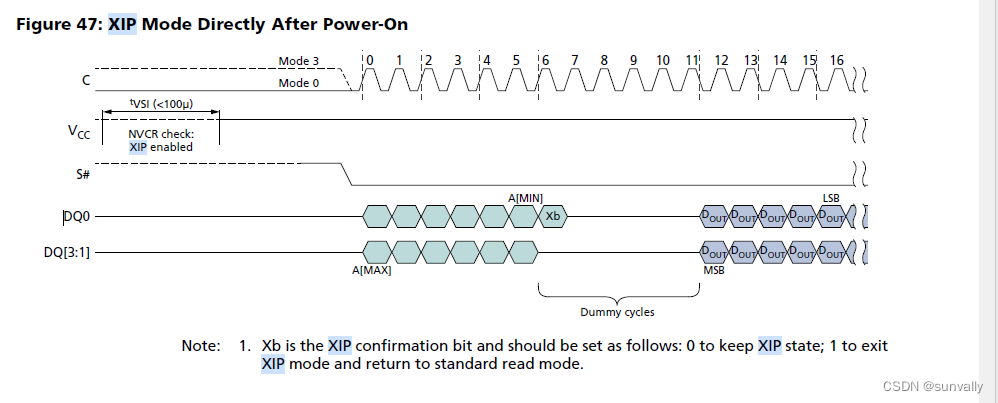

XIP Mode

Execute-in-place (XIP) mode allows the memory to be read by sending an address to the device and then receiving the data on one, two, or four pins in parallel, depending on the customer requirements. XIP mode offers maximum flexibility to the application, saves instruction overhead, and reduces random access time.

Activate and Terminate XIP Using Volatile Configuration Register

Applications that boot in SPI and must switch to XIP use the volatile configuration register. XIP provides faster memory READ operations by requiring only an address to execute, rather than a command code and an address.

To activate XIP requires two steps. First, enable XIP by setting volatile configuration register bit 3 to 0. Next, drive the XIP confirmation bit to 0 during the next FAST READ operation. XIP is then active. Once in XIP, any command that occurs after S# is toggled requires only address bits to execute; a command code is not necessary, and device operations use the SPI protocol that is enabled. XIP is terminated by driving the XIP confirmation bit to 1. The device automatically resets volatile configuration register bit 3 to 1.

Activate and Terminate XIP Using Nonvolatile Configuration Register

Applications that must boot directly in XIP use the nonvolatile configuration register. To enable a device to power-up in XIP using this register, set nonvolatile configuration register bits [11:9]. Settings vary according to protocol, as explained in the Nonvolatile

Configuration Register section. Because the device boots directly in XIP, after the power cycle, no command code is necessary. XIP is terminated by driving the XIP confirmation bit to 1.

796

796

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?